| m |  |

Assistant Professor, Texas A&M University Department of Electrical & Computer Engineering |

m |  |

| mHOME | mRESEARCH | mTEACHING | mPUBLICATIONS | mCONTACT |

|

ADC-Based Serial Links Project Description

The ADC-based high-speed serial link architectures and design techniques under development in this project aim to significantly improve interconnect energy efficiency and bandwidth density, which is necessary for continued scaling of future compute systems. The research goals are to develop high-performance energy-efficient ADC-based high-speed serial link architectures applicable to future computing systems. To accomplish this goal, research objectives are: (1) develop a novel statistical-modeling framework for designing advanced ADC-based high-speed serial links; (2) develop, implement, and test a CMOS prototype of an energy-efficient transmitter architecture capable of scaling data rate and modulation format based on system performance demands; (3) develop, implement, and test a new hybrid ADC-based receiver architecture which combines in a power optimum manner equalization embedded in the ADC and dynamically power-gated digital equalization based on threshold detection.

Publications

S. Cai, E. Zhian Tabasy, A. Shafik, S. Kiran, S. Hoyos, and S. Palermo, "A 25GS/s 6b TI Binary Search ADC with Soft-Decision Selection in 65nm CMOS," submitted to 2015 IEEE Symposium on VLSI Circuits.

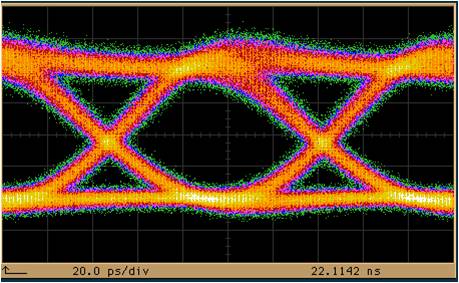

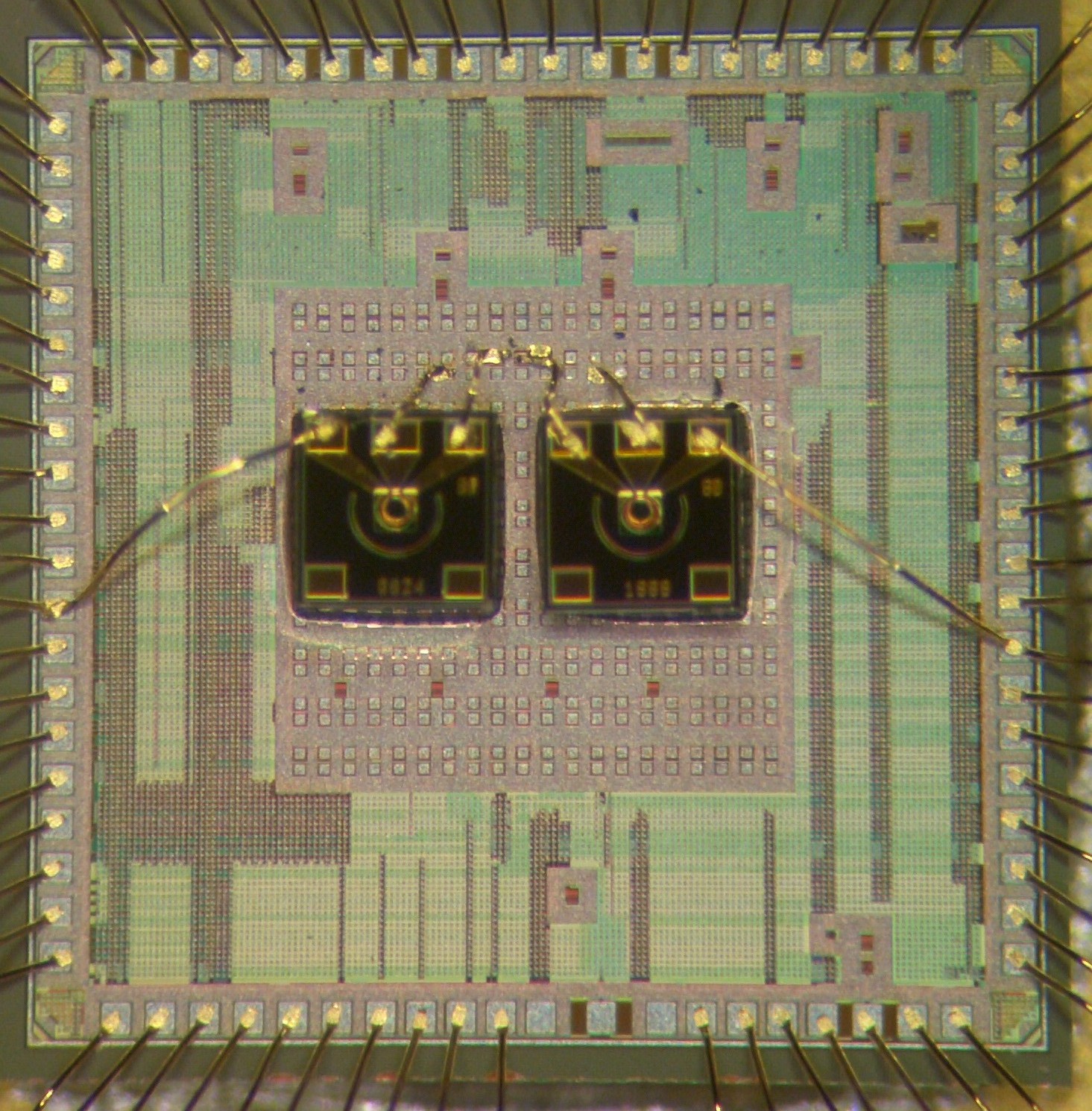

A. Shafik, E. Zhian Tabasy, S. Cai, K. Lee, S. Hoyos, and S. Palermo, "A 10Gb/s Hybrid ADC-Based Receiver with Embedded 3-Tap Analog FFE and Dynamically-Enabled Digital Equalization in 65nm CMOS," accepted in 2015 International Solid-State Circuits Conference.

E. Zhian Tabasy, A. Shafik, K. Lee, S. Hoyos, and S. Palermo, "A 6b 10GS/s TI-SAR ADC with Low-Overhead Embedded FFE/DFE Equalization for Wireline Receiver Applications," IEEE Journal of Solid-State Circuits, Nov. 2014.

S. Cai, A. Shafik, S. Kiran, E. Zhian Tabasy, S. Hoyos, and S. Palermo, "Statistical Modeling of Metastability in ADC-Based Serial I/O Receivers," IEEE Conference on Electrical Performance of Electronic Packaging and Systems, Oct. 2014.

B. Min, N. H.-W. Yang, and S. Palermo, "10Gb/s Adaptive Receive-Side Near-End and Far-End Crosstalk Cancellation Circuitry," IEEE International Midwest Symposium on Circuits and Systems, Aug. 2014.[Best Student Paper Award].

E. Zhian Tabasy, A. Shafik, S. Huang, N. Yang, S. Hoyos, and S. Palermo, "A 6b 1.6GS/s ADC with Redundant Cycle 1-Tap Embedded DFE in 90nm CMOS," IEEE Journal of Solid-State Circuits, Aug. 2013.

|

m | |