## Chapter 7

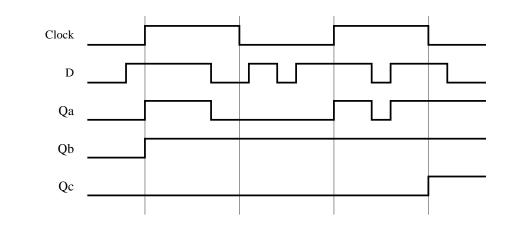

7.1.

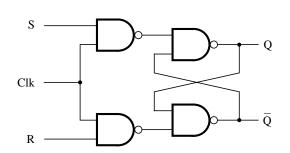

- 7.2. The circuit in Figure 7.3 can be modified to implement an SR latch by connecting S to the *Data* input and S + R to the *Load* input. Thus the value of S is loaded into the latch whenever either S or R is asserted. Care must be taken to ensure that the *Data* signal remains stable while the *Load* signal is asserted.

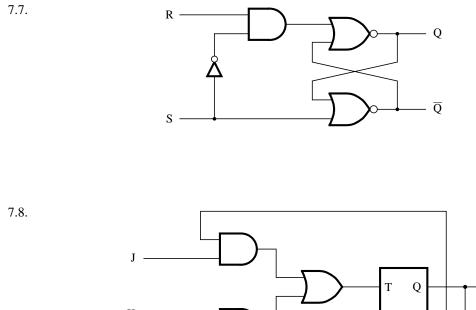

- 7.3.  $\overline{R}$  .  $\overline{S} = \overline{R}$  $Q_a \quad Q_b$  $Q_b$ 0/1 1/0 (no change) 1 1 1 0 0 1 0 1 0 1  $Q_a$ 0 0 1 1  $\overline{S}$  .

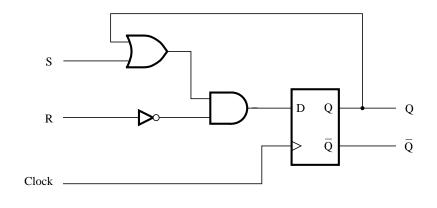

7.4.

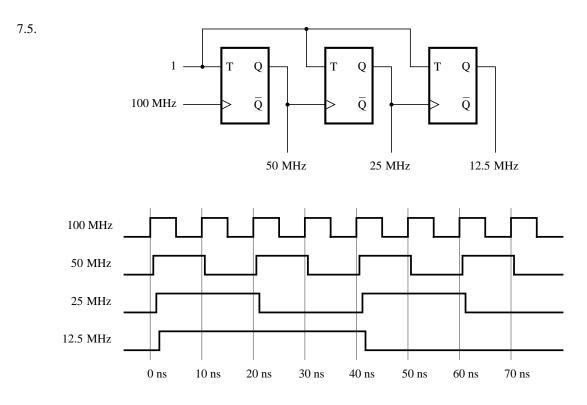

7.6.

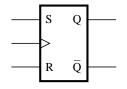

| S | R | Q(t + 1) |

|---|---|----------|

| 0 | 0 | Q(t)     |

| 0 | 1 | 0        |

| 1 | 0 | 1        |

| 1 | 1 | 0        |

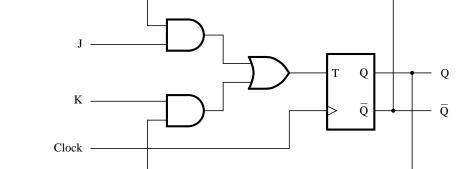

7.9. This circuit acts as a negative-edge-triggered JK flip-flop, in which J = A, K = B, Clock = C, Q = D, and  $\overline{Q} = E$ . This circuit is found in the standard chip called 74LS107A (plus a *Clear* input, which is not shown).

## **Chapter 8**

8.1. The expressions for the inputs of the flip-flops are

$$D_2 = Y_2 = \overline{w}y_2 + \overline{y}_1\overline{y}_2$$

$$D_1 = Y_1 = w \oplus y_1 \oplus y_2$$

The output equation is

$z = y_1 y_2$

8.2. The excitation table for JK flip-flops is

| Present  |          |          |          |          |        |

|----------|----------|----------|----------|----------|--------|

| state    | w = 0    |          | w = 1    |          | Output |

| $y_2y_1$ | $J_2K_2$ | $J_1K_1$ | $J_2K_2$ | $J_1K_1$ | z      |

| 00       | 1d       | 0d       | 1d       | 1d       | 0      |

| 01       | 0d       | d0       | 0d       | d1       | 0      |

| 10       | d0       | 1d       | d1       | 0d       | 0      |

| 11       | d0       | d1       | d1       | d0       | 1      |

The expressions for the inputs of the flip-flops are

$$J_2 = \overline{y}_1$$

$$K_2 = w$$

$$J_1 = \overline{w}y_2 + w\overline{y}_2$$

$$K_1 = J_1$$

The output equation is

$$z = y_1 y_2$$

8.3. A possible state table is

| Present | Next  | state | Output z |       |

|---------|-------|-------|----------|-------|

| state   | w = 0 | w = 1 | w = 0    | w = 1 |

| А       | А     | В     | 0        | 0     |

| В       | Е     | С     | 0        | 0     |

| С       | Е     | D     | 0        | 0     |

| D       | Е     | D     | 0        | 1     |

| Е       | F     | В     | 0        | 0     |

| F       | А     | В     | 0        | 1     |