# Simulation and Analysis of Random Decision Errors in Clocked Comparators

Jaeha Kim, Member, IEEE, Brian S. Leibowitz, Member, IEEE, Jihong Ren, Member, IEEE, and Chris J. Madden, Member, IEEE

Abstract-Clocked comparators have found widespread use in noise sensitive applications including analog-to-digital converters, wireline receivers, and memory bit-line detectors. However, their nonlinear, time-varying dynamics resulting in discrete output levels have discouraged the use of traditional linear time-invariant (LTI) small-signal analysis and noise simulation techniques. This paper describes a linear, time-varying (LTV) model of clock comparators that can accurately predict the decision error probability without resorting to more general stochastic system models. The LTV analysis framework in conjunction with the linear, periodically time-varying (LPTV) simulation algorithms available from RF circuit simulators can provide insights into the intrinsic sampling and decision operations of clock comparators and the major contribution sources to random decision errors. Two comparators are simulated and compared with laboratory measurements. A 90-nm CMOS comparator is measured to have an equivalent input-referred random noise of 0.73 mVrms for dc inputs, matching simulation results with a short channel excess noise factor  $\gamma = 2$ .

*Index Terms*—Circuit analysis, circuit noise, circuit simulation, comparators.

#### I. INTRODUCTION

CLOCKED comparator is a circuit element that makes A decision as to whether the input signal is high or low at every clock cycle. It has found widespread use in applications where digital information needs to be recovered from analog signals, such as analog-to-digital (A/D) converters, wireline receivers, and memory bit-line detectors. To ensure correct detection on each comparison, the analog input must have sufficient magnitude to overcome deterministic errors such as offset and hysteresis, as well as random errors due to device thermal noise and flicker noise. In the past, circuit designers have focused more on the deterministic errors that are related to integral and differential nonlinearities in A/D converters, for instance. However, the supply voltage scaling in CMOS technologies and the increasing demand for low power consumption have effectively led to the reduction in the signal power while the random noises in the circuits have become worse due to the degradation

B. S. Leibowitz, J. Ren, and C. J. Madden are with the Rambus, Inc., Los Altos, CA 94022 USA (e-mail: brianl@rambus.com; jren@rambus.com; cmadden@rambus.com).

Digital Object Identifier 10.1109/TCSI.2009.2028449

in the device transconductance  $(g_m)$ . As a result, the random noises have become a significant source of decision errors for clocked comparators and must be properly addressed during the design phase. This paper describes a framework based on linear time-varying system theories [1], [2] that can accurately analyze and simulate the random decision error probabilities in clocked comparators.

While a comparator is by definition a nonlinear circuit element that makes a hard decision on the input signal polarity, almost every clocked comparator does so by sampling the input signal and then regeneratively amplifying it, each of which operation can be treated as that of a linear system. The key difference with traditional linear circuits such as amplifiers is that the comparator may have different linear behaviors at different time points; in other words, it is a linear, but time-varying (LTV) system. While this property precludes the use of the linear time-invariant (LTI) system theory or the traditional small-signal analysis framework for estimating the noise effects in clocked comparators, we will find that their simple extensions to time-varying systems can provide all the necessary insights to design a good comparator with low random decision error rates.

Most comparators are triggered by periodic clocks and therefore can be treated as *linear*, *periodically time-varying* (LPTV) systems, which mend themselves well to the periodic simulation framework of RF circuit simulators including SpectreRF and ADS. These periodic simulation techniques have been primarily used for RF circuits such as LNAs, mixers, and oscillators [3]–[6]. Once we realize that a comparator can be viewed as an LPTV system, these mature simulation techniques can be leveraged in characterizing its sampling and regeneration processes as well as estimating the contributions from various noise sources during the decision process.

Note that random decision errors are different from metastability failures, which have been extensively studied in literature [8]. While metastability failure refers to a situation where the comparator cannot make a firm decision within a given period of time due to insufficient input swing, a random decision error in this paper refers to a situation where the comparator makes a decision, but the decision is incorrect due to excessive random noise.

This paper presents analysis and simulation methodologies for characterizing the random decision error probabilities in clock comparators based on an LPTV system model. The paper is organized as follows. First, it introduces the LTV system theory and describes the LTV model for clocked comparators that is found instrumental in characterizing the sampling

Manuscript received March 21, 2009; revised June 16, 2009. First published July 28, 2009; current version published August 21, 2009. This paper was recommended by Guest Editor S. Mirabbasi.

J. Kim was with the Rambus, Inc., Los Altos, CA 94022, USA. He is now with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: jaeha@ieee.org).

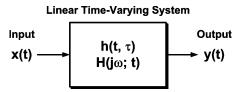

Fig. 1. LTV system is characterized either with time-varying impulse response  $h(t, \tau)$  or with time-varying transfer function  $H(j\omega; t)$ .

aperture and regeneration gain [11], [12] as well as estimating the decision error probability or the equivalent input-referred noise [14], [15]. Second, it demonstrates the application of the LTV system analysis framework to a representative clocked comparator example from [7]. Then, it outlines the procedure of simulating the clocked comparator responses with RF simulator analyses such as periodic steady-state (PSS) and periodic noise (PNOISE). Finally, the simulation results are compared to laboratory measurements to validate the methodology.

# II. LINEAR, TIME-VARYING SYSTEM MODEL FOR CLOCKED COMPARATORS

# A. Linear Time-Varying System Theory

This sub-section reviews the LTV system theory [1], [2] and lists a few key equations governing the signal and noise responses of LTV systems.

An LTV system is a dynamical system for which the superposition principle holds but the time-invariant property does not. In other words, if  $y_1(t)$  and  $y_2(t)$  are the time-domain responses of an LTV system to the input stimuli  $x_1(t)$  and  $x_2(t)$ , respectively, then the response to a linearly combined input  $a \cdot x_1(t) + b \cdot x_2(t)$  is equal to the linearly combined output  $a \cdot y_1(t) + b \cdot y_2(t)$ , where a and b are real numbers. However, the response to a time-shifted input  $x_1(t-t_0)$  may not be equal to the time-shifted output  $y_1(t-t_0)$ .

For such an LTV system depicted in Fig. 1, one can define a *time-varying impulse response*,  $h(t, \tau)$ , which describes the system response at time t to an impulse arriving at time  $\tau$ . Since the superposition principle still holds for an LTV system, the output of the system y(t) can be related to the input x(t) via an integral expression

$$y(t) = \int_{-\infty}^{\infty} h(t,\tau) \cdot x(\tau) d\tau.$$

(1)

Note that for an LTI system, the time-varying impulse response  $h(t,\tau)$  reduces to the time-invariant impulse response  $h(t-\tau)$  since the response depends only on the time difference between the observation time t and the impulse arrival time  $\tau$ . The above equation then corresponds to a convolution between h(t) and x(t) as expected.

As with LTI systems, an LTV system can be described in frequency domain. If  $X(j\omega)$  is the Fourier transform of the input signal x(t), i.e.,

$$X(j\omega) = \int_{-\infty}^{\infty} x(t) \cdot \exp(-j\omega t) dt$$

<sup>(2)</sup>

$$x(t) = \frac{1}{2\pi} \int_{-\infty}^{\infty} X(j\omega) \cdot \exp(j\omega t) d\omega$$

(3)

then substituting (2) in (1) yields

$$y(t) = \int_{-\infty}^{\infty} h(t,\tau) \times \left[ \frac{1}{2\pi} \int_{-\infty}^{\infty} X(j\omega) \cdot \exp(j\omega\tau) d\omega \right] d\tau$$

$$= \frac{1}{2\pi} \int_{-\infty}^{\infty} X(j\omega) \times \left[ \int_{-\infty}^{\infty} h(t,\tau) \cdot \exp(j\omega\tau) d\tau \right] d\omega.$$

(4)

The time-varying transfer function  $H(j\omega; t)$  is defined as the Fourier transform of the time-varying impulse response [1], that is

$$H(j\omega;t) = \int_{-\infty}^{\infty} h(t,\tau) \cdot \exp(-j\omega(t-\tau))d\tau.$$

(5)

Again, for LTI systems, the above expression reduces to the time-invariant transfer function,  $H(j\omega)$ , since  $h(t,\tau) = h(t - \tau)$ .

Combining (4) and (5) yields the frequency-domain equation governing the input and output of a LTV system

$$Y(j\omega) \cdot \exp(j\omega t) = H(j\omega; t) \cdot X(j\omega) \cdot \exp(j\omega t).$$

(6)

For example, if the input is a single-tone sinusoid,  $x(t) = \exp(j\omega_0 t)$ , (6) says that the output y(t) is  $H(j\omega_0; t) \cdot \exp(j\omega_0 t)$ . The dependency of  $H(j\omega_0; t)$  on the time variable t implies that the system response to a time-shifted input,  $x^*(t) = x(t - t_0) = \exp(j\omega_0(t - t_0))$  may not be equal to the time-shifted version of the original output, i.e.,  $y^*(t) = H(j\omega_0; t) \cdot \exp(j\omega_0(t - t_0)) \neq y(t - t_0)$ .

If the input x(t) is a noise process instead of a signal, the output of the LTV system is a time-varying noise process in general. In a special case of a LPTV system, in which  $h(t, \tau) =$  $h(t + T, \tau + T)$  and  $H(j\omega;t) = H(j\omega;t + T)$  are satisfied for a nonzero real T, the output of the system is a cyclo-stationary noise process [4]. The general expression for the resulting cyclo-stationary noise is somewhat involved, one form of which is a summation of stationary noise processes each scaled by the Fourier series coefficients of the periodically timevarying transfer function  $H(j\omega;t)$ . However, in most circuit applications, designers need not know the full statistics of the time-varying noise process. For example, in mixers, only the noise at the vicinity of the carrier frequency is of concern and therefore the simpler expression can be used [6].

As we will see in later sections, in the case of estimating the probability of random decision errors, we are interested only in the noise statistics measured at a certain time point  $t_0$ . We will later refer to it as the observation time point  $t_{obs}$  and discuss how we determine it for a given comparator. For now, if we assume that we know the time point  $t_0$  at which we will measure the variance of the noise y(t) at the output of the LTV system as a result of the input noise x(t), we can derive the following expression for the variance  $\sigma_y^2(t_0)$ :

$$\sigma_y^2(t_0) = \mathbf{E}[y^2(t_0)]$$

=  $\mathbf{E}\left[\left(\int_{-\infty}^{\infty} h(t_0, u) \cdot x(u) du\right) \cdot \left(\int_{-\infty}^{\infty} h(t_0, v) \cdot x(v) dv\right)\right]$

=  $\int_{-\infty}^{\infty} \int_{-\infty}^{\infty} \mathbf{E}[x(u) \cdot x(v)] \cdot h(t_0, u) \cdot h(t_0, v) du dv$

Authorized licensed use limited to: Texas A M University. Downloaded on February 25,2010 at 13:20:01 EST from IEEE Xplore. Restrictions apply.

$$= \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} R_{xx}(u,v) \cdot h(t_0,u) \cdot h(t_0,v) du dv$$

(7)

where  $R_{xx}(u, v)$  is the auto-correlation function of the input noise process x(t) and we have assumed that the input noise process x(t) has a zero mean without loss of generality. The readers might notice that the expression (7) resembles that of the auto-correlation function of the output noise of an LTI system. In fact, we can treat this LPTV system as an LTI system with an effective impulse response  $h^*(\zeta) = h(t_0, t_0 - \zeta)$  except with a restriction that its output is valid only at  $t = t_0$ . One can derive a frequency-domain expression that relates the power spectral density functions of the input and output noise processes via an effective transfer function  $H^*(j\omega)$  which is the Fourier transform of  $h^*(t)$ .

In a special case when the input x(t) is a white noise with the variance equal to  $\sigma_x^2$ , that is,  $R_{xx}(\tau) = \sigma_x^2 \cdot \delta(\tau)$ , a simpler expression for  $\sigma_y^2(t_0)$  can be derived

$$\sigma_y^2(t_0) = \sigma_x^2 \cdot \int_{-\infty}^{\infty} h^2(t_0, u) du = \sigma_x^2 \cdot \int_{-\infty}^{\infty} \Gamma^2(u) du \equiv \sigma_x^2 \cdot \Gamma_{\rm rms}^2.$$

(8)

A simple example of time-varying noise process is a Wiener process which is an integral of a white Gaussian noise process over a time interval  $[0, \Delta T]$ . Equation (8) suggests that the variance of the Wiener process should increase linearly with the interval width  $\Delta T$  (i.e., the standard deviation increases with  $\sqrt{\Delta T}$ ), which matches with the standard results.

On the other hand, if the input is a flicker noise, i.e.,  $R_{xx}(\tau) = \sigma_x^2$ , the expression for  $\sigma_y^2(t_0)$  becomes

$$\sigma_y^2(t_0) = \sigma_x^2 \cdot \left[ \int_{-\infty}^{\infty} h(t_0, u) du \right]^2$$

$$= \sigma_x^2 \cdot \left[ \int_{-\infty}^{\infty} \Gamma(u) du \right]^2$$

$$= \sigma_x^2 \cdot \Gamma_{dc}^2. \tag{9}$$

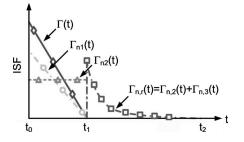

In both cases, the variance of the output noise at time  $t_0$  can be computed based on  $h(t_0, \tau)$ , which is equivalent to the sampling aperture function  $\Gamma(\tau)$  of a sampler [9] or a comparator [10], or what is more generally referred to as the impulse sensitivity function (ISF) of an LPTV system [11]–[13]. It is noteworthy that the expressions (8) and (9) are much simpler than those based on stochastic differential equations (SDE's) found in [14] and [16] and more amenable to the small-signal analysis framework commonly used in circuit design.

#### B. Linear Time-Varying Model for Clocked Comparators

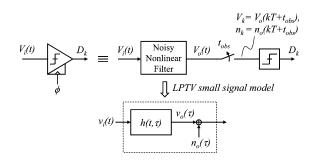

Fig. 2 illustrates the model of a clocked comparator that periodically samples an input signal  $V_i(t)$  and produces a sequence of decision results  $D_k$ . An ideal comparator would sample the instantaneous value of the input signal  $V_i(t)$  at  $t = t_{obs} + kT$

Fig. 2. (top) Clocked comparator model including a nonlinear filter, ideal sampler, and ideal slicer and (bottom) linearized PTV filter model with noise.

and produce  $D_k$  of 0 or 1 for each cycle k based on the polarity of the sampled signal compared to an implicit zero reference. Here T is the clock period and k is an integer number. Hence, the model for such an ideal comparator would be an ideal sampler followed by an ideal slicer. However, a realistic comparator does not sample the instantaneous value but rather the filtered version of the input signal over a narrow time window, of which width is commonly referred to as the *sampling aperture*. This filtering process is in general nonlinear and time-varying. Also, a comparator may add noise to the filtered signal which can cause random decision errors.

Therefore, the clocked comparator model in Fig. 2 consists of three elements: a noisy nonlinear filter, an ideal sampler, and an ideal slicer. Based on this model, the probability of a decision error can be determined by the signal-to-noise ratio (SNR) at the slicer input. While practical comparator circuits do not have such explicit distinction between these filtering, sampling, and decision elements, this mathematical model is useful for analyzing the comparator characteristics and quantifying the decision error probabilities.

While the signals in clocked comparator circuits generally make large-signal excursions during the operation, many of the important characteristics can be analyzed based on the smallsignal response of the comparator when it is near the metastable point (i.e., when the input signal  $V_i(t)$  is conditioned so that the comparator cannot reach a firm decision within the cycle). It is because the metastable point is where the comparator decision output  $D_k$  is most sensitive to noise and the comparator is most likely to generate decision errors. This small-signal response can be described based on the LTV system model explained in the previous sub-section, represented by a time-varying impulse response  $h(t, \tau)$ . Since the decision is made based solely on the filter output  $V_o(t)$  sampled at a single observation time  $t_{\rm obs} + kT$  each cycle, the small-signal response of interest is actually a subset of the time-varying impulse response,  $h(t_{obs} +$  $kT, \tau$ ) or simply  $h(t_{\rm obs}, \tau)$  without loss of generality. The function  $h(t_{obs}, \tau)$  expresses the sensitivity of the slicer input signal  $V_o(t_{\rm obs})$  with respect to the impulses arriving at different times  $\tau$  and can be found equivalent to the sampling function or aperture function defined in other literatures [9]–[11]. This function can also be viewed as being equivalent to the impulse sensitivity function (ISF) that was originally defined for oscillators in [13]. In [12], the concept of ISF was extended to general periodic circuits, where the ISF  $\Gamma(\tau)$  is defined as  $\Gamma(\tau) = h(t_{obs}, \tau)$ .

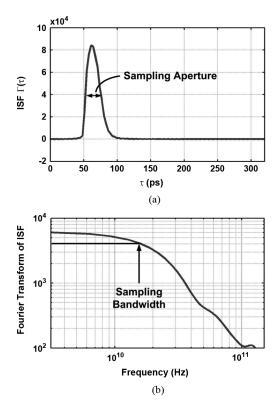

Fig. 3. (a) Impulse sensitivity function (ISF) of a clocked comparator indicating its sampling aperture. (b) The Fourier transform of the ISF indicating the sampling bandwidth.

It is noteworthy that the ISF  $\Gamma(\tau)$  captures many of the important characteristics of a clocked comparator. The LTV system (1) implies that  $\Gamma(\tau)$  is the key function that relates the smallsignal response of the filter  $v_o(t)$  to the small-signal input  $v_i(t)$ via an integral equation

$$v_o(t_{\rm obs}) = \int_{-\infty}^{\infty} v_i(\tau) \cdot \Gamma(\tau) d\tau.$$

(10)

That is, the comparator makes a decision based on the weighted average of the input signal  $v_i(\tau)$  with  $\Gamma(\tau)$  serving as the weighting factor. The width of the ISF  $\Gamma(\tau)$  corresponds to the timing resolution or the sampling aperture of the comparator, as illustrated in Fig. 3. For example, an ideal sampler would have  $\Gamma(\tau) = \delta(\tau - t_s)$ , where  $\delta(\cdot)$  is the Dirac delta function and  $t_s$ is the sampling instant. From a frequency domain perspective, the Fourier transform of the ISF indicates how fast a signal the comparator can track and capture, i.e., the sampling bandwidth.

The LTV filter model in Fig. 2 also includes an additive Gaussian noise process  $n_o(t)$  at the output of the filter. While the noise  $n_o(t)$  is in general a time-varying noise process (or a cyclo-stationary noise process if the comparator is triggered periodically), for the purpose of estimating decision error probabilities, we are only interested in the variance in  $n_o(t)$  at a specific time point  $t_{obs}$ , the sampling instant of the internal model sampler. This noise variance  $\sigma_{n,o}^2(t_{obs})$  can be derived using either (8) or (9) depending on the type of the input noise source. When there are multiple independent white and 1/f

noise sources that contribute to  $n_o(t_{\rm obs})$ , the overall noise variance  $\sigma_{n,o}^2(t_{\rm obs})$  can be expressed as:

$$\sigma_{n,o}^{2}(t_{\text{obs}}) = \sum_{j} \sigma_{n,j}^{2}(t_{\text{obs}}) + \sum_{k} \sigma_{n,k}^{2}(t_{\text{obs}})$$

$$= \sum_{j} \sigma_{j}^{2} \cdot \left[ \int_{-\infty}^{\infty} \Gamma_{j}^{2}(\tau) d\tau \right]$$

$$+ \sum_{k} \sigma_{k}^{2} \cdot \left[ \int_{-\infty}^{\infty} \Gamma_{k}(\tau) d\tau \right]^{2}$$

(11)

where  $\sigma_j^2$ 's and  $\sigma_k^2$ 's are the variances of the white noise sources and the 1/f noise sources, respectively.  $\Gamma_j(\tau)$  and  $\Gamma_k(\tau)$  are the ISF's with respect to the *j*th and *k*th noise sources, respectively.

Once the signal and noise components at the input of the slicer in Fig. 2 are found,  $V_o(t_{obs})$  and  $\sigma_{n,o}(t_{obs})$ , respectively, we can estimate the random decision error probability  $P(error_k)$  based on the Gaussian statistics

$$P(error_k) = Q\left(\sqrt{\text{SNR}}\right)$$

$$= \frac{1}{\sqrt{2\pi}} \int_{\sqrt{\text{SNR}}}^{\infty} \exp\left(\frac{-x^2}{2}\right) dx \qquad (12)$$

$$\sqrt{\text{SNR}} = \frac{V_o(t_{\text{obs}})}{\sigma_{n,o}(t_{\text{obs}})}.$$

(13)

As in most other applications, it is convenient to define the equivalent input-referred noise to compare the noise characteristics of clocked comparator circuits with different gains, or to compare the noise with input signal levels or other input-referred parameters such as the input offset voltage. The input-referred noise is defined as the equivalent stationary noise  $n_i(t)$  at the input of the comparator that would produce the same amount of noise at the slicer input,  $n_o(t_{obs})$  or that would result in the same decision error probability. If  $\sigma_{n,o}(t_{obs})$  is insensitive to the value of  $V_i(t)$ , that is, if the noise is truly additive, the input-referred noise can be computed as  $\sigma_{n,o}(t_{obs})$  divided by the dc gain of the filter. The dc gain of an LTV filter in this context corresponds to the change in the sampled filter output  $v_o(t_{obs})$ with respect to a unit change in the dc part of the small-signal component of the input signal,  $v_{i,dc}$ . This dc gain G is equal to the area of the ISF and the equivalent input-referred noise can be expressed as

$$G = \frac{v_o(t_{\rm obs})}{v_{i,\rm dc}} = \int_{-\infty}^{\infty} \Gamma(\tau) \mathrm{d}\tau \tag{14}$$

$$\sigma_{n,i} = \frac{\sigma_{n,o}(t_{\text{obs}})}{G}.$$

(15)

However, in practical simulation, we found that the noise observed at the comparator output is not strictly additive, especially when the comparator is operating very close to the metastable point. It is possible that noises modulated by deterministic, large-signal effects such as kick-back noise overwhelm the additive Gaussian noise that we are trying to measure. As described later in Section IV, we found that it yields more accurate results to estimate the Gaussian noise power from a set of decision error probability measurements with nonzero input

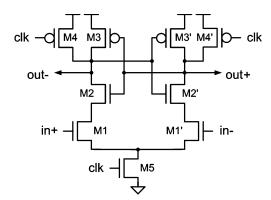

Fig. 4. Clocked comparator circuit commonly called StrongARM latch [7].

signal values  $V_{i,dc}$ 's for which the comparator is slightly apart from the metastable point and the additive Gaussian noise has the dominant effect on the error probability.

It is apparent that the ISF has a central role in determining the signal response as well as the noise response of a clocked comparator. In essence, the ISF  $\Gamma(\tau)$  with respect to the input signal indicates the small-signal gain G of the sampling filter and the ISF with respect to each noise source [i.e.,  $\Gamma_j(\tau)$  and  $\Gamma_k(\tau)$  in (11)] determines how much the noise contributes to the total slicer input noise  $n_o(t_{obs})$ . The next sections will discuss how to analyze and simulate these ISF components and estimate the total noise contribution  $\sigma_{n,o}^2(t_{obs})$  for a representative clocked comparator example.

#### **III. LTV ANALYSIS ON CLOCKED COMPARATORS**

This section demonstrates the application of the LTV system analysis framework on a representative clock comparator circuit shown in Fig. 4 which is commonly referred to as StrongARM latch [7]. We point that a recent work [14] carried out an extensive noise analysis on a variant of this comparator based on stochastic differential equations (SDEs). Since the small-signal models and equations described in [14] for each operating phase of the comparator are applicable to the LTV analysis framework as well, we provide here only the key design equations that capture the main tradeoffs with respect to the comparator noise and the random decision error. The key difference with our LTV analysis approach is that it finds the contribution of each noise source by first deriving the ISF  $\Gamma(t)$  and then calculating the output noise power according to (8) or (9). In comparison, the approach in [14] computes the noise being accumulated on each capacitive node through the operating phases by sequentially solving SDEs. While both approaches give similar results, the ISFs derived from the LTV analysis can also shed lights on how the circuit parameters influence the various key characteristics of the comparator such as sampling aperture/bandwidth and regeneration gain as well as the random decision error probability. Some of these tradeoff issues will be discussed in Section III-D.

As previously mentioned, we treat a clocked comparator as a LTV system whose linear system response changes over time. In case of the comparator circuit shown in Fig. 4, the comparator goes through a set of distinct operating phases each cycle, namely: resetting, sampling, regeneration, and decision phases. Section IV will describe each of these operating phases in more detail and some signatures in the comparator responses that can be used to distinguish one operating phase from another. For example, determining  $t_{\rm obs}$  that marks the end of the regeneration phase will be discussed.

For the purpose of estimating the random decision error, or equivalently the input-referred noise, we are primarily interested in the LTV system response of the comparator in the sampling phase and in the regeneration phase. The LTV response during these phases is captured by the filter function  $h(t, \tau)$  in our comparator model in Fig. 2. As the model concerns only with the filter response at time  $t = t_{obs}$ , the comparator behavior during the sampling and regeneration phases is well described by the ISF of the comparator  $\Gamma(\tau) = h(t_{obs}, \tau)$ . The rest of this section visit each of the sampling and regeneration phases and analytically derive the expressions for the ISFs, from which we can get the expression for the input-referred noise of the comparator.

However, it is noted that the analysis to be described is only an approximation since it assumes that the comparator abruptly switches through distinct operating phases over time and within each phase, the small-signal circuit parameters such as transconductance  $(g_m)$  would stay constant. Practical comparator circuits do not abruptly transition from one phase to another; rather their characteristics change continuously with time. Nonetheless, this approximation serves well the purpose of identifying the key design tradeoffs governing the input-referred noise of the comparator.

## A. Sampling Phase

Initially, the comparator shown in Fig. 4 is in the resetting phase when the clock input *clk* is low. The reset switches M4and M4' pull the output nodes out+ and out- to  $V_{dd}$  and the internal nodes X and X' to approximately  $V_{dd} - V_{Tn}$ , where  $V_{Tn}$  is the threshold voltage of an nMOS transistor. During this phase, the noise currents from the reset switches can contribute to the noise voltages on the output nodes. We will discuss their contributions to the total input-referred noise later once all the ISFs are derived.

When *clk* switches to high at  $t = t_0$ , the input differential pair *M*1 and *M*1' starts discharging the nodes *X* and *X'* depending on the input voltage difference. The cross-coupled nMOS pair, *M*2 and *M*2' then discharges the output nodes out+ and out- depending on the voltage difference between *X* and *X'*. Hence, the comparator is sampling the input voltages onto the internal nodes X/X' and the output nodes out + /out-. Until the voltage on out+ or out- drops below *V*dd - $V_{Tp}$ , where  $V_{Tp}$  is the threshold voltage of pMOS, the pMOS cross-coupled pair *M*3 and *M*3' remains in cutoff state. Let's assume this sampling phase lasts until  $t = t_1$ . The duration of the sampling phase  $t_1 - t_0$  can be approximated as

$$t_1 - t_0 = \frac{C_{\text{out}} \cdot V_{\text{Tp}}}{I_{d1}} \tag{16}$$

where  $C_{\text{out}}$  is the total capacitance on each output node and  $I_{d1}$  is the drain current of the transistor M1. The above expression basically corresponds to the amount of time required to discharge the output nodes from  $V_{\text{dd}}$  down to  $V_{\text{dd}} - V_{\text{Tp}}$ .

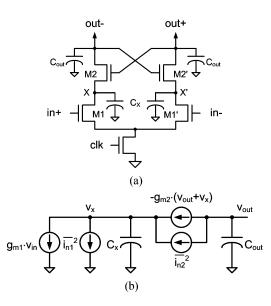

The approximate small-signal model for the comparator in the sampling phase is shown in Fig. 5. Also shown are the drain

Fig. 5. (a) Clocked comparator in the sampling phase. (b) Its small-signal model.

current noise sources  $i_{n1}$  and  $i_{n2}$  from the transistors M1 and M2, respectively. From this small-signal model, we can derive the transfer function from the small-signal input  $v_{in}$  to the small-signal output  $v_{out}$  as the following:

$$\frac{v_{\text{out}}(s)}{v_{\text{in}}(s)} = \frac{g_{m1} \cdot g_{m2}}{sC_{\text{out}}C_x \left(s + \frac{g_{m2}(C_{\text{out}} - C_x)}{C_{\text{out}}C_x}\right)}$$

(17)

where  $g_{m1}$  and  $g_{m2}$  are the transconductances of M1 and M2, respectively, and  $C_x$  and  $C_{out}$  are the total capacitances associated with the nodes X and out, respectively.

If we assume that the time constant of the nonzero pole in (17) is sufficiently longer than the duration of the sampling phase  $t_1 - t_0$ , i.e.,  $|g_{m2}(C_{\text{out}} - C_x)/C_{\text{out}}C_x| \ll 1/(t_1 - t_0)$ , then we can simplify the expression in (17) to

$$\frac{v_{\text{out}}(s)}{v_{\text{in}}(s)} \cong \frac{g_{m1} \cdot g_{m2}}{s^2 C_{\text{out}} C_x} = \frac{1}{s^2 \tau_{s1} \tau_{s2}}$$

(18)

where we have defined two time constants  $\tau_{s1} \equiv C_x/g_{m1}$  and  $\tau_{s2} \equiv C_{out}/g_{m2}$ . Note that the resulting transfer function in (18) corresponds to two cascaded integrations; an impulse arriving at the input will give rise to a ramp at the output. Considering the ISF with respect to the input  $v_{in}$ , the circuit has the higher gain for the input impulse arriving earlier in time since the resulting ramp has a longer time available for it to rise. In expression

$$\Gamma(t) \cong \frac{t_1 - t}{\tau_{s1} \tau_{s2}} \cdot G_R, \quad \text{for} \quad t_0 \le t \le t_1 \quad (19)$$

where  $G_R$  is the regeneration gain of the comparator which will be derived in the next subsection. Since all the contributions during the sampling phase will be amplified by a factor of  $G_R$ and the ISF for the comparator is defined as  $h(t_{obs}, t)$ , i.e., the sensitivity of  $v_{out}$  at time  $t_{obs}$ , the end of the regeneration phase, the ISF in (19) is multiplied by  $G_R$ . We can perform the similar analysis to derive the ISFs with respect to the current noise sources  $i_{n1}$  and  $i_{n2}$ . First, the transfer functions are

$$\frac{v_{\text{out}}(s)}{i_{n1}(s)} \cong \frac{g_{m2}}{s^2 C_{\text{out}} C_x} \tag{20}$$

$$\frac{v_{\text{out}}(s)}{i_{n2}(s)} \cong \frac{1}{sC_{\text{out}}} \tag{21}$$

and their ISFs,  $\Gamma_{n1}(t)$  and  $\Gamma_{n2}(t)$ , respectively, are expressed as below. Notice that  $\Gamma_{n2}(t)$  is flat within the sampling phase since the transfer function in (21) is a single integration

$$\Gamma_{n1}(t) \cong \frac{1}{C_x} \cdot \frac{t_1 - t}{\tau_{s2}} \cdot G_R, \qquad \text{for } t_0 \le t \le t_1 \quad (22)$$

$$\Gamma_{n2}(t) \cong \frac{1}{C_{\text{out}}} \cdot G_R, \quad \text{for } t_0 \le t \le t_1.$$

(23)

As in the case of  $\Gamma(t)$ , the ISFs with respect to the noise sources,  $\Gamma_{n1}(t)$  and  $\Gamma_{n2}(t)$ , are scaled by the regeneration gain  $G_R$ , which is discussed next.

#### B. Regeneration Phase

When the output nodes out+ and out- fall sufficiently low that the pMOS devices M3 and M3' finally turn on, the crosscoupled inverter pair M2-M2'-M3-M3' starts regenerating the voltage difference stored on the output nodes via positive feedback. During this phase, we assume that the input devices M1 and M1' are in linear region with very large conductance compared to the other devices; hence the internal nodes X and X' are considered almost short-circuited to ground as in [14].

The small-signal model of the comparator in the regeneration phase based on this assumption is shown in Fig. 6. The regeneration time constant  $\tau_R$  is given by the transconductance of the inverter and the load capacitance

$$\tau_R = \frac{C_{\text{out}}}{(g_{m2,r} + g_{m3,r})} \equiv \frac{C_{\text{out}}}{g_{m,r}}$$

(24)

where  $g_{m2,r}$  and  $g_{m3,r}$  denote the transconductance of the devices M2 and M3 during the regeneration phase, respectively, and if we assume that the regeneration lasts from time  $t_1$  to time  $t_2$  (i.e.,  $t_{obs} = t_2$ ), then the regeneration gain  $G_R$  is

$$G_R = \exp\left(\frac{t_2 - t_1}{\tau_R}\right).$$

(25)

The small-signal model in Fig. 6 also implies that the comparator is no longer sensitive to the input voltage and also to the noise current from the input devices M1 and M1' once the regeneration starts after  $t = t_1$ . In other words, the ISFs with respect to  $v_{in}$  and  $i_{n1}$  are zero during the regeneration phase. This is a crude approximation, but implies that the sampling aperture of the comparator is primarily determined by the duration of the sampling phase  $t_1 - t_0$ , which in turn is set by the output capacitance  $C_{out}$  and the current pulled by the stack of nMOS transistors M2 - M1 - M5. As we will see shortly, the longer aperture time  $t_1 - t_0$  can reduce the input-referred offset, but can degrade the sampling bandwidth of the comparator. This parameter can be adjusted by sizing M1, M2, or M5.

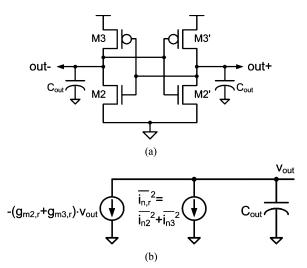

Fig. 6. (a) Clocked comparator in the regeneration phase. (b) Its small-signal model.

Fig. 7. Approximate ISFs of the clocked comparator with respect to the input  $(\Gamma(t))$  and with respect to the device noise sources  $(\Gamma_{n,1}(t), \Gamma_{n,2}(t), \text{ and } \Gamma_{n,r}(t))$ .

While the cross-coupled inverter pair is regenerating the signals on out+ and out-, the drain current noise from M2, M2', M3, and M3' can contribute to the output voltage and get regenerated as well. If we define a combined noise source as  $i_{n,r}$ as shown in Fig. 6, then the ISF with respect to this noise source  $\Gamma_{n,r}(t)$  is

$$\Gamma_{n,r}(t) = \Gamma_{n,2}(t) + \Gamma_{n,3}(t)$$

$$\cong \frac{1}{C_{\text{out}}} \cdot \exp\left(\frac{t_2 - t}{\tau_R}\right), \quad \text{for } t_1 \le t \le t_2.(26)$$

Note that the ISF  $\Gamma_{n,r}(t)$  exponentially decays with time t since the noise arriving at the output nodes later in time has less time to be regenerated and the regeneration gain is an exponential function of the time available.

As a summary, Fig. 7 plots the ISFs derived analytically for the sampling and regeneration phases. In comparison with the simulated ISFs plotted in Fig. 8 based on the periodic AC (PAC) analysis procedure outlined in [12], the two ISFs agree well in general, but the readers may notice a few discrepancies which can be attributed to the simplifying assumptions that we have made. One discrepancy is that within the sampling phase  $t_0 \le t \le t_1$ , the simulated input ISF  $\Gamma(t)$  and noise ISFs  $\Gamma_{n,1}(t)$ ,  $\Gamma_{n,2}(t)$ , and  $\Gamma_{n,3}(t)$  shown in Fig. 8 have rather different shapes than the linearly decreasing ramps or constant value as shown in Fig. 7. It is due to the fact that the small-signal parameters in the

Fig. 8. Simulated ISFs of the clocked comparator: (a) ISF with respect to the input  $(\Gamma(t))$  and (b) ISFs with respect to the device noise sources  $(\Gamma_{n,1}(t), \Gamma_{n,2}(t), \text{ and } \Gamma_{n,3}(t))$ .

model in Fig. 5(b) such as the transconductances  $g_{m1}$  and  $g_{m2}$ and the capacitances  $C_x$  and  $C_{out}$  change continuously with time, rather than staying constant. Fig. 9 plots the trajectories of the transconductances with time and tries to factor out the variations in the small-signal parameters by plotting the input ISF  $\Gamma(t)$  normalized to the product of  $g_{m1}$  and  $g_{m2}$ . According to (19),  $\Gamma(t) \cdot \tau_{s1} \tau_{s2} \cong \Gamma(t) \cdot C_x / g_{m1} \cdot C_{out} / g_{m2} \cong (t_1 - t) \cdot G_R$ and the quantity  $\Gamma(t)/(g_{m1} \cdot g_{m2})$  should follow the linearly decreasing trajectory for  $t_0 \leq t \leq t_1$  if the capacitances  $C_x$  and  $C_{\text{out}}$  were constant during the period. The resulting plot shown in Fig. 9(b) is closer to the analytical  $\Gamma(t)$  in Fig. 7 where the remaining errors can be attributed to the nonlinear capacitances that vary within the sampling phase. In addition, the aperture width of the simulated input ISF  $\Gamma(t)$  matches well to the duration marked by  $t_0$  and  $t_1$ , the times at which the transistor pairs M1/M1' and M3/M3' start conducting, respectively. Similar observations can be made for the noise ISFs  $\Gamma_{n,1}(t)$ ,  $\Gamma_{n,2}(t)$ , and  $\Gamma_{n,3}(t)$ .

The other discrepancy is that the simulated noise ISFs have nonzero sensitivities for the time before  $t_0$ . It is because the circuit has finite bandwidths in filtering the noises and therefore the noise that arrives before  $t_0$  can still affect the comparator output. The sensitivity should drop exponentially as the noise arrives earlier in time before  $t_0$  and the associated time constant is determined by the circuit bandwidths. While we do not explicitly derive the noise ISFs in the resetting phase in this paper, their nonzero sensitivities before  $t_0$  are taken into account when we lump the noise contributions before  $t_0$  into an equivalent 2kT/C noise that arrives at  $t = t_0$ .

Another observation that is worth noting from Fig. 8(b) is that the noise ISF  $\Gamma_{n,2}(t)$  changes its sign before and after  $t = t_0$ .

Fig. 9. (a) Trajectories of device transconductances  $g_{m1}$ ,  $g_{m2}$ , and  $g_{m3}$  during the sampling and regeneration phases of the comparator and (b) the input ISF normalized to the product of  $g_{m1}$  and  $g_{m2}$  for the comparison with the analytical expression in (19) and Fig. 7.

During the resetting phase, the positive noise current from M2pulls the node voltage on X higher and therefore helps keeping the output voltage at high values. On the other hand, during the sampling phase, the same polarity noise current from M2 causes the output node voltage to be discharged to a lower value. As a result, the ISF  $\Gamma_{n,2}(t)$  with respect to noise from M2/M2'pair has a low dc value which is desirable for suppressing 1/fnoise or mismatch effects according to (9). This makes sense as the transistor M2/M2' precharges its source nodes X/X' to ~  $V_{\rm dd}$  –  $V_{\rm Tn}$ , canceling the  $V_{\rm Tn}$  mismatch between M2 and M2'by a first order. The alternating signs of the ISF  $\Gamma_{n,2}(t)$  would not be observed if the internal nodes X and X' are precharged to a fixed voltage (e.g.,  $V_{dd}$ ) with additional pull-up devices as in [14].

### C. LTV Noise Analysis

Now that we have derived all the ISFs with respect to the input signal as well as to the major noise sources as illustrated in Fig. 7, we can estimate the input-referred noise of the clocked comparator.

First, we derive the small-signal dc gain G according to (14)

$$G = \frac{v_o(t_{\text{obs}})}{v_{i,\text{dc}}}$$

$$= \int_{-\infty}^{\infty} \Gamma(t) dt = \frac{(t_1 - t_0)^2}{2\tau_{s1}\tau_{s2}} \cdot \exp\left(\frac{t_2 - t_1}{\tau_R}\right). \quad (27)$$

Second, we compute the contribution of each noise source to the output noise variance measured at  $t = t_{obs}$  using either (8) or (9). For the sake of simplicity, we consider only the contribution of the thermal noise

$$\sigma^{2}(i_{n1}) = 4kT\gamma \cdot g_{m1},$$

$$\sigma^{2}(i_{n2}) = 4kT\gamma \cdot g_{m2}$$

$$\sigma^{2}(i_{n,r}) = 4kT\gamma \cdot (g_{m2,r} + g_{m3,r})$$

(28)

where  $\gamma$  is the excess noise factor for short-channel MOS devices [17]. Note that the noise variance expressions in (28) account for the noise from both devices in a pair (e.g., M1 and M1'). Since thermal noises are white, we can derive the following expressions for each contribution to the total output noise variance  $\sigma_{n,o}^2$  at time  $t = t_{obs}$

$$\sigma_{n1,o}^{2} = \sigma^{2}(i_{n1}) \cdot \int_{t_{0}}^{t_{1}} \Gamma_{n1}^{2}(t) dt = \frac{4kT\gamma}{3C_{x}} \cdot \frac{(t_{1} - t_{0})^{3}}{\tau_{s1} \cdot \tau_{s2}^{2}} \cdot G_{R}^{2}$$

$$\sigma_{n2,o}^{2} = \sigma^{2}(i_{n2}) \cdot \int_{t_{0}}^{t_{1}} \Gamma_{n2}^{2}(t) dt = \frac{4kT\gamma}{C_{\text{out}}} \cdot \frac{t_{1} - t_{0}}{\tau_{s2}} \cdot G_{R}^{2}$$

$$\sigma_{nr,o}^{2} = \sigma^{2}(i_{n,r}) \cdot \int_{t_{1}}^{t_{2}} \Gamma_{n,r}^{2}(t) dt \cong \frac{2kT\gamma}{C_{\text{out}}} \cdot G_{R}^{2}.$$

(29)

In addition, in order to account for the noise contributions during the resetting phase before  $t = t_0$ , we assume that each capacitive node gets an impulse noise arriving at time  $t = t_0$ with its noise power equal to 2kT/C, where C is the total node capacitance. Considering their ISFs that are in similar forms to (22) and (23), the contributions to the total output noise at time  $t = t_{obs}$  are

$$\sigma_{nx,o}^{2} = \frac{4kT}{C_{x}} \cdot \left(\frac{t_{1} - t_{0}}{\tau_{s2}}\right)^{2} \cdot G_{R}^{2}$$

$$\sigma_{no,o}^{2} = \frac{4kT}{C_{\text{out}}} \cdot G_{R}^{2}.$$

(30)

Again, the noise variances are for the differential output including the contributions from both devices in a pair. Assuming the noises are independent of each other, the total output noise variance at  $t = t_{obs}$  is simply a sum of the individual noise contributions:  $\sigma_{n,o}^2 = \sigma_{n1,o}^2 + \sigma_{n2,o}^2 + \sigma_{n3,o}^2 + \sigma_{nx,o}^2 + \sigma_{no,o}^2$ . Finally, the input-referred noise  $\sigma_{n,i}$  is  $\sigma_{n,o}$  divided by the

small-signal dc gain G, according to (15)

$$\begin{aligned} \sigma_{n,i}^{2} &= \frac{\sigma_{n,o}^{2}}{G^{2}} \\ &= \frac{(\sigma_{n1,o}^{2} + \sigma_{n2,o}^{2} + \sigma_{n3,o}^{2} + \sigma_{nx,o}^{2} + \sigma_{no,o}^{2})}{G^{2}} \\ &\cong \frac{16kT\gamma}{3C_{x}} \cdot \frac{\tau_{s1}}{t_{1} - t_{0}} + \frac{16kT\gamma}{C_{out}} \cdot \frac{\tau_{s1}^{2} \cdot \tau_{s2}}{(t_{1} - t_{0})^{3}} \\ &+ \frac{8kT\gamma}{C_{out}} \cdot \frac{\tau_{s1}^{2} \cdot \tau_{s2}^{2}}{(t_{1} - t_{0})^{4}} \\ &+ \frac{16kT}{C_{x}} \cdot \frac{\tau_{s1}^{2}}{(t_{1} - t_{0})^{2}} + \frac{16kT}{C_{out}} \cdot \frac{\tau_{s1}^{2} \cdot \tau_{s2}^{2}}{(t_{1} - t_{0})^{4}}. \end{aligned}$$

(31)

Authorized licensed use limited to: Texas A M University. Downloaded on February 25,2010 at 13:20:01 EST from IEEE Xplore. Restrictions apply

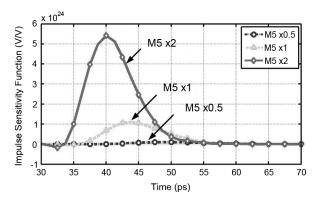

Fig. 10. Simulated input ISFs with various tail device (M5) sizes.

Note that the above expression has common terms  $\tau_{s1}/(t_1 - t_0)$ and  $\tau_{s2}/(t_1 - t_0)$  which can be expressed in  $g_m/I_d$  terms using (16)

$$\frac{\tau_{s1}}{t_1 - t_0} = \frac{C_x}{C_{\text{out}}} \cdot \left(\frac{g_{m1}}{I_{d1}} \cdot V_{Tp}\right)^{-1}$$

$$\frac{\tau_{s2}}{t_1 - t_0} = \left(\frac{g_{m2}}{I_{d2}} \cdot V_{Tp}\right)^{-1}.$$

(32)

The expressions for the input-referred noise in (31) and (32) suggests that in order to minimize random decision errors, it is desirable to attain large  $g_m/I_d$  for the input pair M1 - M1' and the regenerative nMOS pair M2 - M2'. Equivalently, it is desirable to keep the sampling aperture  $t_1 - t_0$  wide compared to the time constants  $\tau_{s1}$  and  $\tau_{s2}$ . As discussed in [14], the large  $g_{m1}/I_{d1}$  for the input pair M1 - M1' can be achieved by increasing their sizes at the cost of the increased input capacitance or by decreasing the input common-mode voltage. The  $g_{m2}/I_{d2}$  for the pair M2 - M2' can be achieved by increasing their sizes. However, while adjusting such design parameters to improve the noise response, their impacts on the other comparator characteristics such as the sampling aperture  $t_1 - t_0$  and the sampling gain G must be considered in order for the best overall performance.

#### D. Design Considerations

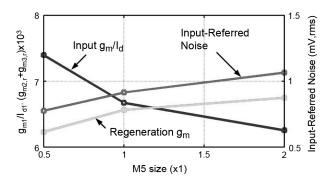

The subsection examines the design tradeoff issues in further detail when one is trying to reduce the input-referred noise by increasing the  $g_m/I_d$  values according to (31) and (32).

One way to increase  $g_m/I_d$  without increasing the input capacitance is to decrease the size of the tail device M5 in Fig. 4. The smaller tail device reduces the current  $I_d$  flowing through the input pair devices M1 - M1' and their gate overdrives, which are inversely proportional to their  $g_m/I_d$  values. Fig. 10 plots the input ISFs of the comparators with different tail device sizes:  $0.5 \times$ ,  $1 \times$ , and  $2 \times$  of the nominal size. As one reduces the size of M5, the comparator gets the wider sampling aperture (indicated by the width of the input ISF) but the lower regeneration gain (indicated by the area under the ISF). It is because as the current  $I_d$  drops, the transconductances  $g_{m1}$ ,  $g_{m2}$ , and  $g_{m3}$  degrade and the sampling aperture and gain will vary according to our analytical formulas in (16) and (27). Fig. 11 confirms that the input-referred noise improves with the decreasing M5 size but the reduction in the gain may be problematic for

Fig. 11. Input-referred noise as a function of the tail device (M5) size.

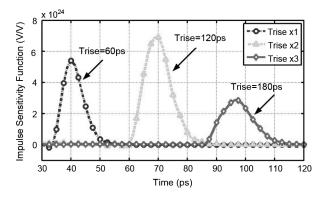

Fig. 12. Simulated input ISFs with various clock rise time (Trise) values.

preventing metastability error probability or keeping the minimum detectable input voltage difference low.

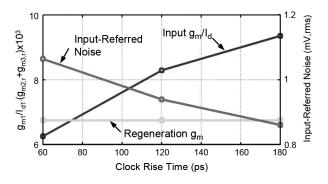

A better way to increase  $g_m/I_d$  is to slow down the clock transition rate as reported in literature [19]. By doing so, one can increase the  $g_m/I_d$  values of the M1 - M1' and M2 - M2' devices during the sampling phase without degrading the transconductance  $q_{m,r}$  during the regeneration phase. Fig. 12 plots various input ISFs of the comparator with M5 size of  $2\times$  while increasing the clock rise time. When the clock rise time is increased from 60 to 120 ps, the sampling gain increases due to the larger  $g_m/I_d$ , according to (27) and (32). However, as the clock rise time increases further up to 180 ps, the gain drops as the slow rise time eats into the period available for regeneration  $(t_2 - t_1)$ . As with the previous case, the sampling aperture widens as the clock signal rises slowly and the available current during the sampling phase decreases. Fig. 12 verifies that the input-referred noise indeed improves with the slower rise time and the larger  $g_m/I_d$ , whereas the regeneration transconductance  $g_{m,r}$  remains unaffected.

It is clear that the expressions in (16), (27), (31), and (32) can effectively guide the tradeoff decisions regarding the sampling aperture, gain, and input-referred noise of a clocked comparator. One important lesson is that many of the techniques for reducing the input-referred noise typically widens the sampling aperture and degrades the bandwidth of the comparator. Therefore, there exists an optimal, nonzero sampling aperture width that suits each application.

## IV. LPTV SIMULATION OF CLOCKED COMPARATORS

The LTV system analysis framework discussed so far works well with the periodic simulation analyses available from RF

Fig. 13. Input-referred noise as a function of the clock rise time.

circuit simulators in the same way that the LTI small-signal analysis method works with the dc, ac, and NOISE analyses in SPICE [18]. The commercial RF simulators such as SpectreRF and ADS first compute the periodic steady-state (PSS) response of a given circuit (e.g., oscillators or mixers) using either time-domain shooting Newton or frequency-domain harmonic balance algorithms and derive the linearized LPTV system of the circuit at the steady state [3]-[6]. Based on this LPTV system model, the simulator can compute the periodic AC transfer function for designated input and output sidebands or compute the power-spectral density (PSD) of the cyclo-stationary noise resulting from various noise sources in the circuit. In SpectreRF, the former analysis is referred to as periodic AC (PAC) analysis and the latter as periodic noise (PNOISE) analysis. These RF simulators are at the mature stage and can handle very large circuits efficiently (more than 10000 elements).

Thus, the only requirement to simulate the ISF and the noise responses via RF circuit simulators is to set up the circuit under test to be periodic. For periodic clocked comparators, the circuit is already periodic as long as the input waveforms are dc or periodic with the clock cycle. For comparators that are triggered asynchronously, we can perform the simulation assuming the trigger signal is a clock with a sufficient long period. As long as we are not concerned with the residual effects from previous cycles (e.g., incomplete reset), the periodic setup should produce sufficiently accurate results. In cases where we are interested in effects that span multiple decision cycles, we can perform the same LPTV simulation with the fundamental period of the periodic steady-state response being multiple clock cycles. In this case, the sampling filter ISF may span multiple clock cycles.

Once the periodic steady-state response of the comparator is simulated, the ISF's from various input stimulus points can be computed using the PAC analysis and the noise power at a specified observation point  $t_{obs}$  can be found using the time-domain PNOISE analysis in SpectreRF. The procedure to derive ISF's from the circuit's PAC responses is outlined in [12] in case the simulator does not directly provide the time-varying transfer function  $H(j\omega; t)$ . The noise power at  $t_{obs}$  can be computed from the PSD of the sampled noise at time  $t_{obs}$  via integration

$$\sigma_{n,o}^2(t_{\rm obs}) = \int_0^{1/2T_p} PSD(f;t_{\rm obs})df$$

(33)

Fig. 14. Simulated waveforms of the clocked comparator near the clock rising edge.

where  $T_p$  is the fundamental period of the periodic steady-state response, which may or may not be equal to the clock period Tas described above. The integration is from 0 to  $1/(2 \cdot T_p)$  because the SpectreRF reports a singled-sided PSD of the sampled noise (i.e., after the noise folding). Hence, the integration from 0 to T/2 yields to the total noise power  $\sigma_{n,o}^2(t_{obs})$ .

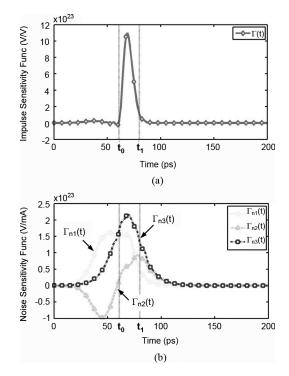

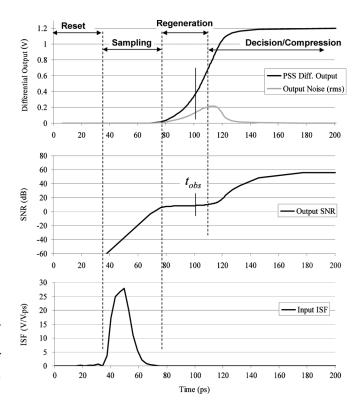

Fig. 14 shows the simulated periodic steady-state (PSS) response of the differential output of the clocked comparator discussed in Section III and illustrated in Fig. 4. Only a portion of the entire clock period of 625-ps (1.6-GHz) near the rising clock edge is shown, so the return-to-reset behavior after the comparison completes is not visible in Fig. 14. The upper plot shows the large-signal PSS output as well as the rms value of the differential output noise  $\sigma_{n,o}(t)$ , computed by integrating the sampled noise PSD(f;t) produced by the PNOISE analysis at each simulation time step t. The lower plot shows the differential output SNR versus time.

Four regions of operation are noted in Fig. 14. Initially the sampler is held in a reset state and the PSS differential output is zero. During reset, there is a small but nonzero output noise determined by the reset devices operating in the linear region and the output capacitance. Since we have no signal, the SNR is zero, or  $-\infty$  dB, during reset. In the second region, the input signal is sampled and transferred to the output nodes, resulting in a rapid rise in the output SNR. As time progresses, exponential regeneration of the output voltage by M2 - M3 takes hold. As discussed in Section III, this exponential regeneration in time means that signal and noise impulses injected to the output node earlier in the cycle have exponentially larger impact than the equivalent injections at later times. In other words, the

ISFs of the comparator with respect to the newly arriving signal and noise components are decaying exponentially with time. As these ISF's approach to zero, the circuit continues to regenerate the output voltage resulting from the previous input and noise signals, but no longer accepts new signal and noise contributions. Therefore, both the signal and noise components grow at the same rate resulting in an approximately constant SNR, as shown in the third region of Fig. 14. The fourth operation region begins when large signal output compression occurs, ultimately producing a logic-level decision output. The output voltage after saturating to a hard logic level is completely insensitive to the incremental signal or noise change at any previous time, so the output noise power returns to a small value similar to the noise level during the reset phase. While a decision error may occur, the decision output itself is essentially noise free. At this stage, the saturated outputs correspond to the ideal slicer output  $D_k$  in Fig. 2 rather than to the sampled filter output  $V_o(t)$ .

Based on this discussion, we can now determine the appropriate observation time point  $t_{obs}$  at which we compute the decision error probabilities based on the LTV model as in (12). The observation time  $t_{\rm obs}$  marked in Fig. 14 represents a time at which the large signal nonlinearity has not yet led to the compression of the output noise power. Because the nonlinear decision response has not been excited yet, up to this time point, the behavior of the circuit can be accurately modeled by the LTV small-signal model in Fig. 2. Also, since the signal and noise events occurring later than  $t_{obs}$  no longer affect the output, the decision outcome has already been determined. That is, the operation of the circuit after  $t_{obs}$  is to regenerate the already present output signal and noise to a full-logic output level, a process that can be modeled by the ideal sampler and slicer in Fig. 2. Therefore, the decision error probability is given by (12) and (13), where  $V_o(t_{obs})$  is the PSS output at the indicated  $t_{obs}$ . Similarly, the ISF's of the comparator can be derived from the time-varying impulse responses  $h(t, \tau)$  evaluated at  $t = t_{obs}$ .

It is to note that the choice of evaluation time  $t_{obs}$  is not unique, as a range of time points within the regeneration phase satisfy the criteria discussed above. However, the times within this range all have approximately the same SNR, and predict similar decision error probabilities. We found two methods that work reasonably well. One is to choose the time point at which the small-signal gain  $G(t_{obs})$  in (34) has the maximum value. The other is to choose the time point at which the incremental gain  $G^*(t_{obs})$  computed from two large-signal responses with marginally different  $V_{i,dc}$ 's as in (35) deviates more than 10% from the small-signal gain G(t). For both methods, the intention is to find the latest time point at which the comparator remains in the linear, regenerative amplification mode

$$G(t) = \frac{v_o(t)}{v_{i,dc}} = \int_{-\infty}^{\infty} h(t,\tau) d\tau$$

(34)

$$G^{*}(t) = \frac{\Delta V_{o}(t)}{\Delta V_{i}(t)} = \frac{(V_{o,1}(t) - V_{o,2}(t))}{(V_{i,1}(t) - V_{i,2}(t))}.$$

(35)

## V. COMPARISON WITH MEASUREMENT RESULTS

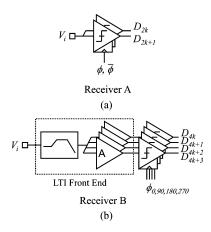

The simulation procedure outlined in Section IV is applied to two different wireline receivers shown in Fig. 15 and the

Fig. 15. Architecture of two high-speed data receivers simulated and measured.

Fig. 16. Receiver A simulated ( $\gamma = 2$ ) and measured receiver BER.

results of both cases are compared with the measured random noise performance. The first example, Receiver A, fabricated in a 90-nm CMOS process, uses  $2\times$  interleaved comparators in Fig. 4 to directly sample a differential input. The differential input is terminated by poly-silicon resistors (not shown) to match the 100  $\Omega$  differential channel impedance. The second example, Receiver B, fabricated in a 65-nm CMOS process, has a similar differential termination and comparator design, but the input signal passes through a linear front-end circuit, consisting of a linear equalizer and preamplifiers, before the  $4\times$  interleaved comparators.

# A. Receiver A—Direct Input Sampling

In the direct input sampling receiver, the random noise includes the contributions from the  $2\times$  interleaved comparators themselves as well as the thermal noise from the termination resistors. A differential input capacitance greater than 2 pF (including pad metallization and ESD) limits the thermal noise contribution of the termination resistors to less than 100  $\mu$ V, rms, which is found to be negligible compared to the equivalent input noise of the comparator itself.

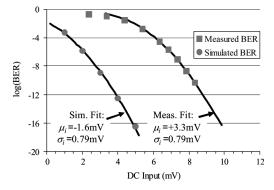

The standalone comparator was simulated with a range of excess noise factors  $\gamma = 1, 2, 3$  to account for the excess noise seen in short-channel MOS devices [17], as this information was not provided by the CMOS foundry (we treated NTNOI parameter in BSIM4 as an equivalent parameter to  $\gamma$ ). For each case, the random decision error probability, or the bit error rate (BER), was simulated for a set of small dc inputs  $V_{i,dc}$  according to (12) and (13) in Section II. The simulation data in Fig. 16 show the resulting BER( $V_{i,dc}$ ) for  $\gamma = 2$ .

TABLE I SIMULATED AND MEASURED RMS INPUT NOISE

| Receiver                  | Simulated (mV) |      |      |      | Measured (mV)        |

|---------------------------|----------------|------|------|------|----------------------|

|                           | $\gamma = 1$   | γ=2  | γ=3  | γ=4  | (Pos. / Neg. / Avg)  |

| A) Direct Sampling        |                |      |      |      | (0.79 / 0.65 / 0.72) |

| BER fit $\sigma_i$        | 0.59           | 0.79 | 0.94 |      |                      |

| $\sigma_i = \sigma / a_0$ | 0.55           | 0.73 | 0.87 |      |                      |

| B) LTI Front-End          |                |      |      |      | ( 0.87 / 0.83 / 0.85 |

| BER fit $\sigma_i$        |                | 0.62 | 0.73 | 0.83 |                      |

| $\sigma_i = \sigma / a_0$ |                | 0.64 | 0.75 | 0.86 |                      |

As mentioned in Section II, the equivalent input-referred noise was found by fitting the simulated error probability results into an additive Gaussian noise model in (36), where the parameters  $\mu_i$  and  $\sigma_i$  are the input-referred offset and rms noise power, respectively. The model fit values for  $\sigma_i$  corresponding to the excess noise factors  $\gamma = 1, 2, 3$  are listed in the first row of Table I. Alternatively, an equivalent input referred rms noise voltage may be estimated by dividing the comparator's rms output noise  $\sigma_o$  by its simulated small-signal gain G at time  $t_{obs}$ , yielding similar results listed in the second row of Table I (simulated at  $V_{i,dc} = 3 \text{ mV}$ )

$$BER(V_{i,dc}) = Q\left(\frac{V_{i,dc} - \mu_i}{\sigma_i}\right).$$

(36)

The equivalent input-referred noise for Receiver A was measured in the laboratory by directly measuring a posteriori decision error probability  $BER(V_{i,dc})$  for various dc inputs. The input stimulus was generated from two precision power supplies connected through high-ratio resistive voltage dividers to attenuate any possible external supply noise. The BER was detected by an external BERT via an on-chip loopback path from the comparator outputs. Fig. 16 shows the measured BER results for positive dc inputs with the BERT detecting errors against an "all ones" pattern. The measured data for BER below  $2 \times 10^{-5}$ are fit to (36) to arrive at a measured rms input noise  $\sigma_i$ . The procedure is repeated for positive and negative input voltages, resulting in the input-referred noises of 0.79 mV, rms and 0.65 mV, rms, respectively, for an average value of 0.72 mV, rms. This measured input-referred noise approximately matches the simulation results shown in Table I for  $\gamma = 2$ .

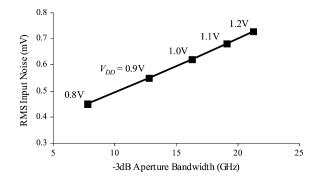

Fig. 17 shows the simulated equivalent input-referred noise and the -3 dB aperture bandwidth for Receiver A with  $\gamma = 2$ across a range of supply voltages. The aperture bandwidth is defined as the -3 dB magnitude response frequency of the Fourier transform of the simulated ISF. Increasing the supply voltage increases the aperture bandwidth of the comparator, consequently making it sensitive to external signal and noise inputs over a wider bandwidth, but also increases the impact of device noise within the comparator itself.

## B. Receiver B-With LTI Front-End

In many applications comparators are preceded by LTI circuits such as equalizers and preamplifiers which can add noise to the input signal and contribute to the random decision error probability. While it is possible to separately simulate noise contributions from such LTI circuits with the linear ac noise simulation, it is important to note that the ISF of the comparator will filter the noise from these preceding stages, reducing the total

Fig. 17. Simulated input noise versus sampling bandwidth as  $V_{\rm DD}$  is varied for Receiver A (CM input =  $V_{\rm DD}$ -200 mV,  $\gamma$  = 2).

Fig. 18. Simulated output noise spectrum of front-end circuits in Receiver B.

noise power that they contribute toward decision errors. This noise reduction is not free however; it comes at the expense of reducing the signal bandwidth since the signal itself is also filtered by the ISF. The periodic simulation on the combined LTI front-end plus comparator circuit properly accounts for these interactions.

The same simulation and measurement techniques used for Receiver A were applied to Receiver B incorporating LTI circuits and comparators. Again, foundry information is unavailable for the excess noise factor  $\gamma$ , so the simulations were performed over the range of  $\gamma = 2, 3, 4$ . The simulated and measured random noise performance listed in Table I show that the measured rms input noise of 0.85 mV is close to the simulation results for  $\gamma = 4$  in this 65-nm CMOS process.

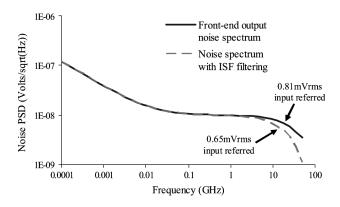

Separate periodic simulation of the comparator and linear ac simulation of the LTI front-end were also performed to examine the impact of comparator ISF filtering on the front-end output noise PSD. The simulated LTI front-end noise for  $\gamma = 3$ is plotted in Fig. 18. The solid line shows the noise PSD at the output of the LTI circuits. The dashed line shows the same noise PSD filtered by the normalized Fourier transform of the comparator ISF, showing less high frequency noise above the aperture bandwidth of approximately 20 GHz. Referred to the input nodes by the DC gain of the front-end circuits, the total noise voltages for these two power spectra are 0.81 mV, rms and 0.65 mV, rms, respectively. Such sizeable impact on the total noise power is observed despite the relatively high aperture bandwidth of the comparator because the integrated noise power is relatively sensitive to the PSD at high frequencies. The comparator's own noise contribution, referred to the input of the front-end circuits, is 0.47 mV, rms. With or without the consideration of ISF noise filtering, the combined front-end and comparator equivalent input-referred noise is calculated to be either 0.77 mV, rms or 0.94 mV, rms, respectively. Compared to the simulation results of 0.73 mV, rms and 0.75 mV, rms for the periodic simulations on the complete receiver shown in Table I and the same noise factor  $\gamma = 3$ , we find that separate simulation of the LTI front-end and comparator noise contributions yields comparable results when the ISF filtering effect is properly accounted for.

### VI. CONCLUSION

This paper described the LTV model for clock comparators that can accurately predict the decision error probability due to random noises without resorting to the more general stochastic differential equation models. The LTV model that consists of filtering, sampling, and decision operations is applicable for understanding the design trade-offs in clocked comparators as well as estimating their random decision error probability using the RF simulation techniques. Comparators typically do not have separate filtering, sampling, and decision circuits, but rather these operations are temporally separated, allowing them to be modeled as consecutive operations in the LTV system model. The periodic simulation results with SpectreRF for two high-speed data receivers, one with and one without linear circuits preceding the comparators, match the measured noise performance, confirming the validity of the approach.

#### References

- L. Zadeh, "Frequency analysis of variable networks," *Proc. IRE*, vol. 38, pp. 291–299, Mar. 1950.

- [2] J. Roychowdhury, "Reduced-order modeling of time-varying systems," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 10, pp. 1273–1288, Oct. 1999.

- [3] K. S. Kundert, "Introduction to RF simulation and its application," *IEEE J. Solid-State Circuits*, vol. 34, no. 9, pp. 1298–1319, Sep. 1999.

- [4] M. Okumura, H. Tanimoto, T. Itakura, and T. Sugawara, "Numerical noise analysis for nonlinear circuits with a periodic large signal excitation including cyclostationary noise sources," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 40, no. 9, pp. 581–590, Sep. 1993.

- [5] A. Demir, A. Mehrotra, and J. Roychowdhury, "Phase noise in oscillators: A unifying theory and numerical methods for characterization," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 5, pp. 655–674, May 2000.

- [6] R. Telichevesky, K. S. Kundert, and J. K. White, "Efficient AC and noise analysis of two-tone RF circuits," in *Proc. ACM/IEEE Des. Autom. Conf.*, Jun. 1996, pp. 292–297.

- [7] J. Montanaro, R. T. Witek, K. Anne, A. J. Black, E. M. Cooper, D. W. Dobberpuhl, P. M. Donahue, J. Eno, W. Hoeppner, D. Kruckemyer, T. H. Lee, P. C. M. Lin, L. Madden, D. Murray, M. H. Pearce, S. Santhanam, K. J. Snyder, R. Stephany, and S. C. Thierauf, "A 160 MHz, 32 b, 0.5 W CMOS RISC micro-processor," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1703–1714, Nov. 1996.

- [8] C. L. Portmann and T. H. Meng, "Supply noise and CMOS synchronization errors," *IEEE J. Solid-State Circuits*, vol. 30, no. 9, pp. 1015–1018, Sep. 1995.

- [9] H. Johansson and C. Svensson, "Time resolution of NMOS sampling switches used on low-swing signals," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 237–245, Feb. 1998.

- [10] T. Toifl, C. Menolfi, M. Reugg, R. Reutemann, P. Buchmann, M. Kossel, T. Morf, J. Weiss, and M. L. Schmatz, "A 22-Gb/s PAM-4 receiver in 90-nm CMOS SOI technology," *IEEE J. Solid-State Circuits*, vol. 41, no. 4, pp. 954–965, Apr. 2006.

- [11] M. Jeeradit, J. Kim, B. Leibowitz, P. Nikaeen, V. Wang, B. Garleep, and C. Werner, "Characterizing sampling aperture of clocked comparators," in *Dig. Tech. Papers, Symp. VLSI Circuits*, Jun. 2008, pp. 68–69.

- [12] J. Kim, B. S. Leibowitz, and M. Jeeradit, "Impulse sensitivity function analysis of periodic circuits," in *Proc. ACM/IEEE Int. Conf. Comput.-Aided Des.*, Nov. 2008, pp. 386–391.

- [13] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb. 1998.

- [14] P. Nuzzo, F. De Bernardinis, P. Terreni, and G. Can der Plas, "Noise analysis of regenerative comparators for reconfigurable ADC architectures," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 7, pp. 1441–1454, Jul. 2008.

- [15] B. S. Leibowitz, J. Kim, J. Ren, and C. J. Madden, "Characterization of random decision errors in clocked comparators," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2008, pp. 691–694.

- [16] A. Demir, E. W. Y. Liu, and A. L. Sangiovanni-Vincentelli, "Time-domain non-monte carlo noise simulation for nonlinear dynamic circuits with arbitrary excitations," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 15, no. 5, pp. 493–505, May 1996.

- [17] R. P. Jindal, "Compact noise models for MOSFETs," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2051–2061, Sep. 2006.

- [18] L. W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," Ph.D. dissertation, Dept. Electr. Eng. Comput. Sci., Univ. California, Berkeley, CA, 1975.

- [19] H. Geib, W. Weber, E. Wohlrab, and L. Risch, "Experimental investigation of the minimum signal for reliable operation of DRAM sense amplifiers," *IEEE J. Solid-State Circuits*, vol., no. 7, pp. 1028–1035, Jul. 1992.

Jacha Kim (S'94–M'03) received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 1997, and received the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1999 and 2003, respectively.

Currently, he is a Consulting Assistant Professor with Stanford University, Stanford, CA. From 2001 to 2003, he was with True Circuits, Inc., Los Altos, CA, developing phase- and delay-locked loops for processors and ASICs. From 2003 to 2006, he was

with Inter-university Semiconductor Research Center (ISRC), Seoul National University, Seoul, Korea as a post-doctoral researcher. From 2006 to 2009, he was with Rambus, Inc., Los Altos, CA, as a Principal Engineer, developing advanced design and verification methodologies for analog and mixed-signal circuits.

Dr. Kim was a recipient of the Takuo Sugano Award for Outstanding Far-East Paper at 2005 International Solid-State Circuits Conference (ISSCC) and the Low Power Design Contest Award at 2001 International Symposium on Low Power Electronics and Design (ISLPED). He has served on the technical program committee of Design Automation Conference (DAC), International Conference on Computer-Aided Design (ICCAD) and Asian Solid-State Circuits Conference (A-SSCC).

**Brian S. Leibowitz** (S'97–M'05) was born in 1976. He received the B.Sc. degree in electrical engineering from Columbia University, New York, NY, in 1998 and the Ph.D. degree in electrical engineering and computer science from University of California at Berkeley, in 2004, where his doctoral research included the developed a fully integrated CMOS imaging receiver for free-space optical communication.

His graduate studies at Berkeley were supported by a Fellowship from the Fannie and John Hertz Foun-

dation. Since 2004 he has been with Rambus, Inc., Los Altos, CA, where he has worked on equalization and mixed-signal circuit design for a variety of high-speed and low power serial links and memory interfaces.

Dr. Leibowitz was a recipient of the Edwin H. Armstrong Award from Columbia University.

**Jihong Ren** (M'06) received the Ph.D. degree in computer science from the University of British Columbia, Vancouver, BC, Canada, in 2006, where she worked on optimal equalization for chip-to-chip high-speed buses.

Since January 2006, she has been with Rambus Inc., Los Altos, CA, where she has worked on equalization algorithms and link performance analysis.

**Chris J. Madden** (M'90) received the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1990.

He is a Senior Principal Engineer in Signal Integrity at Rambus Inc., Los Altos, CA, where he has worked since March 2003 on link modeling and device characterization methodologies for multi-gigabit CMOS interfaces. Prior to Rambus, he worked at several companies developing modules for fiber-optic communications, notably Agilent and Finisar. He also had a long stint at HP Laboratories

where he did millimeter-wave circuit design and characterization for instrumentation and wireless applications.