# A 0.6 mW/Gb/s, 6.4–7.2 Gb/s Serial Link Receiver Using Local Injection-Locked Ring Oscillators in 90 nm CMOS

Kangmin Hu, Student Member, IEEE, Tao Jiang, Student Member, IEEE, Jingguang Wang, Frank O'Mahony, Member, IEEE, and Patrick Yin Chiang, Member, IEEE

Abstract—This paper describes a quad-lane, 6.4–7.2 Gb/s serial link receiver prototype using a forwarded clock architecture. A novel phase deskew scheme using injection-locked ring oscillators (ILRO) is proposed that achieves greater than one UI of phase shift for multiple clock phases, eliminating phase rotation and interpolation required in conventional architectures. Each receiver, optimized for power efficiency, consists of a low-power linear equalizer, four offset-cancelled quantizers for 1:4 demultiplexing, and an injection-locked ring oscillator coupled to a low-voltage swing, global clock distribution. Measurement results show a 6.4–7.2 Gb/s data rate with BER  $< 10^{-12}$  across 14 cm of PCB, and also an 8.0 Gb/s data rate through 4 cm of PCB. Designed in a 1.2 V, 90 nm CMOS process, the ILRO achieves a wide tuning range from 1.6–2.6 GHz. The total area of each receiver is 0.0174 mm², resulting in a measured power efficiency of 0.6 mW/Gb/s.

Index Terms—Injection-locked oscillator, receiver, serial link.

#### I. INTRODUCTION

HE demand for massively parallel, high speed serial links has recently intensified due to the large amount of off-chip bandwidth required for future multi-core processing and networking applications [1]–[3]. For example, microprocessor industry standards such as Hyper Transport [4] and Quick Path [5] require tens of high-speed serial links with a combined bandwidth greater than 200 Gb/s. In addition, recent chipsets for networking switches require off-chip I/O bandwidths of 2.4 Tb/s [3]. Due to the continual scaling of transistors in future CMOS processes, today's state-of-the art serial links can achieve tens of Gb/s per pin [6]–[8]. While such bandwidth/pin is an important consideration for these next generation applications, energy efficiency per link is the critical metric as there may exist tens to hundreds of these links on a single chip [1], [10].

In contrast to legacy backplane applications that exhibit channel losses greater than 20 dB at Nyquist frequencies [11],

Manuscript received August 27, 2009; revised November 19, 2009. Current version published March 24, 2010. This paper was approved by Guest Editor Masayuki Mizuno. This work was supported by Intel Corporation.

- K. Hu, T. Jiang, and P. Y. Chiang are with the School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, OR 97331 USA (e-mail: huka@eecs.oregonstate.edu; pchiang@eecs.oregonstate.edu).

- J. Wang was with the School of Electrical Engineering and Computer Science, Oregon State University. He is now with Broadcom Corporation, Irvine, CA 92618 USA.

- F. O'Mahony is with Intel Corporation, Hillsboro, OR 97124 USA.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2010.2040116

these future applications may optimize transmission line characteristics for better signal integrity (i.e. better connectors and shorter distances), such that channel losses are moderate and therefore do not require complex equalization [9]. Therefore, the goal for these short-haul, highly parallelized, chip-to-chip signaling is to achieve high power efficiency (mW/Gb/s) while requiring only minimal equalization power.

Recent serial link receivers have shown significant improvements in power efficiency by focusing on reducing dynamic clock power using resonantly-tuned LC oscillators, both in global clock distribution [9], [12] and local clock demultiplexing [8], [13]. In this paper, we present a multi-channel serial link receiver architecture that exhibits further improvements in dynamic clock power consumption by implementing a low-voltage swing, global clock distribution to multiple link locations, where locally-tapped, injection-locked ring oscillators (ILRO) are used to generate tunable quadrature sampling clocks for receiver demultiplexing [14].

The overview of this paper is as follows. Section II describes the architectural considerations for receiver clocking and data recovery (CDR). Next, in Section III, while most previous analyses of injection-locked oscillator are only applicable to LC oscillators [15]–[18], we propose new analytical equations that enable the understanding of injection-locked, nonharmonic ring oscillators, including the locking range, phase deskew ability, and jitter performance. Details of the receiver circuit implementation are described in Section IV. Section V provides the measurement results of the test chip, ending with the conclusion in Section VI.

#### II. RECEIVER ARCHITECTURE OVERVIEW

Embedded clock and forwarded clock architectures are the two major CDR architectures for multi-Gb/s transceivers. In embedded clock architecture, the clock is directly recovered from the incoming data such that no extra clocking channel is required. Therefore, the jitter of the recovered clock will track that of the data within the CDR loop bandwidth. If there are multiple embedded clock serial links, each can work independently from separate frequency references. However, recovering clock from the data typically requires 2× oversampling, resulting in considerable overhead in power consumption [19].

Compared with the embedded clock architecture, forwarded clock architectures [20] reduce the power of clock recovery at the expense of an additional forwarded link to deliver the transmitted mesochronous clock. However, if the chip I/O interface

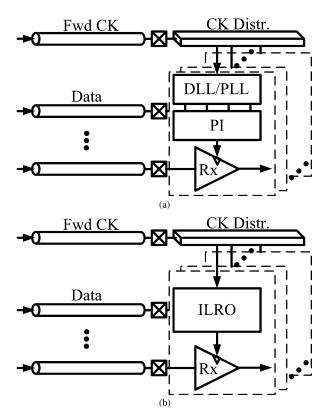

Fig. 1. (a) Conventional forwarded clock receiver architecture and (b) proposed architecture using ILRO for multiple serial links.

requires many parallel serial lanes, the power and pin overhead of the additional forwarded clock can be amortized among all the data links.

A conventional, forwarded clock receiver architecture [21] is shown in Fig. 1(a), which consists of the global clock distribution, as well as the local delay/phase locked loop (DLL/PLL) to generate multiple time-interleaved phases. The proceeding phase rotator use these phases to interpolate the appropriate phase position for the receiver to sample the incoming data. In this architecture, significant power is spent in the receiver clocking and phase generation as each link needs a local, phase rotator-based PLL to deskew the clock phase for recovery of the data [22]. For example, phase rotation alone occupies almost half the total receiver power in [9].

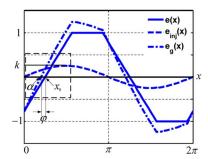

As an alternative to the phase rotator, injection-locked LC oscillators (IL-LCO) can enable clock deskew ability with less power and a lower voltage swing for the global clock. Hence, injection-locking has recently been proposed for both clock distribution [12], [23] and serial link receivers [8], [24]. As shown from the phase vector diagram in Fig. 2(a), when the frequency of the injection signal  $e_{\rm inj}(x)$  is different from the free-running frequency of the signal in the LC tank, e(x), a phase deskew  $\alpha$  will be generated between the resulting outputs  $e_{\rm g}(x)$  and  $e_{\rm inj}(x)$ . The value  $\alpha$  depends on the frequency difference and locking range, given by Alder's equation [15]:

$$\frac{d\alpha}{dt} = -\omega_{SL} \sin \alpha + \Delta\omega_0, \quad \omega_{SL} = k / \frac{d\varphi}{d\omega} = k \frac{\omega_0}{2Q} \quad (1)$$

where  $\alpha$  is the phase difference between the resultant output clock and the injection input clock,  $\varphi$  is the phase difference

Fig. 2. (a) Phase vector diagram (injection signal  $\mathrm{e_{inj}}(x)$ , free-running tank signal  $\mathrm{e}(x)$  and resultant output  $\mathrm{e_g}(x)$ ). (b) Deskew with different injection strength k, based on Adler's equation.

between the free-running frequency  $\omega_0$  and the resultant output,  $\omega_{SL}$  is the single-sided locking range, k is the injection strength defined as the ratio of the injection current and the oscillator current, and  $\Delta\omega_0$  is the frequency difference between  $\omega_0$  and the injection clock. Fig. 2(b) plots an example of the deskew phase shift along the normalized frequency difference under three injection strength values.

Monolithic LC oscillators typically have better phase noise and jitter performance than their ring oscillator counterparts due to the band-pass nature of LC tank resonators, rejecting out-of-band frequencies and filtering power supply induced noise [25]. However, for highly-parallel serial link applications, per-channel, injection-locked LC oscillators are not desirable, as each receiver would require an individual on-chip inductor, resulting in significant area penalty. In addition, LC-based oscillators exhibit very limited tuning range, may exhibit oscillator pulling due to magnetic coupling from adjacent LC oscillators [26], and do not scale well with continued technology scaling.

Although the jitter performance of free-running ring oscillators is typically worse than LC oscillators, the large jitter transfer bandwidth of injection locking can suppress and high-pass filter a large amount of oscillator phase noise, as will be described in Section III. Therefore, this work proposes a new forwarded clock receiver architecture using injection-locked ring oscillators (ILRO), as shown in Fig. 1(b), to deskew the clock used to sample the incoming data.

Compared with the conventional receiver architecture, the ILRO can achieve large phase deskew ability without the power overhead required for the combined DLL, PLL and phase interpolation. Second, it can lock to relatively small voltage swings of the injected global clock, saving power in the clock distribution. Third, the ILRO can achieve faster phase locking than a

conventional PLL because while the loop bandwidth of a PLL is limited to approximately 1/10 of the reference clock [26], injection-locking exhibits non-linear loop bandwidth characteristics.

Unfortunately, as shown in Fig. 2(b), nonlinearity can be observed in the deskew steps at the edge of locking range, when  $\alpha$  reaches around  $\pm 100^{\circ}$ . However, the linear deskew region can be increased as the injection strength k increases. To further avoid the use of the nonlinear deskew region, each receiver uses 1:4 demultiplexing, implemented with four quantizers clocked by quadrature sampling. Therefore, only  $\pm 45^{\circ}$  phase deskew range of the ring oscillator is required to enable each quadrature phase to achieve full UI range, limiting the deskew to only the linear region.

Compared with the IL-LCO, ILRO consumes less silicon area, larger tuning range, inherent multi-phase generation, and scalability to future CMOS processes. However, because previous analysis on the injection-locking phenomenon is applicable only to tank-based oscillators, new analysis is needed to further understand the behavior of the proposed ILRO.

#### III. ANALYSIS ON INJECTION-LOCKING RING OSCILLATORS

### A. Previous Approaches

Several methods have been proposed in previous works to analyze injection locking in oscillators including: the phasor-based Adler's equation, the perturbation-based projection vector (PPV) method, and the waveform-based time-domain derivation.

The classic Adler's equation [15] expresses the oscillator behavior under injection locking by using a phasor vector diagram, as shown in (1) and Fig. 2. Various time-domain solutions to Adler's equation are discussed in [16]–[18]. However, two main factors prevent this approach from being applicable to ring oscillators. First, the output waveform of ring oscillators usually does not exhibit sine wave behavior; however, the adoption of a vector-based analysis relies on the assumption that there exists only a single dominant frequency component [28]. Second, it is required to know the quality factor Q in order to solve  $\mathrm{d}\varphi/\mathrm{d}\omega$  in (1), which is not well defined for nonharmonic ring oscillators.

The PPV [27] and the transient waveform-based methods [28] are capable of analyzing both LC and ring oscillators. However, the PPV method requires a full circuit description at both the transistor and numerical levels, and only the expression for locking range is derived [27]. The analysis in [28] provides good insight into analyzing injection locking in the time domain. However, neither of these two methods gives an analytical expression for evaluating the jitter performance of injection-locked oscillators.

#### B. Proposed Approach for ILRO Analysis

Since Adler's equation is still quite simple and is proven useful for capturing the LC oscillator behavior in both the frequency and time domains, this work presents an expansion to Adler's equation that overcomes the two limitations mentioned above, making it suitable for injection-locked ring oscillators.

Fig. 3. Superposition of waveforms.

By revisiting the process of Adler's derivation [15], it can be observed:

$$\frac{d\alpha}{dt} = \varphi / \frac{d\varphi}{d\omega} + \Delta\omega_0. \tag{2}$$

Note that (2) is held for both LC and ring oscillators, as neither the assumption of Q nor a vector diagram approach has been applied yet. Next, alternative methods for finding  $d\varphi/d\omega$  as well as the relationship between  $\varphi$  and  $\alpha$  are presented.

First,  $\mathrm{d}\varphi/\mathrm{d}\omega$  can be solved directly from the small signal model of each delay cell. Assuming each delay cell contributes one dominant 3 dB pole, the loop transfer function H of an N-stage ring oscillator is

$$H(j\omega) = -\left(\frac{A_0}{1 + j\omega/\omega_{3}}\right)^N \tag{3}$$

such that its phase and derivative are

$$\varphi(j\omega) = N \tan^{-1}(\omega/\omega_{3 \text{ dB}}) \tag{4}$$

$$\left. \frac{d\varphi}{d\omega} \right|_{\omega = \omega_0} = \frac{N}{2\omega_0} \sin \frac{2\pi}{N}.\tag{5}$$

Equation (5) is obtained by noting that each delay stage exhibits a phase shift equal to  $\tan^{-1}(\omega_0/\omega_3) = \pi/N$ . Similar analysis can lead to an equivalent definition of Q for ring oscillators as shown in [29].

Second, the phase relationship can be obtained by superposition of waveforms in the time-domain rather than using a vector diagram; this enables a general analysis for any arbitrary waveform. As shown in Fig. 3, the proposed derivation assumes that the small-swing injection clock  $e_{inj}(x)$  remains like a sine-wave, but the waveform shape of the free-running ring oscillator e(x)resembles a trapezoid. Hence, this trapezoidal model reflects the actual waveform of a nonharmonic ring oscillator with equal rise and fall times, where the slope is  $k_f$ . Signal  $e_g(x)$  is the resulting superposition waveform of both the injection and the ring oscillator signals, and  $x_0$  is the phase difference between  $e_{ini}(x)$  and e(x), which is equal to  $\alpha + \varphi$ . Other symbols remain unchanged. The amplitude is normalized to the amplitude of the free-running oscillator, and the time axis x is normalized to  $2\pi$ . During the rising edge of the oscillator waveform (in the dashed box of Fig. 3), it is observed that due to superposition:

$$e_q(x) = e_{inj}(x) + e(x) = k \sin x + k_f(x - x_0)$$

(6)

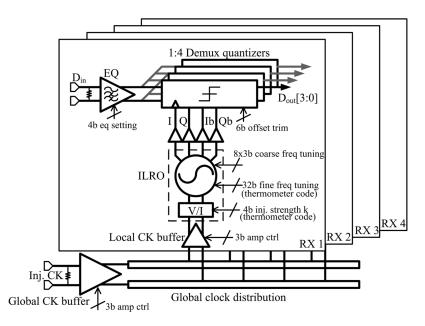

Fig. 4. Block diagram of proposed receiver.

Let (6) equal to 0, and noting that  $\sin(x)$  can be approximated as  $\sin x_0 + (x - x_0) \cos(x_0)$  using Taylor series expansion near  $x_0$ , it is obtained:

$$\varphi = -\frac{k \sin x_0}{k_f - k \cos x_0} \approx -\frac{k \sin \alpha}{k_f - k \cos \alpha} \tag{7}$$

The relationship between k<sub>f</sub> and N for ring oscillators is

$$k_f = N\eta/\pi \tag{8}$$

where  $\eta$  is a proportionality constant, close to the value of one [30].

Substituting (5), (7) and (8) into (2), we observe:

$$\frac{d\alpha}{dt} = -\frac{k}{N\eta/\pi - k\cos\alpha} \frac{2\omega_0}{N\sin(2\pi/N)} \sin\alpha + \Delta\omega_0 \quad (9)$$

Hence, the new expression for single-sided locking range  $\omega_{\rm SL}$  becomes

$$\omega_{SL} = \frac{k}{Nn/\pi - k\cos\alpha} \frac{2\omega_0}{N\sin(2\pi/N)} \tag{10}$$

Thus, we have derived new equations for analyzing the behavior of injection-locked ring oscillators (with no requirement for Q) by applying small signal and time-domain waveform analysis to Adler's derivation.

Further, by analogy between injection-locked oscillators and a 1st order PLL [31], jitter transfer and jitter generation functions can be derived as follows:

$$\left| \frac{\phi_{out}}{\phi_{inj}} \right| = \frac{1}{\sqrt{1 + (\omega/\omega_{SL})^2}}, \quad \left| \frac{\phi_{out}}{\phi_{vco}} \right| = \frac{1}{\sqrt{1 + (\omega_{SL}/\omega)^2}}$$

(11)

Therefore, ILRO will low-pass filter the noise from injection clock, while high-pass filter the noise from itself. Since the jitter

of the injection clock  $(\sigma_{\rm inj})$  and that of oscillator  $(\sigma_{\rm vco})$  are usually uncorrelated, the total jitter can be expressed as

$$\sigma_{out}^2 = \left| \frac{\phi_{out}}{\phi_{inj}} \right|^2 \sigma_{inj}^2 + \left| \frac{\phi_{out}}{\phi_{vco}} \right|^2 \sigma_{vco}^2 \tag{12}$$

The results here will be verified with measurements in Section V.

#### IV. CIRCUIT IMPLEMENTATION

Fig. 4 shows the block diagram of the major sections of the test chip. Four links are integrated for the experimental demonstration of a multiple serial link architecture using ILROs. The forwarded quarter-rate clock is first buffered by a global CML clock buffer driving a 600 um-long, ground-shielded, differential RC line to all four receivers with a 250 mV clock signal. The clock input is then coupled to each receiver through a local CML buffer that injects into the injection-locked ring oscillator. The ILRO generates tunable quadrature phases for the quantizers to recover and demultiplex the data.

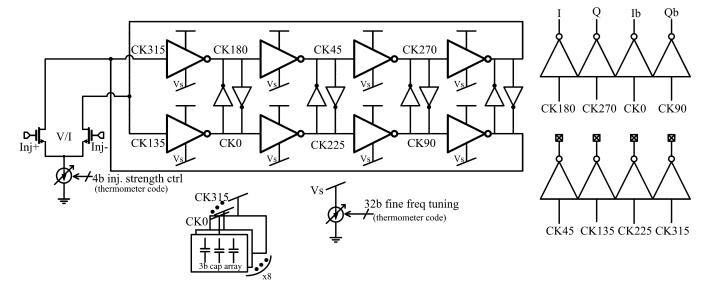

#### A. ILRO

Each injection-locked oscillator consists of a voltage-to-current (V/I) converter and a four-stage, cross-coupled, pseudo-differential current-starved ring oscillator. Simple NMOS-only differential V/I converters without resistive loading are used here to mitigate the interaction with the DC bias at the injection point. The sizes of the NMOS differential pair are carefully chosen to reduce the parasitic loading while fully steering the current source.

All the delay cells in the ring oscillator share a single current source, implemented as a 32b thermometer-encoded DAC. The minimum DAC current step is 30  $\mu$ A, enabling fine tuning of the free-running frequency of the oscillator. For coarse tuning of the

Fig. 5. Schematic of ILRO.

free-running VCO frequency, either the supply can be reduced or a 3b switched capacitor array can be utilized.

Injection-locking will cause adjacent time-interleaved phases of the oscillator to be unevenly spaced. For example, the injection nodes CK135 and CK315 exhibit significant phase asymmetry from the other six phases, as these nodes are the summing nodes from the injection-locking interpolation. However, once the differential clocks are propagated to CK0 and CK180, they are decoupled from the injection-point phase asymmetry, and now exhibit conventional inverter loading and delay. Hence, the four alternating phases (every two inverter stages) CK180, CK270, CK0, CK90 maintain adequate quadrature accuracy (less than 4.5°), both in the simulated as well as in the experimental results. Each of the eight multi-phases is loaded with the same inverter buffering, to maintain the same capacitive loading. Further phase symmetry is obtained by using small cross-coupled inverters between complementary phases, as well as using a 3b binary capacitor bank on each output clock phase to individually trim the phase imbalances that arise due to process variations or layout mismatch. In addition, for a typical application (not implemented here), an offline, static phase calibration of multiple, time-interleaved phases at reset time would be included to resolve maximum phase mismatch to several picoseconds [32], [33].

#### B. Linear Equalizer

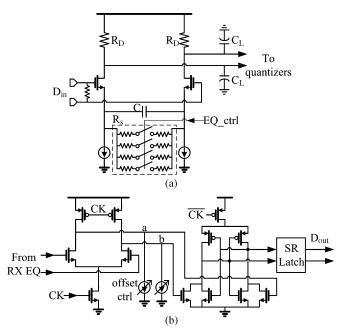

The front-end receiver equalizer is the analog component that works at the highest frequency of all the receiver blocks. A source-degenerated, linear equalizer similar to [9] is implemented, as shown in Fig. 6(a). Its voltage gain can be written as

$$A_{v} = G_{m}R_{out} \approx \frac{g_{m}}{1 + g_{m}\left(R_{s}//\frac{1}{sC}\right)} \left(R_{D}//\frac{1}{sC_{L}}\right)$$

$$= \frac{g_{m}R_{D}}{1 + g_{m}R_{s}} \frac{1 + s/\omega_{z}}{(1 + s/\omega_{p})(1 + s/\omega_{p,out})}$$

(13)

Fig. 6. (a) Schematic of RX EQ. (b) quantizer with offset control.

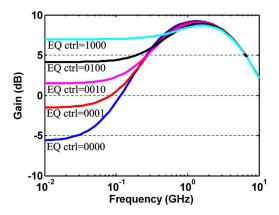

where  $\omega_z=1/R_sC$ ,  $\omega_p=(1+g_mR_s)/R_sC=(1+g_mR_s)\omega_z$ , and output pole  $\omega_{p,out}=1/R_DC_L$ . Therefore,  $R_s$  and C introduce a zero  $\omega_z$  before the pole  $\omega_p$ . If the output pole  $\omega_{p,out}$  is also designed to be larger than the zero, gain will be boosted between  $\omega_z$  and the smaller one of  $\omega_p$  and  $\omega_{p,out}$ . By switching the value of the degenerated resistor  $R_s$ , the DC gain will change as shown in Fig. 7, resulting in an effective high-pass filtering effect.

#### C. Other Building Blocks

Each quantizer of the 1:4 demuxplexing is implemented using a two-stage sense amplifier [34] and SR latch, as shown in Fig. 6(b). A 6b binary current source can be injected to nodes  $\boldsymbol{a}$  and  $\boldsymbol{b}$  in order to cancel the quantizer offset by current-imbalancing.

Fig. 7. Simulated AC response of RX EQ under different settings.

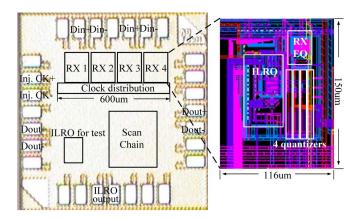

Fig. 8. Die photo and layout screen capture.

## V. EXPERIMENTAL RESULTS

The 1 mm<sup>2</sup> test chip has been fabricated in a 90 nm, 1.2 V CMOS process and tested in a chip-on-board assembly. As shown in Fig. 8, it integrates four receivers, the global clock distribution network, a digital scan chain, test output buffers and a stand-alone ILRO for test purposes. Each receiver occupies 0.0174 mm<sup>2</sup>. Due to the limitation in pad area, only near-end (RX1) and far-end (RX4) I/Os are measured. In each receiver, the four-way, demultiplexed output data can be individually selected to drive the output pads.

# A. ILRO

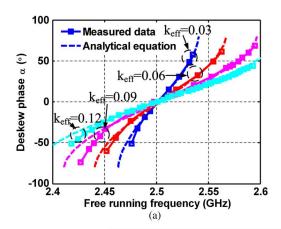

In this subsection, the analytical equations derived in Section III will be examined and compared with measurement data. Note that the stage number N=4 and assumes  $\eta=1$ . The ILRO can tune from 1.6 GHz to 2.6 GHz by coarse tuning its supply, while turning on all switches in the digital switch capacitor bank can provide an additional 250–300 MHz frequency range. Hence, this large and fine tuning range can be used to compensate possible variations. Note that a shared, frequency-locked loop (not implemented in this work) initiated at reset time, can be used at startup to calibrate and compensate for initial oscillation frequency variations [35].

Fig. 9(a) shows both the measured deskew under different injection strength  $k_{\rm eff}$  and the analytical model predicted from (9). In this measurement, the injection clock was kept constant at 2.5 GHz and the current-DAC, fine tuning control was swept

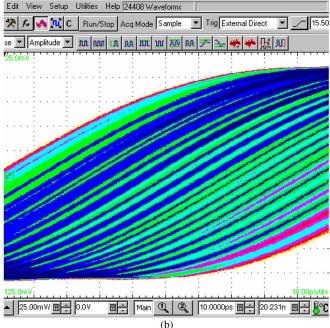

Fig. 9. (a) Deskew of ILRO; (b) overlaid waveforms by sweeping phase settings (vertical scale =25 mV/div, horizontal scale =10 ps/div).

until the oscillator operated beyond its locking range. The measured phase shift confirms the same deskew characteristics as the simulated ILRO shown previously in Fig. 2(b). The measured results also show that the ILRO can achieve greater than  $\pm 45^{\circ}$  linear deskew range. Fig. 9(b) plots the corresponding output waveforms of the ILRO, overlaid on oscilloscope, giving an intuitive viewpoint of the fine interpolation steps of ILRO. The measured injection-locking ranges for injection strength  $k_{\rm eff}=0.03,0.06,0.09,$  and 0.12 are 65, 115, 167, and 203 MHz, respectively.

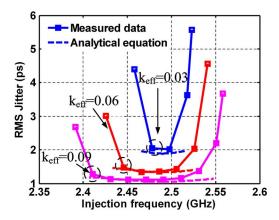

The jitter performance was measured by keeping the free-running frequency fixed at round 2.5 GHz and sweeping the frequency of the injection clock. Fig. 10 shows that the jitter of ILRO will first get slightly worse as the frequency of injection clock moves away from the free-running frequency, and then get dramatically worse at the edge of locking range. By substituting measured RMS jitters of injection clock and free-running ring oscillator into (12), we can successfully predict the jitter degradation when the injection clock is near the free-running frequency. This is because  $\omega_{\rm SL}$  will reduce slightly due to

Fig. 10. Jitter performance of ILRO.

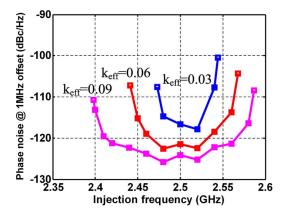

Fig. 11. Measured phase noise performance of ILRO.

the change of  $\alpha$  from (10), such that more noise of the oscillator will pass through to the output. At the edge of the locking range, the jitter worsens because the oscillator is on the cusp of losing phase lock. However, across the linear deskew range, the jitter stays sufficiently low (below 1.5 ps RMS jitter when  $k_{\rm eff}=0.09$ ) such that the jitter degradation will not affect the normal operation of the ILRO. Corresponding measurements of the phase noise shows a similar tendency in the performance degradation, as shown in Fig. 11.

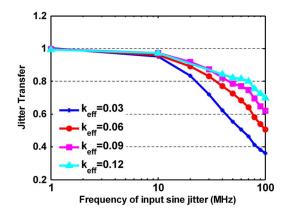

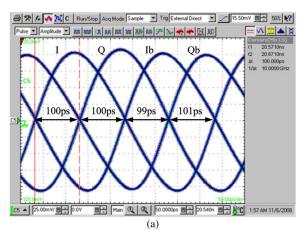

The -3 dB bandwidth at  $k_{\rm eff}=0.03,\,0.06,\,0.09,\,{\rm and}\,0.12$  are 31, 55, 80, and 100 MHz, respectively, as shown in Fig. 12. This measurement is done directly by injecting a stressed input clock with 5% UI of sine jitter generated by a BertScope 12500B. To verify the phase symmetry, quadrature output waveforms of the ILRO are overlaid in Fig. 13. Measurement across the linear deskew range shows a maximum I/Q phase and amplitude imbalance of 4.5° and 7 mV, respectively.

## B. Entire Receiver

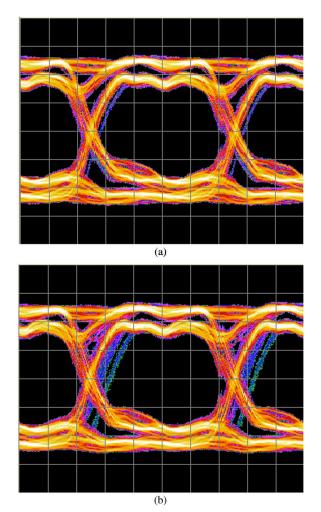

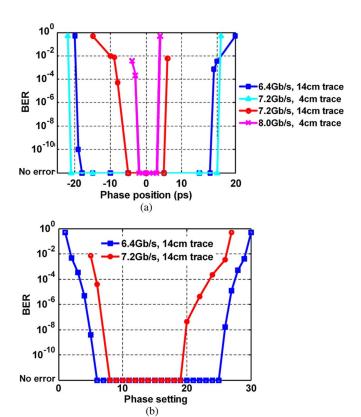

Experimental measurements are obtained from testing the far-end receiver (RX4). RX4 exhibits the longest clock distribution distance among the four receivers, and therefore shows the worse case performance of the four lanes. The results are measured from 6.4 Gb/s to 8 Gb/s with a 400 mV swing PRBS 7 data sequence generated by the BertScope under two channel conditions: 1) chip-on-board bond-wire with a 4 cm PCB trace on the test board plus two SMA connectors and cables, and

Fig. 12. Measured jitter transfer of ILRO.

Fig. 13. Phase spacing when injecting 2.5 GHz clock: (a)  $f_0 = 2.49$  GHz, (b)  $f_0 = 2.58$  GHz (vertical scale = 25 mV/div, horizontal scale = 50 ps/div).

2) uses both 1) and an additional 10 cm of FR4 PCB trace. They are denoted as 4 cm trace and 14 cm trace in this paper, and exhibit approximately 1 dB and 5 dB loss at 4 GHz, respectively.

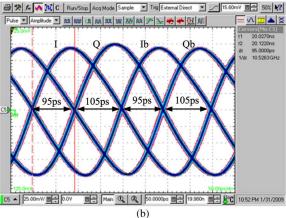

The receiver consumes 3.84 mW, 4.3 mW and 4.8 mW<sup>1</sup> at input data rates of 6.4 Gb/s, 7.2 Gb/s, and 8 Gb/s, respectively. Fig. 14 shows the breakdown of the power for the receiver. The ILRO occupies 23% of the total power consumption, which is

<sup>1</sup>We do not implement an on-chip regulator in this design. Supply noise was mitigated by using large decoupling capacitors both on-chip and off-chip and testing with an off-chip, precision digital voltage generator. Power of test buffers is not included.

Fig. 14. Receiver power breakdown.

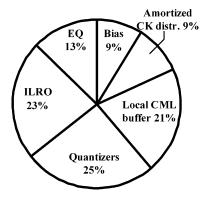

Fig. 15. Eye diagrams of recovered data under (a) 4 cm trace and (b) 14 cm trace (input data rate = 7.2 Gb/s, vertical scale = 155 mV/div, horizontal scale = 111 ps/div).

about half the ratio of a phase rotator within a conventional link receiver, as in [9]. Therefore the clock related power is reduced to about 53% of the total receiver power.

Eye diagrams of one stream of recovered 1.8 Gb/s data from the 7.2 Gb/s input are shown in Fig. 15. There exists a slightly bimodal eye diagram when the 14 cm PCB trace is used. Due to a sub-optimal design of the equalizer where the peak is placed  $2\times$  lower than desired for this PCB Nyquist bandwidth, the channel

Fig. 16. BER measurements (a) by sweeping the delay in BERT and (b) by sweeping the phase setting of ILRO.

TABLE I PERFORMANCE SUMMARY

| Technology                                  | 1.2V 90nm CMOS |          |        |  |

|---------------------------------------------|----------------|----------|--------|--|

| ILRO tuning range                           | 1.6-2.6GHz     |          |        |  |

| ILRO locking range (k <sub>eff</sub> =0.12) | 203MHz         |          |        |  |

| Phase deskew                                | 1.8°-3.6°      |          |        |  |

| resolution(k <sub>eff</sub> =0.12)          |                |          |        |  |

| ILRO power                                  | 0.88mW         | 1.08mW   | 1.3mW  |  |

|                                             | @1.6GHz        | @1.8GHz  | @2GHz  |  |

| Total RX Power (including                   | 3.84mW         | 4.3mW    | 4.8mW  |  |

| amortized power of clock distr.)            | @6.4Gb/s       | @7.2Gb/s | @8Gb/s |  |

|                                             |                |          |        |  |

plus component assembly results in more loss and reflection than expected, such that the equalization is not enough to compensate for the channel losses at higher data rate. Fig. 16 plots the measured BER bathtub curves for the two channel conditions, with the measured performance summarized in Table I. Table II compares the performance with prior state-of-the-art, energy-efficient serial links.

## VI. CONCLUSION

A four-lane, 6.4–7.2 Gb/s per link, parallel serial link receiver design has been presented. The proposed forwarded clock ar-

| TABLE II                       |  |  |  |  |

|--------------------------------|--|--|--|--|

| COMPARISON WITH RECENT DESIGNS |  |  |  |  |

|                     | [9]                         | [8]                  | This work             |

|---------------------|-----------------------------|----------------------|-----------------------|

| Data rate           | 6.25Gb/s                    | 27Gb/s               | 7.2Gb/s               |

| Architecture        | Software<br>CDR             | Forwarded<br>CK      | Forwarded<br>CK       |

| Phase tuning method | Ring-<br>VCO PLL<br>with PI | IL-LCO               | ILRO                  |

| RX power            | 8.22mW                      | 43mW                 | 4.3mW                 |

| Power<br>efficiency | 1.31<br>mW/Gb/s             | 1.6<br>mW/Gb/s       | 0.6<br>mW/Gb/s        |

| RX area             | ~0.15mm <sup>2</sup>        | 0.015mm <sup>2</sup> | 0.0174mm <sup>2</sup> |

| Technology          | 90nm<br>CMOS                | 45nm<br>CMOS         | 90nm<br>CMOS          |

chitecture using ILROs allows the test chip to obtain full UI deskew while achieving only 0.6 mW/Gb/s under moderate channel losses. The use of ILROs also exhibits other benefits including inherent multiphase generation and large jitter transfer bandwidth. Methods to avoid the nonlinearity of ILROs are also discussed. Simple analytical equations are derived to understand both the injection locking and jitter performance of ILROs and are verified with experimental measurements. The methods presented provide new insights into low power serial link design for future multi-Gb/s I/O interfaces.

#### ACKNOWLEDGMENT

The authors would like to thank Brent Close, Charlie Zhong and Freeman Zhong of LSI, for generous support of lab and equipment measurement time, Intel for funding support, and MOSIS for help in chip fabrication.

#### REFERENCES

- M. Tremblay and S. Chaudhry, "A third-generation 65 nm 16-core 32-thread plus 32-scout-thread CMT SPARC processor," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 82–83.

- [2] S. Bell, B. Edwards, and J. Amann et al., "TILE64TM processor: A 64-core SoC with mesh interconnect," in *IEEE ISSCC Dig. Tech. Pa*pers, Feb. 2008, pp. 88–89.

- [3] S. Scott, D. Abts, J. Kim, and W. J. Dally, "The BlackWidow high-radix Clos network," in *Proc. ISCA '06*, Jun. 2006, pp. 16–28.

- [4] HyperTransport I/O Technology Overview [Online]. Available: http://www.hypertransport.org/docs/wp/HT\_Overview.pdf

- [5] An Introduction to the Intel QuickPath Interconnect [Online]. Available: www.intel.com/technology/quickpath/introduction.pdf

- [6] L. Rodoni, G. von Buren, A. Huber, M. Schmatz, and H. Jackel, "A 5.75 to 44 Gb/s quarter rate CDR with data rate selection in 90 nm bulk CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 7, pp. 1927–1941, July 2009.

- [7] Y. Amamiya, S. Kaeriyama, and H. Noguchi et al., "A 40 Gb/s multi-data-rate CMOS transceiver chipset with SFI-5 interface for optical transmission systems," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2009, pp. 358–359.

- [8] F. O'Mahony, S. Shekhar, and M. Mansuri et al., "A 27 Gb/s for-warded-clock I/O receiver using an injection-locked LC-DCO in 45 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2008, pp. 452–453.

- [9] J. Poulton, R. Palmer, and A. M. Fuller *et al.*, "A 14-mW 6.25-Gb/s transceiver in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2745–2757, Dec. 2007.

- [10] H. Lee, K.-Y. K. Chang, and J.-H. Chun et al., "A 16 Gb/s/link, 64 GB/s bidirectional asymmetric memory interface," *IEEE J. Solid-State Circuits*, vol. 44, no. 4, pp. 1235–1247, Apr. 2009.

- [11] M. Pozzoni, S. Erba, and P. Viola *et al.*, "A multi-standard 1.5 to 10 Gb/s latch-based 3-tap DFE receiver with a SSC tolerant CDR for serial backplane communication," *IEEE J. Solid-State Circuits*, vol. 44, no. 4, pp. 1306–1315, Apr. 2009.

- [12] L. Zhang, B. Ciftcioglu, M. Huang, and W. Hui, "Injection-locked clocking: A new GHz clock distribution scheme," in *IEEE Proc. CICC*, Sep. 2006, pp. 785–788.

- [13] P. Chiang, W. J. Dally, and M.-J. E. Lee et al., "A 20 Gb/s 0.13 um CMOS serial link transmitter using an LC-PLL to directly drive the output multiplexer," *IEEE J. Solid-State Circuits*, vol. 40, no. 4, pp. 1004–1011, Apr. 2005.

- [14] K. Hu, T. Jiang, J. Wang, F. O'Mahony, and P. Y. Chiang, "A 0.6 mW/Gbps, 6.4-8.0 Gbps serial link receiver using local injection-locked ring oscillators in 90 nm CMOS," in *Symp. VLSI Circuits Dig.*, Jun. 2009, pp. 46–47.

- [15] R. Alder, "A study of locking phenomena in oscillators," *Proc. IRE*, vol. 34, pp. 351–356, Jun. 1946, reprinted in *Proc. IEEE*, vol. 61, pp. 1380–1385, Oct. 1973.

- [16] L. J. Paciorek, "Injection locking of oscillators," *Proc. IEEE*, vol. 53, no. 11, pp. 1723–1728, Nov. 1965.

- [17] B. Razavi, "A study of injection locking and pulling in oscillators," IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [18] N. Lanka, S. Patnaik, and R. Harjani, "Understanding the behavior of injection locked LC oscillators," in *IEEE Proc. CICC*, Sep. 2007, pp. 667–670.

- [19] J. Jaussi, B. Casper, and M. Mansuri et al., "A 20 Gb/s embedded clock transceiver in 90 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2006, pp. 340–341.

- [20] B. Casper, J. Jaussi, and F. O'Mahony et al., "A 20 Gb/s forwarded clock transceiver in 90 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2006, pp. 90–91.

- [21] B. Casper and F. O'Mahony, "Clocking analysis, implementation and measurement techniques for high-speed data links—A tutorial," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 1, pp. 17–39, Jan. 2000

- [22] A. Agrawal, P. K. Hanumolu, and G.-Y. Wei, "A 8 × 5 Gb/s source-synchronous receiver with clock generator phase error correction," in *IEEE Proc. CICC*, Sep. 2008, pp. 459–462.

- [23] Z. Xu and K. L. Shepard, "Low-jitter active deskewing through injection-locked resonant clocking," in *IEEE Proc. CICC*, Sep. 2007, pp. 9–12.

- [24] M. Hossain and A. C. Carusone, "CMOS oscillators for clock distribution and injection-locked deskew," *IEEE J. Solid-State Circuits*, vol. 44, no. 8, pp. 2138–2153, Aug. 2009.

- [25] T. H. Lee and A. Hajimiri, "Oscillator phase noise: A tutorial," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 326–336, Mar. 2004.

- [26] B. Razavi, RF Microelectronics. Englewood Cliffs, NJ: Prentice-Hall, 1998, ch. 7–8.

- [27] X. Lai and J. Roychowdhury, "Analytical equations for predicting injection locking in LC and ring oscillators," in *IEEE Proc. CICC*, Sep. 2005, pp. 461–464.

- [28] G. R. Gangasani and P. R. Kinget, "Time-domain model for injection locking in nonharmonic oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 6, pp. 1648–1658, July 2008.

- [29] B. Razavi, "A study of phase noise in CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 31, no. 3, pp. 331–343, March 1996.

- [30] A. Hajimiri, S. Limotyrakis, and T. H. Lee, "Jitter and phase noise in ring oscillators," *IEEE J. Solid-State Circuits*, vol. 34, no. 6, pp. 790–804, June 1999.

- [31] V. F. Kroupa, Phase Lock Loops and Frequency Synthesis. New York: Wiley, 2003, ch. 1.

- [32] L. Lee, D. Weinlader, and C.-K. K. Yang, "A sub-10-ps multiphase sampling system using redundancy," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 265–273, Jan. 2006.

- [33] J. Wang, "Techniques for improving timing accuracy of multi-gigahertz track/hold circuits," M.S. thesis, Dept. Elect. Eng., Oregon State Univ., Corvallis, OR, 2008.

- [34] D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18 ps setup+hold time," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2007, pp. 314–315.

- [35] J. Kim and M. A. Horowitz, "Adaptive supply serial links with sub-1-V operation and per-pin clock recovery," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1403–1413, Nov. 2002.

Kangmin Hu (S'08) received the B.S. degree in electrical engineering from Shanghai Jiao Tong University, Shanghai, China, in 2004 and the M.S. degree in microelectronics from Fudan University, Shanghai, China, in 2007. He is currently working toward the Ph.D. degree in electrical engineering at Oregon State University, Corvallis, OR.

During the spring of 2007, he interned at Intel Flash Products Group in Shanghai, China. In 2009, he was a summer intern at Montage Technology, Shanghai, China. His current research interests

include system analysis and circuit design on low power multi-Gb/s wireline transceivers.

Tao Jiang (S'08) received the B.E. degree in electronic information and engineering in 2004, and the M.S.E.E. degree in electronic science and technology in 2007, both from Tsinghua University, Beijing, China. He is currently working toward the Ph.D. degree at Oregon State University, Corvallis, OR.

He was an intern at LSI Corporation, Milpitas, CA, from September to December 2008, where he was involved with the research on the high-speed ADC design. His current technical and research interests in-

clude low-power, high-speed ADC and serial link design.

Jingguang Wang received the B.Sc. and M.Sc. degrees in microelectronics from Fudan University, Shanghai, China, in 2003 and 2006, respectively, and the M.Sc. degree in electronic engineering from Oregon State University, Corvallis, OR, in 2008.

From 2006 to 2007, he was an RF/Analog Design Engineer with RDA microelectronics, Shanghai, China, where he worked on the satellite TV tuner design. During the summer of 2008, he interned at Telegent Systems in Sunnyvale, CA, designing a SAR ADC for tuner product. In 2008, he joined

Broadcom Corporation, Irvine, CA, working on the analog front-end for Ethernet products.

Frank O'Mahony (S'99-M'03) received the B.S., M.S., and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1997, 2000, and 2004, respectively. His doctoral research focused on resonant clock distribution techniques for high-performance microprocessors.

Since 2003, he has been with Intel's Circuit Research Lab in Hillsboro, OR, His research interests include high-speed and low-power data links, clock generation and distribution, and design techniques for low-noise, variation-tolerant clocking and sig-

naling circuits.

Dr. O'Mahony received the 2003 Jack Kilby Award for Outstanding Student Paper at ISSCC.

Patrick Yin Chiang (S'99-M'06) received the B.S. degree in electrical engineering and computer sciences from the University of California, Berkeley, in 1998, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 2001 and 2007.

He is currently an Assistant Professor of electrical and computer engineering at Oregon State University, Corvallis, OR. In 1998, he was with Datapath Systems (now LSI Logic), working on analog frontends for DSL chipsets. In 2002, he was a research

intern at Velio Communications (now Rambus) working on 10 GHz clock synthesis architectures. In 2004, he was a consultant at startup Telegent Systems, evaluating low phase noise VCOs for CMOS mobile TV tuners. In 2006, he was a Visiting NSF Postdoctoral Researcher at Tsinghua University, China, investigating low-power, low-voltage RF transceivers. In summer 2007, he was a Visiting Professor at the Institute of Computing Technology, Chinese Academy of Sciences, where he collaborated on the design of multi-gigahertz ADCs and high-speed serial links. In December 2009, he was a Senior Visiting Researcher at Fudan University, Shanghai, China, researching mixed-signal circuits and systems in the State Key Lab of ASIC and System. His interests are energy-efficient VLSI interconnect and energy-constrained medical sensors.