## IBM90nm – FO4 Delay

ECEN689 High Speed I/O Dr Samuel Palermo Ref : Dr Silva [EE474 Lab manuel] http://engineering.tamu.edu/electrical/employee-resources/unixlinux-resources-helpdesk

#### **Starting Cadence for the First Time**

## -Course Directory : /mnt/lab\_files/ECEN689\_605

- 1. Make EE689 folder in your home director : mkdir ECEN689

- 2. Go to the EE689 : cd ECEN689

- 3. Copy model(directory), cds.lib(file), and ncsu from course directory

cp -rf /mnt/lab\_files/ECEN689\_605/model. cp -rf /mnt/lab\_files/ECEN689\_605/cds.lib. cp -rf /mnt/lab\_files/ECEN689\_605/ncsu.

4. Run cadence => ./ncsu

[rdliu918]@hera3 ~> (21:00:14 01/24/21) :: cd ECEN720/ [rdliu918]@hera3 ~/ECEN720> (21:01:36 01/24/21) :: cp -rf /mnt/lab\_files/ECEN689\_605/cds.lib . [rdliu918]@hera3 ~/ECEN720> (21:02:02 01/24/21) :: cp -rf /mnt/lab\_files/ECEN689\_605/ncsu . [rdliu918]@hera3 ~/ECEN720> (21:02:10 01/24/21) :: cp -rf /mnt/lab\_files/ECEN689\_605/model . [rdliu918]@hera3 ~/ECEN720> (21:02:17 01/24/21) :: ./ncsu [1] 35942 [rdliu918]@hera3 ~/ECEN720> (21:02:22 01/24/21) :: ]

## **Creating a Library**

## 1. From the CIW select Tools $\rightarrow$ Library Manager to load the Library Manager

| Library Manager: WorkArea: /homes/grad/yxs4875/689                                                                    | L3                   |                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| <u>E</u> ile <u>E</u> dit <u>V</u> iew <u>D</u> esign Manager <u>H</u> elp                                            |                      | cādence                                                                                                                 |

| Show Categories Show Files  Library  INV_4  US_8ths andILlb analogLib basic cdsDerTechLib functional rTExamples rtLib | Cell<br>Inv4<br>Inv4 | View         schematic         View       Lock       Size         Schematic       yxs4875@apollo.ece.tamu.edu       30k |

| Messages                                                                                                              |                      |                                                                                                                         |

|                                                                                                                       |                      | /                                                                                                                       |

2. Do not Attach to an existing techfile due to using IBM90nm Model which is not support by cadence.

#### **Creating a Schematic**

The first circuit we will design is a simple inverter. Select which library you want to put the cell into, in this case "INV4", and then File  $\rightarrow$  New  $\rightarrow$  Cell. Name your cell inverter. The tool you want to use here is Composer-Schematic

| File           |                                          |

|----------------|------------------------------------------|

| Library        | INV_4                                    |

| Cell           | inv4                                     |

| View           | schematic                                |

| Туре           | schematic 🔽                              |

| Application -  |                                          |

| Open with      | Schematics L 🧧                           |

| 🔲 Always us    | e this application for this type of file |

| Library path f | ile                                      |

|                | l/yxs4875/689/cds.lib                    |

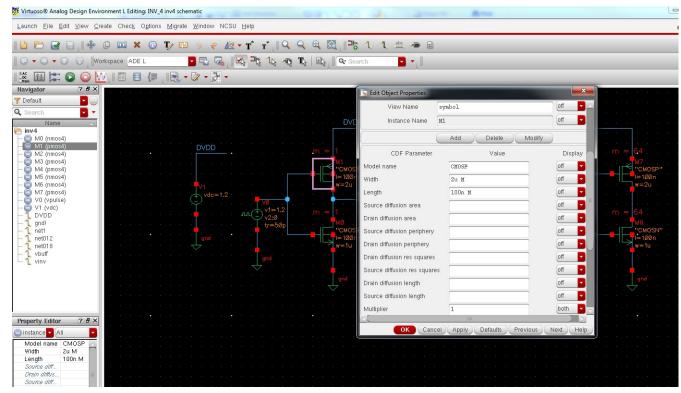

After selecting OK, the schematic window opens. We wish to add two transistors so that we can make an inverter. To do this we need to add an instance. You can do this by either clicking Add  $\rightarrow$  Instance or by pressing "i" on the keyboard. A window titled "Component Browser" should pop up. Make sure that the library analogLib is selected. Select N\_Transistors and then nmos4. Go back to the schematic and select where you would like to add the NMOS transistor. Go back to the Component Browser and select P\_transistors and then pmos4. Add this transistor to your schematic. Hit ESC to exit the Add Instance mode. Connect components together using wires. You can select Add  $\rightarrow$  Wire or use the "w" hotkey. To change the properties of a device use Edit  $\rightarrow$  Properties  $\rightarrow$  Objects or use the "q" hotkey.

### MINIMUM W/L - 0.12um/0.10um

When finished, your schematic should resemble shown Figure to measure FO4 Delay. Select Design  $\rightarrow$  Check and Save to save your schematic and make sure that there are no errors or warnings.

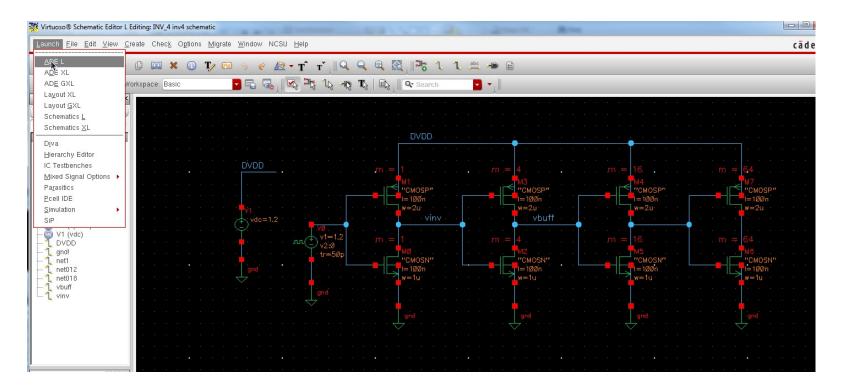

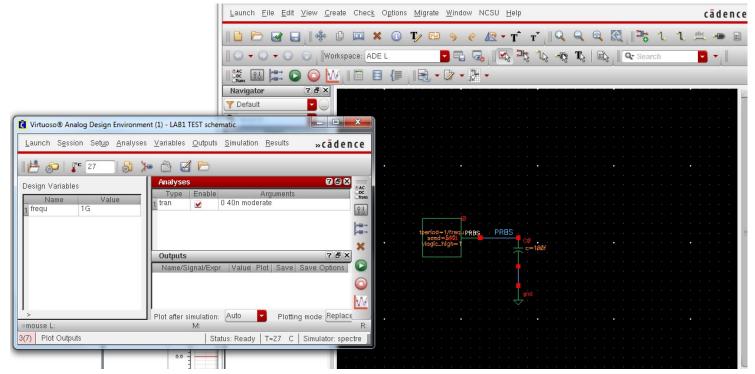

#### **Simulating the Schematic**

Start the simulator environment by selecting Launch  $\rightarrow$  ADE L

# Simulator

| 5 <b>/</b>   | DE L (1) - INV      | V4 inv4 schematic@hera3.ece.tamu.edu                                                                         |                                                  | – 🗆                                 | ×           | ADE L (1) - INV4 inv4   |                                      |                                                             |                            | - 🗆 X                    |

|--------------|---------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|-------------|-------------------------|--------------------------------------|-------------------------------------------------------------|----------------------------|--------------------------|

| <u>L</u> aun | ch S <u>e</u> ssion | Setup Analyses Variables Outputs                                                                             | <u>S</u> imulation <u>R</u> esults <u>T</u> ools | <u>H</u> elp <b>cāde</b>            | nce         | Launch Session Setu     | p <u>A</u> nalyses <u>V</u> ariables | Outputs Simulation Results                                  | <u>T</u> ools <u>H</u> elp | cādence                  |

| 12           | õ 👔                 | <u>B</u> esign                                                                                               |                                                  |                                     |             | 🎼 🤔 🧊 27                | 🛛 💩 ⊁ 🖆 I                            | 🗹 🗁                                                         |                            |                          |

|              |                     | 🔊 Simulator/Directory/Host                                                                                   | es                                               | ? 5                                 | AC<br>DC    | Design Variables        |                                      | Analyses                                                    |                            | ? 🗗 🗙 🗛 C<br>OC<br>Trans |

|              | Name                | High-Performance Simulation                                                                                  | Enable                                           | Arguments                           | Crans<br>아니 | Name                    | Value                                | Type Enable                                                 | Arguments                  | CTrans<br>약당             |

|              |                     | Model Libraries<br><u> <u> </u> </u> |                                                  |                                     |             |                         | (D) (1) (1)                          |                                                             |                            |                          |

|              |                     | Stim <u>u</u> li<br>Simulation Files                                                                         |                                                  |                                     | ×           |                         | spectre                              | )E L (1)@hera3.ece.tamu.edu                                 | ×                          | *                        |

|              |                     | <u>E</u> M/IR Analysis                                                                                       |                                                  |                                     |             | Project Directory       |                                      | ong/cadence/simulation                                      |                            |                          |

|              |                     | MATLAB/Simulink                                                                                              | s                                                |                                     |             | Host Mode               | 🖲 local 🔾 remote 🤇                   | distributed                                                 |                            | ? = ×                    |

|              |                     |                                                                                                              | me/Signal/Expr Value                             | Plot Save Save Options              | 80          | Host                    |                                      |                                                             | Save                       | Save Options             |

|              |                     |                                                                                                              |                                                  |                                     |             | Remote Directory        | OK                                   | Cancel Defaulte Appl                                        | Halp                       |                          |

|              |                     | Plot after                                                                                                   | r simulation: Auto                               | Plotting mode: Replace              |             |                         | Ōĸ                                   | <u>Cancel Defaults Apply</u><br>Plot after simulation: Auto | Plotting mod               | e: Replace               |

| ><br>        |                     |                                                                                                              | 1                                                |                                     |             |                         |                                      |                                                             |                            |                          |

| 2(4)         | Simulator/Dil       | rectory/Host                                                                                                 | Statu                                            | is: Ready   T=27 C   Simulator: spe | ctre 📗      | 2(4) Simulator/Director | yrnost                               |                                                             | Status: Ready   1=2        | 7 C Simulator: spectre 📗 |

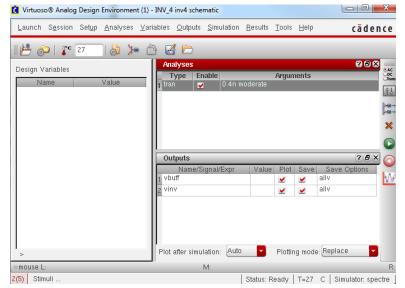

• Change simulator to "spectre"

## Select Setup $\rightarrow$ Model path and add CMOSN.m and CMOSP.m

| 🔀 spectre0: Model Library Setup         | A  | ×                 |

|-----------------------------------------|----|-------------------|

| Model File<br>⊡- Global Model Files<br> |    | Section           |

|                                         | ОК | Cancel Apply Help |

Next we need to configure the environment to run our first simulation. In the Analog Environment window select Analyses  $\rightarrow$  Choose. Select "tran"

Select Simulation  $\rightarrow$  Run or click on the green light in the bottom right corner. Once the simulation has completed, we can plot any outputs that we wish. To do this we use the calculator. To access the calculator, select Tools  $\rightarrow$  Calculator in the Analog Environment.

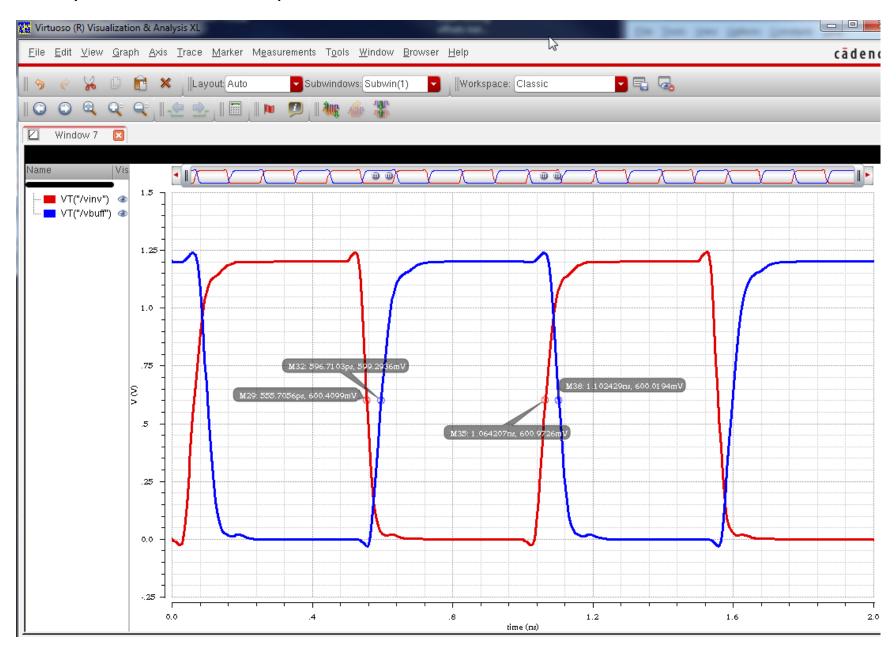

## **Simulation Result** FO4 delay for IBM90nm => 40ps

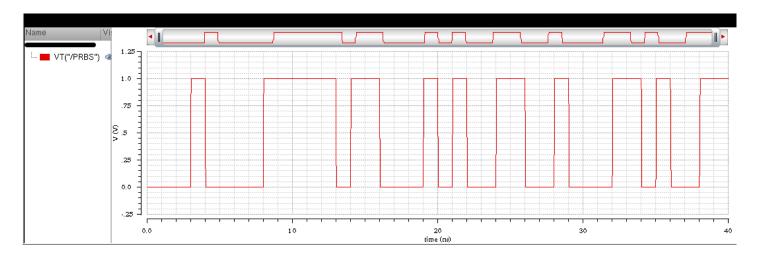

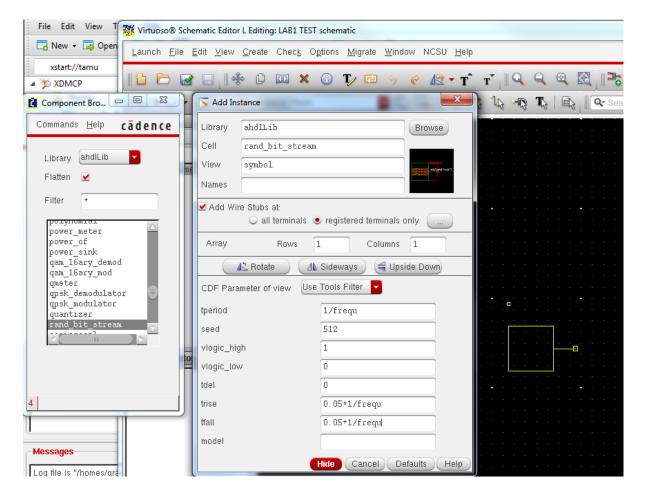

#### How to use PRBS generator in Cadence

PRBS generator can be found in ahdlLib. It is called rand\_bit\_stream. Please specify a PRBS generator as shown in Figure 1. Please set seed to 128 for 7 bit PRBS.

Figure 1 PRBS Generator Property

## **Cadence Setup**

#### **Simulation Result**