**Texas A&M University**

**Department of Electrical and Computer Engineering**

**ECEN 620 – Network Theory (Broadband Circuit Design)**

**Fall 2025**

**Exam #1**

**Instructor: Sam Palermo**

- Please write your name in the space provided below

- Please verify that there are **6** pages in your exam

- You may use one double-sided page of notes and equations for the exam

- Good Luck!

| Problem      | Score | Max Score  |

|--------------|-------|------------|

| 1            |       | 40         |

| 2            |       | 60         |

| <b>Total</b> |       | <b>100</b> |

Name: SAM PALERMO

UIN: \_\_\_\_\_

## Problem 1 (40 points)

Select the proper PLL architecture to track a frequency ramp of  $10^{12} \text{ rad/s}^2$  with a steady-state phase error of 0.01 rad. Assume that  $K_{VCO} = 2\pi * (1 \text{ GHz/V})$ , there is no loop divider ( $N=1$ ), and that the loop filter utilizes a  $1 \text{ nF}$  capacitor. Additional circuitry should be added to the loop filter to achieve a  $\zeta=2$ . **Give the value of  $K_{PD}$  (include correct units), draw the loop filter and label the filter component values.**

A 2nd-order Type 2 PLL is required to track a frequency ramp.

$$E(s) = \frac{s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

Frequency Ramp:  $\Phi_{in}(s) = \frac{1}{s^3}$

$$\Phi_{e,ss} = \lim_{s \rightarrow 0} \frac{1}{s^3} \frac{s \cdot s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2} = \frac{1}{\omega_n^2} = 0.01 \text{ rad}$$

$$\Rightarrow \omega_n = \sqrt{\frac{1}{\Phi_{e,ss}}} = \sqrt{\frac{10^{12} \text{ rad/s}^2}{0.01 \text{ rad}}} = 10^7 \text{ rad/s}$$

$$\omega_n = \sqrt{\frac{K_{PD} K_{VCO}}{NC}}$$

$$K_{PD} = \frac{\omega_n^2 NC}{K_{VCO}} = \frac{(10^7 \text{ rad/s})^2 (1)(1 \text{ nF})}{2\pi (1 \text{ GHz/V})} = \frac{100 \mu\text{A}}{2\pi}$$

$$L = \frac{2\zeta}{\omega_n C} = \frac{2(2)}{(10^7 \text{ rad/s})(1 \text{ nF})} = 400 \text{ nH}$$

$K_{PD} = \frac{100 \mu\text{A}}{2\pi}$

## Problem 2 (60 points)

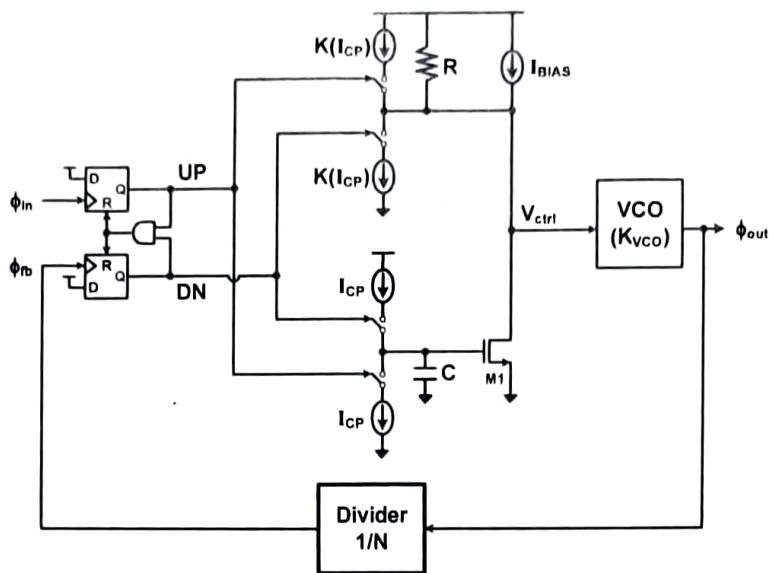

For the PLL shown below, assume that the VCO gain is  $K_{VCO}$  is positive, all transistors are operating in saturation with  $r_o = \infty$  and you can ignore any transistor device capacitors.

a) Draw the phase domain small signal model of the loop.

b) Find the expressions for the product of the forward path gain and feedback factor,  $\frac{G(s)}{N}$ , and determine the pole-zero locations of  $\frac{G(s)}{N}$ .

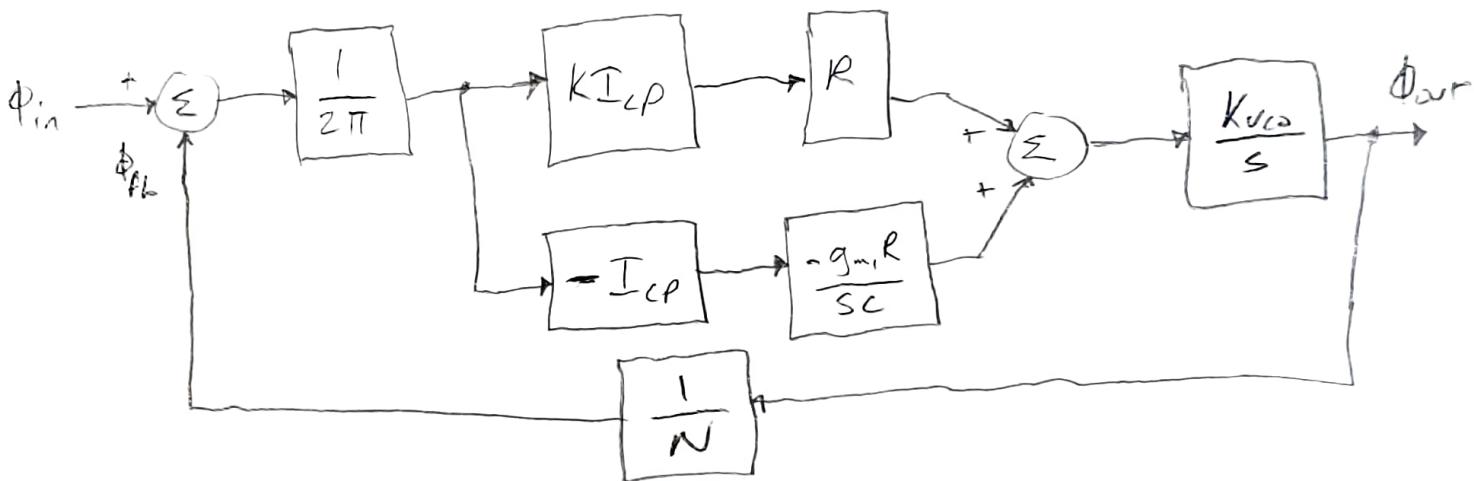

a.

b.

$$\frac{G(s)}{N} = \frac{1}{2\pi} \left[ KI_{CP}R + I_{CP} \frac{g_{m1}R}{SC} \right] \left( \frac{K_{VCO}}{s} \right) \left( \frac{1}{N} \right)$$

$$\frac{G(s)}{N} = \frac{K_{VCO}R}{2\pi} \frac{I_{CP}}{N} \left[ s + \frac{g_{m1}}{KC} \right]$$

1 zero at  $s = -\frac{g_{m1}}{KC}$

2 poles at  $s = 0$

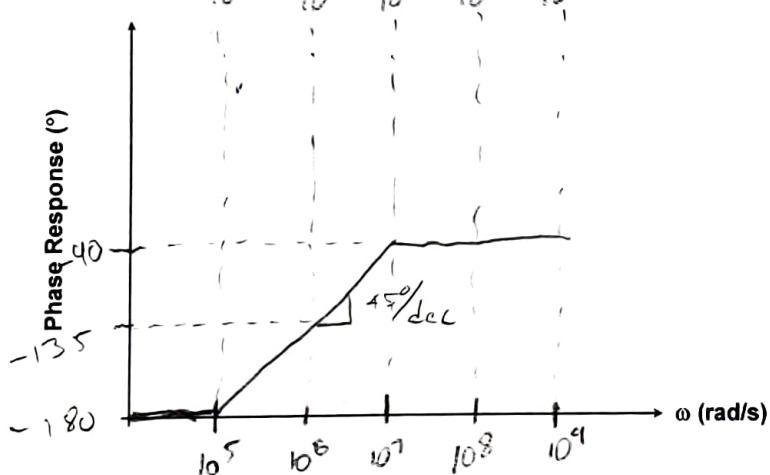

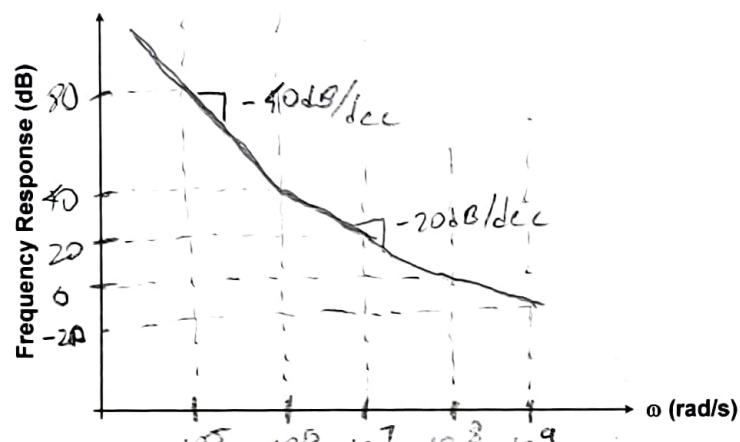

c) Assume that  $I_{CP}=10\mu\text{A}$ ,  $K=10$ ,  $R=50\text{k}\Omega$ ,  $K_{VCO}=2\pi*(1\text{GHz}/\text{V})$ ,  $g_m=20\mu\text{A}/\text{V}$  and  $N=50$ . What is the  $C$  value required for the  $\frac{G(s)}{N}$  transfer function zero,  $\omega_z$ , to equal  $1\text{Mrad/s}$ ? Sketch the  $\frac{G(s)}{N}$  Bode Plot (magnitude and phase). What is the phase margin?

$$|\omega_z| = \frac{\omega_m}{KC} \Rightarrow C = \frac{\omega_m}{K|\omega_z|} = \frac{20\mu\text{A}}{10(1\text{Mrad/s})} = 2\text{pF}$$

$$\frac{G(s)}{N} = \frac{\frac{10(10\mu\text{A})(50\text{k}\Omega)(2\pi \cdot 1\text{GHz})}{2\pi}}{s^2 + 50} [s + 10^6] = \frac{10^8 [s + 10^6]}{s^2}$$

$A + j\omega = 10^5 \text{ rad/s} \quad \left| \frac{G(j10^5)}{N} \right| \approx \frac{10^8 (10^6)}{10^{10}} = 10^4 = 80 \text{ dB}$

$$C = 2\text{pF}$$

$$\text{Phase Margin} = 90^\circ$$

d) What is the phase relationship between  $\phi_{in}$  and  $\phi_{fb}$  when is PLL locked?

The PFD will cause the PLL to lock with a  $0^\circ$  phase difference.

$$\phi_{in} - \phi_{fb} = 0^\circ$$