# Texas A&M University Department of Electrical and Computer Engineering

### ECEN 620 - Network Theory (Broadband Circuit Design)

#### Fall 2021

#### Exam #1

Instructor: Sam Palermo

- Please write your name in the space provided below

- Please verify that there are 6 pages in your exam

- You may use one double-sided page of notes and equations for the exam

- Good Luck!

| Problem | Score | Max Score |

|---------|-------|-----------|

| 1       |       | 55        |

| 2       |       | 45        |

| Total   |       | 100       |

| Name: | SAM | PALERMO |  |

|-------|-----|---------|--|

| UIN:  |     |         |  |

Problem 1 (55 points)

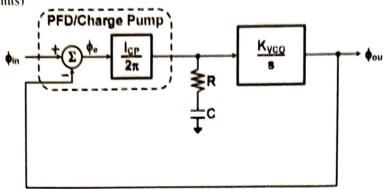

a) For the PLL block diagram shown above, find the expressions for the forward path gain G(s) and the closed-loop transfer function  $H(s)=\phi_{out}(s)/\phi_{in}(s)$ . (10 points)

$$G(S) = \frac{F_{cP}}{2\pi} K_{VO} R(S + \frac{1}{Rc})$$

$$G(s) = \frac{G(s)}{H(s)} = \frac{\frac{\operatorname{TcR}}{\operatorname{ZH}} K_{Vio} K(s) \frac{1}{\operatorname{RC}}}{S^{2} + S \frac{\operatorname{TcR}}{\operatorname{ZH}} K_{Vio} R} + \frac{\operatorname{TcR}}{\operatorname{ZH}} K_{Vio}$$

$H(s) = \phi_{out}(s)/\phi_{in}(s) =$

b) Assume that  $\mu_{N}=10\mu A/(2\pi)$ ,  $K_{VCO}=2\pi^*(100 MHz/V)$ , and that R=0. What is the value of C required for a loop gain unity-gain crossover frequency of 1Mrad/s? What is the phase margin? (10 points)

$$W/R=0 \implies G(S) = \frac{I_{CP}}{2\pi} k_{VO} = \frac{I_{Opt}A}{2\pi} \left(2\pi \cdot I_{COMIR}/U\right)$$

$$S^{2}C$$

$$S^{2}C$$

$$\left| G\left(\frac{10^6}{10^6}\right) \right| = \frac{\left(\frac{10 \text{ ad}}{2 \text{ TT}}\right) \left(\frac{2 \text{TT} \cdot 100 \text{MHz/U}}{10^6}\right)}{\left(\frac{10^6 \text{ rad/}}{2 \text{ TT}}\right)^2} = 1$$

$$C = \ln F \qquad PM = 180^{\circ} + \cancel{\xi} G(5/0^{\circ}) \qquad C = \ln F$$

$$= 180^{\circ} - 180^{\circ} = 0^{\circ} \qquad Phase Margin = 0^{\circ}$$

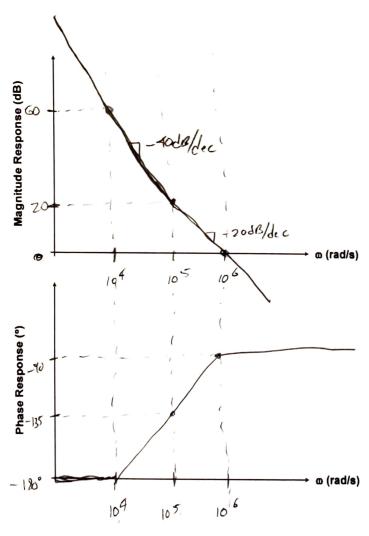

c) Now assume that C=10nF. Note, this is not the answer to (b). What is the R value required for the closed-loop transfer function zero, ω<sub>z</sub>, to equal 100krad/s? Sketch the G(s) Bode Plot (magnitude and phase). What is the phase margin now? (20 points)

$$W_{2} = \frac{1}{RC} \implies R = \frac{1}{U_{2}C} = \frac{1}{(10^{5} \cdot 10^{4})(100F)} = 1kN$$

$$G(S) = \frac{100A}{2\pi} (2\pi 10^{8})(1k)(S + 10^{5}) = \frac{10^{6} (S + 10^{5})}{S^{2}}$$

$$A + W = 10^{4} |6| = \frac{10^{6} (15^{5})}{10^{8}}$$

$$= 10^{3}$$

R= /KA

Phase Margin =  $\sim 90^{\circ}$

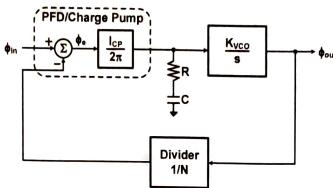

d) Now assume that the PLL is modified to include a loop divider. Using the same numerical values from part(c), what is the maximum loop division factor, N, for a minimum phase margin of 30°? (15 points)

$$G(s) = \frac{I_{cp}}{2\pi} Kv_{co}R(s + \frac{1}{Rc})$$

$$N s^{2}$$

$$PM = 180^{\circ} + CG(j\omega_u) = 190^{\circ} + tan^{-1}(\omega_u R.C) - 180^{\circ}$$

=  $tan^{-1}(\omega_u R.C) = 30^{\circ}$

$\omega_u = \frac{1}{13RC} = \frac{\omega_z}{13} = \frac{10^{5}}{13}$

$$\left|\frac{\alpha(\omega_{\lambda})}{N}\right| = 1$$

$$\frac{\left(\frac{10\,\mu\text{A}}{2\,\text{T}}\right)\left(2\pi\cdot10^{8}\right)\left(1k\right)\left(\frac{10^{5}}{43}\right)^{2}+\left(10^{8}\right)^{2}}{N\left(\frac{10^{5}}{73}\right)^{2}}=1$$

$$N = 34.6$$

Max. N for 30° Phase Margin = 34,6 => 34 (assuming only integer)

#### Problem 2 (45 points)

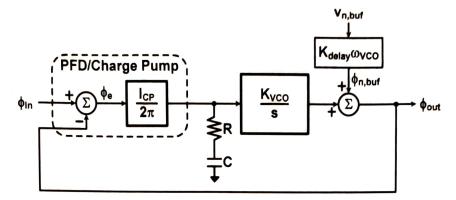

This problem investigates how voltage noise on an inside-the-loop post-VCO buffer impacts the output phase noise. Assume that the post-VCO buffer noise is modeled as an additive phase noise term, as shown in the model below.

a) Find the expression for the post-VCO buffer voltage noise induced phase noise transfer function,  $T(s) = \phi_{out}(s)/v_{n,buf}(s)$ . (15 points)

$$\frac{\Phi_{out}(s)}{V_{n,buf}(s)} = \frac{s^{2} k_{delay} U_{uco}}{s^{2} + 2 k_{wn} + w_{n}^{2}}$$

where  $w_{n} = \sqrt{\frac{F_{co}k_{vco}}{2\pi c}}$  and  $h = \frac{w_{n}}{2}RC$

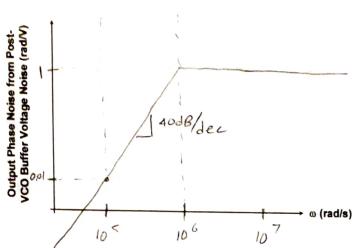

b) Assume that the PLL has been designed for  $\omega_n=1$  Mrad/s and  $\zeta=1$ . Also, assume that  $\omega_{VCO}=10$  Grad/s and  $K_{delay}=-100$ ps/V. Sketch the post-VCO buffer voltage noise induced phase noise **magnitude** versus frequency. Label the high frequency value and the key frequencies and slopes in the plot. Use a log scale for both the x and y-axis. (10 points)

Pour (S) = 52 Kdelay who => High Frequency Magnitude = | Kdelay way

- | (-10cpc/v) | 10 Grad/s)

= | (-1) Cpc/v) | 10 Grad/s)

c) Assume that the post-VCO buffer voltage noise has sinusoidal modulation.

$$v_{n,buf}(t) = 0.1\sin(10^7 t)$$

(V)

What is the output jitter amplitude in ps? (10 points)

107 is well above the 2-poles, in the high-pass region

Output jither amplitude =

$$(|rad/v|)(100mV) = 0.|rad$$

A+  $106rad/s => 0.|rad(\frac{2\pi Lioops)}{2\pi rad} = 10ps$

Output Jitter Amplitude (ps) =  $|0\rangle$

d) Assuming 10<sup>5</sup> rad/s sinusoidal noise, what is the maximum voltage amplitude for an output jitter amplitude of 0.5ps? (10 points)

Max Voltage Amplitude = 500 m $\sqrt{}$

## Scratch Paper