# ECEN326: Electronic Circuits Spring 2022

Lecture 8: Output Stages and Power Amplifiers

Sam Palermo

Analog & Mixed-Signal Center

Texas A&M University

#### Announcements

- Homework 8 due Apr 28

- Exam 3 May 5

- 12:30 2:30

- Closed book w/ one standard note sheet

- 8.5"x11" front & back

- Bring your calculator

- Emphasis will be on Lectures 7-8

- Sample Exam3s posted on website

- Reading

- Razavi Chapter 14

### Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

# Why Special Output Stages or Power Amplifiers?

Power amplifiers are necessary to efficiently drive a load with high power

- Examples

- A cellphone may need 1W of power at the antenna

- Audio systems require tens to hundreds of Watts

- As ordinary voltage/current amplifiers are not suited for efficiently supporting these power levels, specialized output stages are necessary

## Power Amplifier Characteristics

- Can drive a small "heavy" load resistance

- Example: Speaker resistance can be  $4-16\Omega$

- Delivers large current levels

- Often in the hundreds of mA

- Requires large voltage swings

- Draws a large amount of power from the supplies

- Dissipates a large amount of power, and thus can get hot

Example: Delivering 1W to an  $8\Omega$  speaker

Sinusoidal

$$P_{out} = \left(\frac{V_P}{\sqrt{2}}\right)^2 \cdot \frac{1}{R_L} = 1W$$

This results in a peak voltage

$$V_P = 4V$$

and a peak current

$$I_P = \frac{V_P}{R_L} = \frac{4V}{8\Omega} = 500 mA$$

## Power Amplifier Performance Metrics

- Linearity or Distortion

- Audio amplifiers must have low distortion to reproduce music with high fidelity

- Power Efficiency

$$\eta = \frac{\text{Power Delivered to Load}}{\text{Power Drawn from Supply}}$$

- Maximum Voltage Rating

- May require high power supplies

- Transistors must have sufficiently high breakdown voltages

## Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

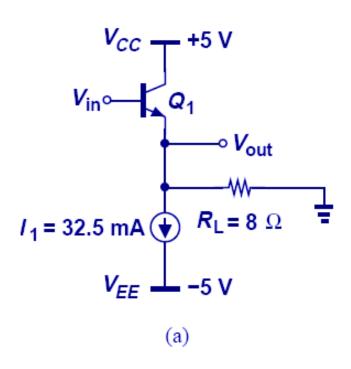

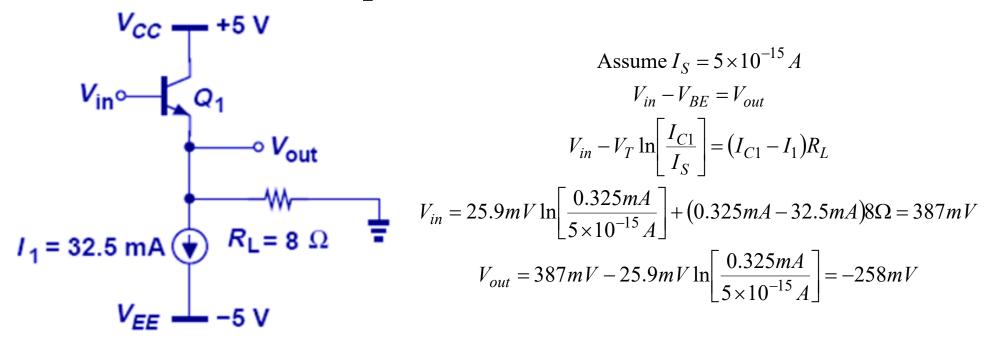

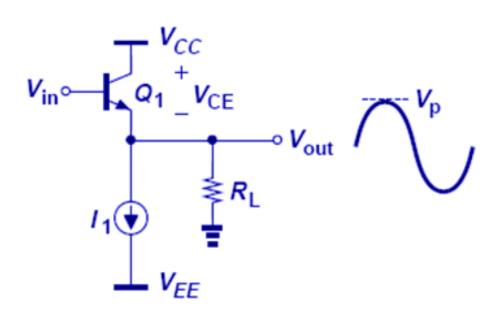

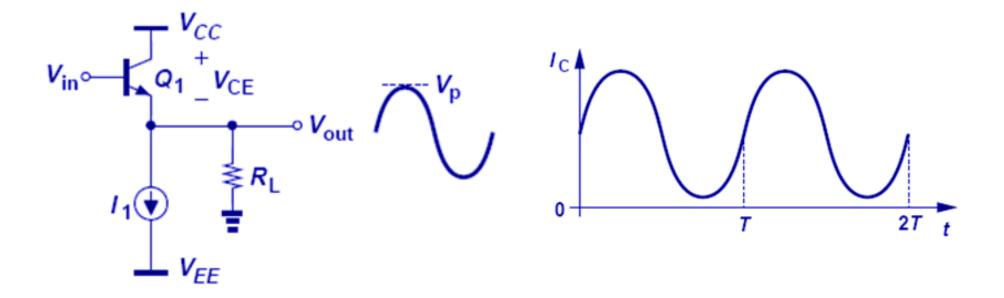

## Emitter Follower Large-Signal Behavior: Positive Half-Cycle

Here  $V_{BE}$  is assumed to be 0.8V due to the high current levels

- As V<sub>in</sub> increases V<sub>out</sub> also follows and Q₁ provides more current

- No major issue with the input signal positive half-cycle

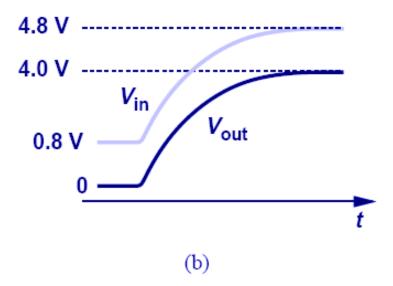

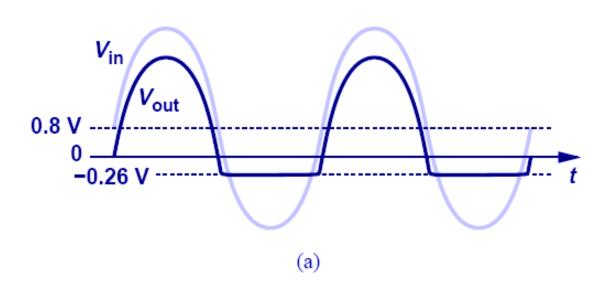

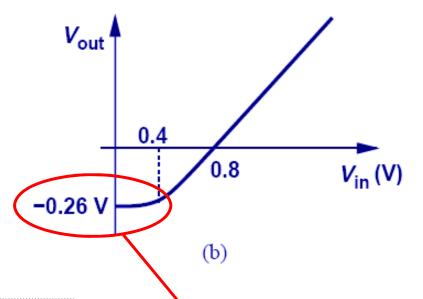

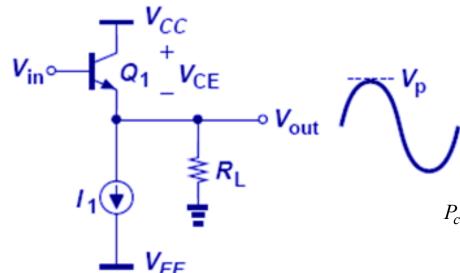

## Emitter Follower Large-Signal Behavior: Negative Half-Cycle

- However as V<sub>in</sub> decreases, V<sub>out</sub> also decreases, shutting off Q<sub>1</sub> and resulting in a constant V<sub>out</sub>

- The output signal clips at a minimum value of –I₁R₁

#### **Example: Emitter Follower**

What are the input and output voltages when I<sub>C1</sub> drops to 1% of I<sub>1</sub>?

- At this current level, the V<sub>BE</sub> has dropped to 645mV

- For voltage levels much below 400mV, the output will saturate at  $-I_1R_1 = -260$ mV

#### **Linearity of an Emitter Follower**

- As Vin decreases the output waveform will be clipped, introducing nonlinearity in I/O characteristics

- ➤ Overall, the fixed I₁ limits the output swing

## Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

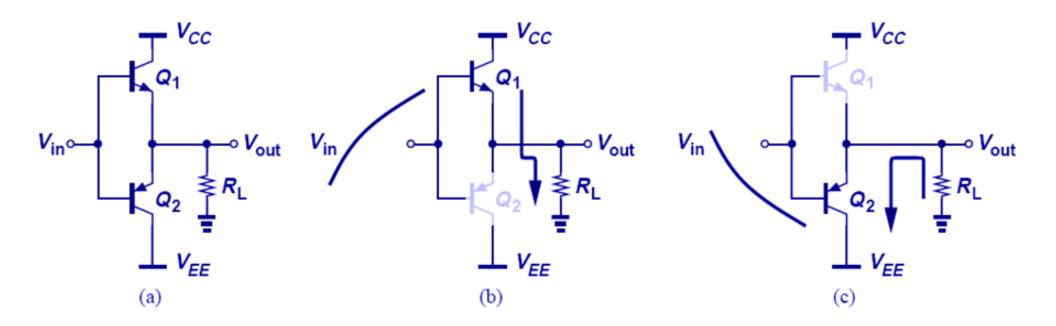

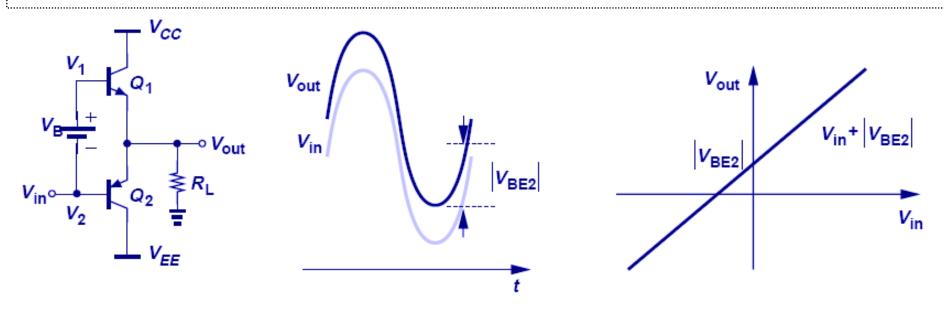

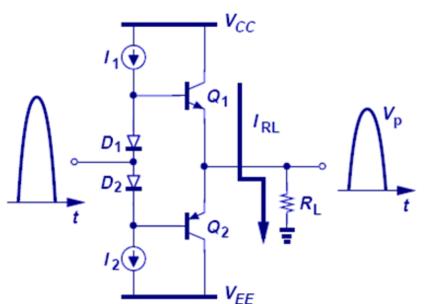

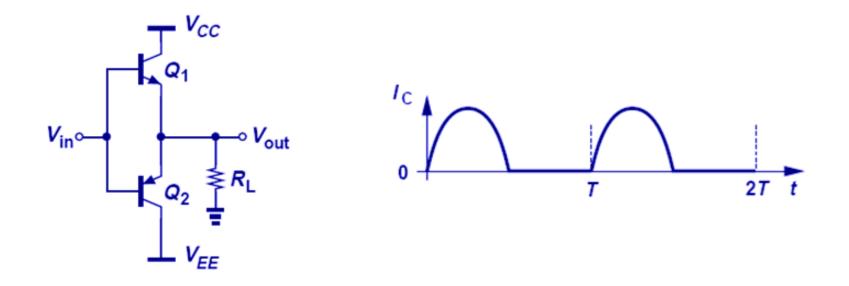

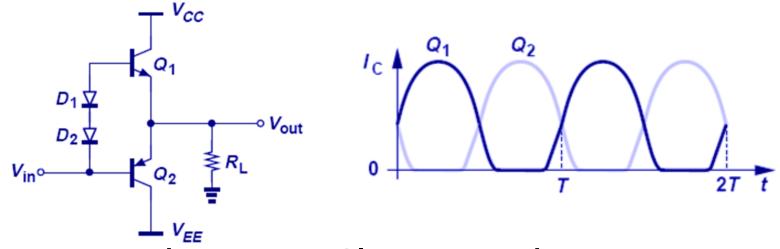

#### **Push-Pull Stage**

- As V<sub>in</sub> increases, Q<sub>1</sub> is on and pushes a current into R<sub>L</sub>.

- $\triangleright$  As  $V_{in}$  decreases,  $Q_2$  is on and pulls a current out of  $R_L$ .

- For positive  $V_{in}$ ,  $Q_1$  shifts the output down and for negative  $V_{in}$ ,  $Q_2$  shifts the output up.

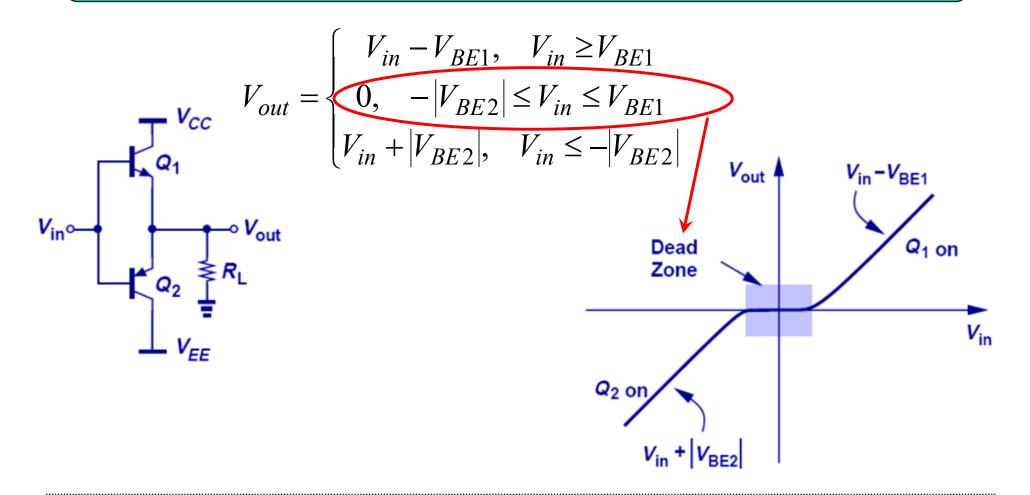

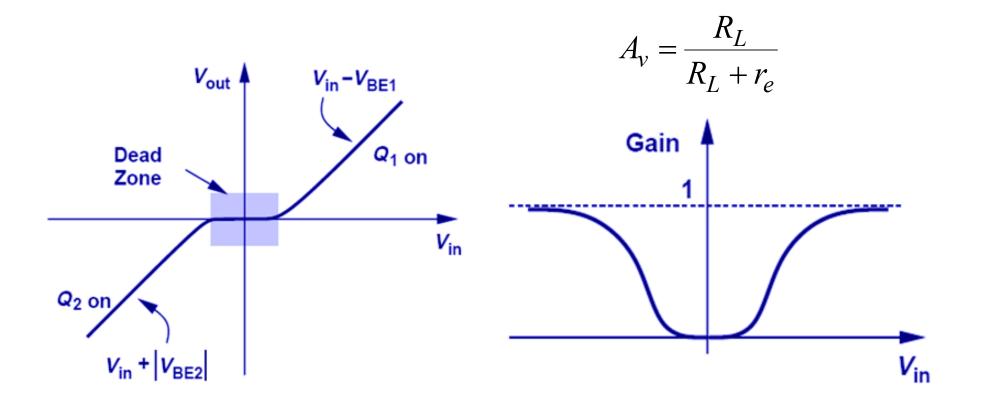

#### Overall I/O Characteristics of Push-Pull Stage

- ightharpoonup However, for small  $V_{in}$ , there is a dead zone (both  $Q_1$  and  $Q_2$  are off) in the I/O characteristic, resulting in gross nonlinearity

- The dead zone is from -|V<sub>BE2</sub>| ≤ V<sub>in</sub> ≤ V<sub>BE1</sub>

#### **Small-Signal Gain of Push-Pull Stage**

- The push-pull stage exhibits a gain that tends to unity when either Q1 or Q2 is on.

- When Vin is very small, the gain drops to zero.

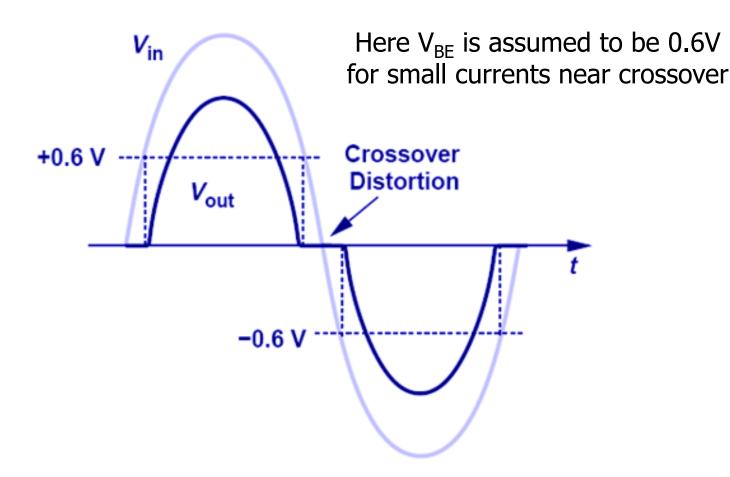

#### Sinusoidal Response of Push-Pull Stage

For large Vin, the output follows the input with a fixed DC offset, however as Vin becomes small the output drops to zero and causes "Crossover Distortion."

## Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

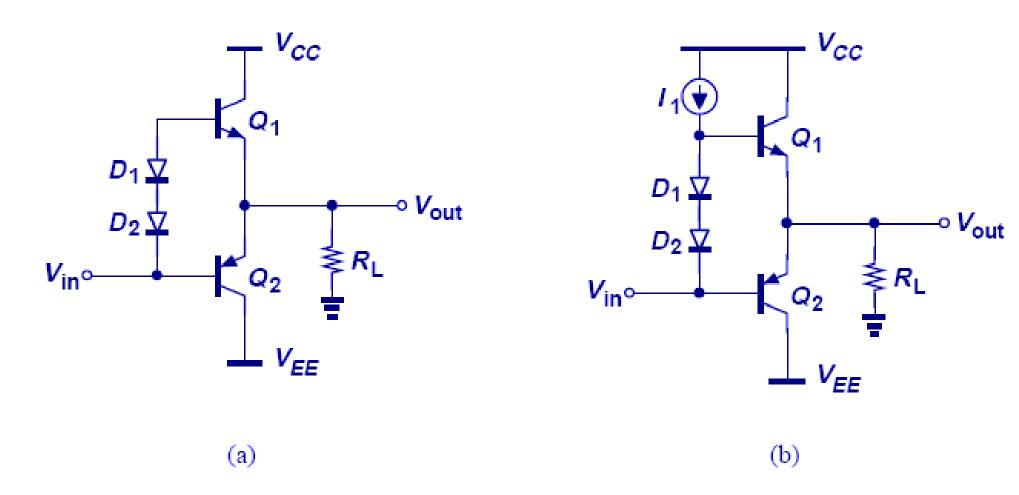

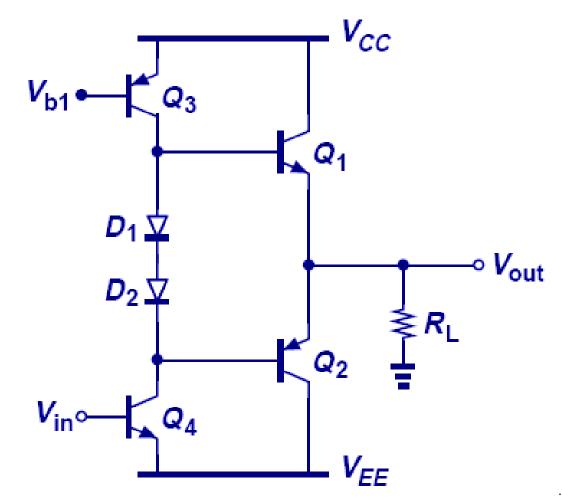

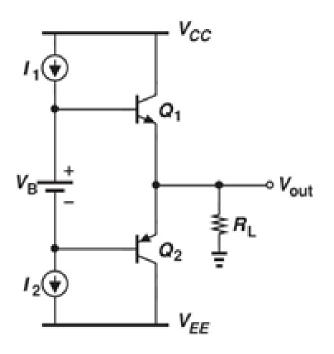

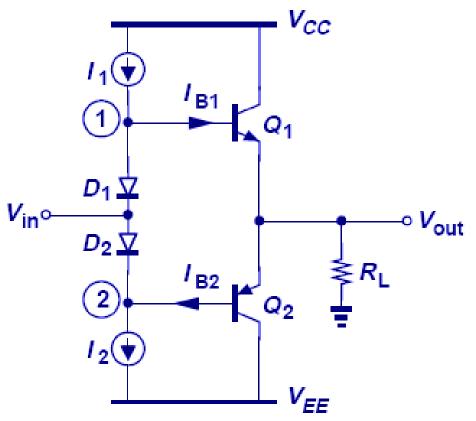

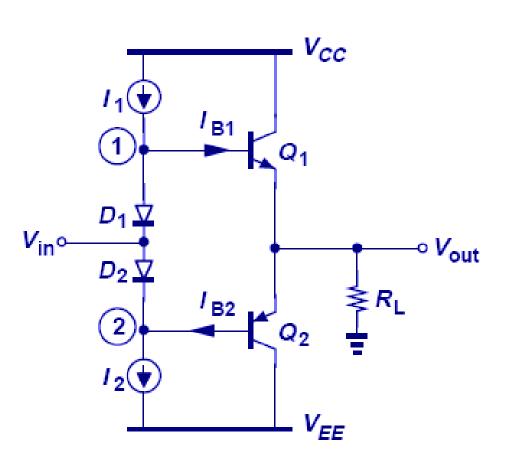

#### **Improved Push-Pull Stage**

With a battery of  $V_B$  inserted between the bases of  $Q_1$  and  $Q_2$ , the dead zone is eliminated.

What should  $V_B$  be so that at least one transistor is always on?

$$Q_2$$

turns off when  $V_{in} = -|V_{BE2}|$

at this point we want  $Q_1$  on, or  $V_1 = V_{BE1}$

Thus,

$$V_B = V_1 - V_{in} = V_{BE1} - (-|V_{BE2}|)$$

$$V_B = V_{BE1} + \left| V_{BE2} \right|$$

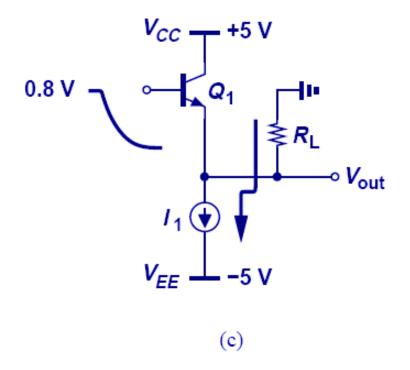

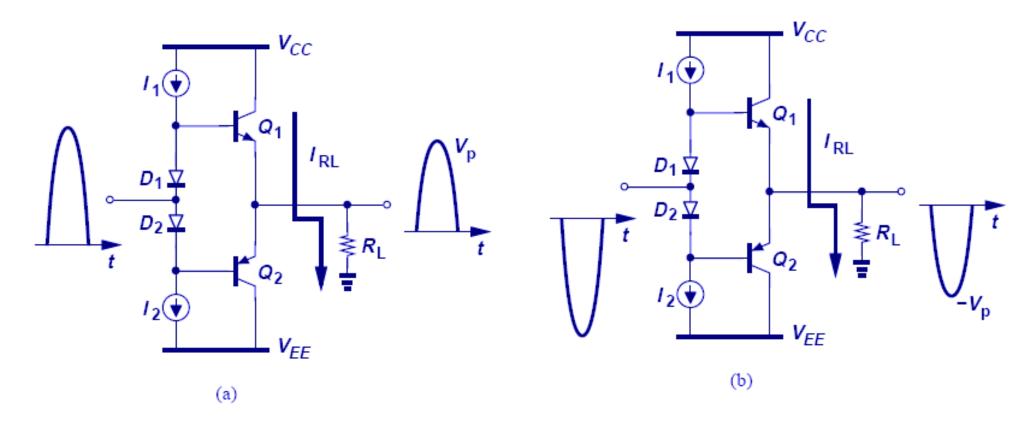

#### Implementation of V<sub>B</sub>

- Since V<sub>B</sub>=V<sub>BE1</sub>+|V<sub>BE2</sub>|, a natural choice would be two series diodes

- $\triangleright$  I<sub>1</sub> in figure (b) is used to bias the diodes and Q<sub>1</sub>.

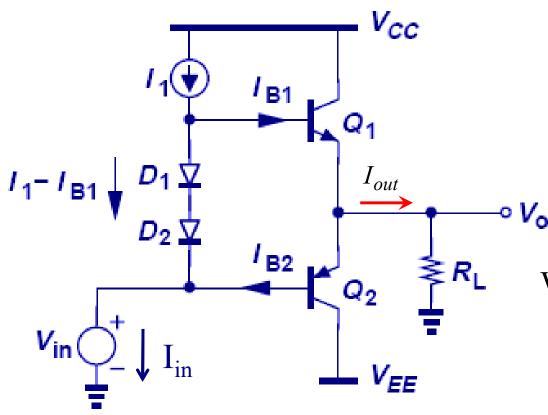

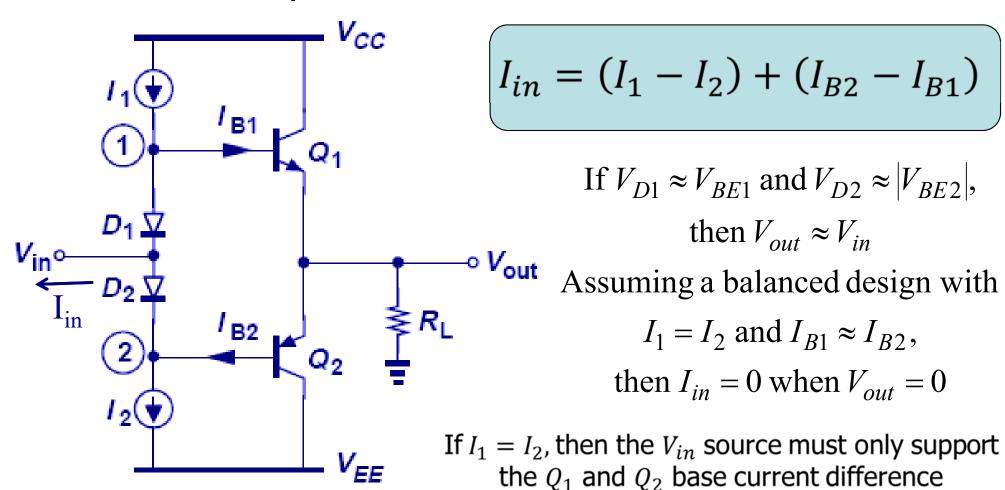

#### **Example: Current Flow I**

The  $V_{in}$  source must support  $I_1$  and the  $Q_1$  and  $Q_2$  base current difference, which can excessively load the source

$$I_{in} = I_1 - I_{B1} + I_{B2}$$

When is  $I_{in} = I_1$ , assuming  $\beta_1 = \beta_2$ ? This occurs when  $I_{B1} = I_{B2}$ , which implies that  $I_{C1} = I_{C2}$ and that  $I_{out} = 0$ Thus, this occurs when

$V_{out} = 0$

#### **Example: Current Flow II**

The offset between input and output is minimized when the input is in the middle of the diodes

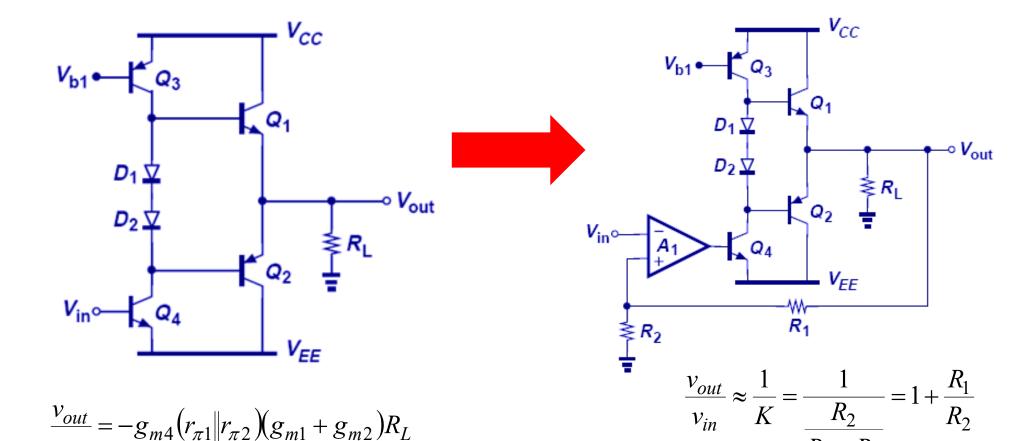

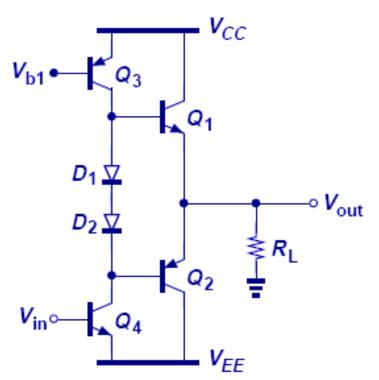

#### **Addition of CE Stage**

- $\triangleright$  A CE stage (Q<sub>4</sub>) is added to provide voltage gain from the input to the bases of Q<sub>1</sub> and Q<sub>2</sub>

- This push-pull circuit is often used in high-power output stages

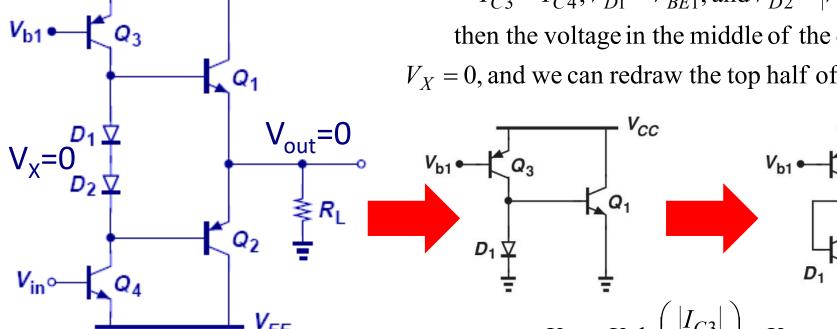

#### **Bias Point Analysis**

With  $V_{out} = 0$  and assuming that

$$I_{C3} = I_{C4}, V_{D1} = V_{BE1}, \text{ and } V_{D2} = |V_{BE2}|$$

then the voltage in the middle of the diodes

$V_X = 0$ , and we can redraw the top half of the circuit

- $V_{D1} = V_T \ln \left( \frac{|I_{C3}|}{I_{S,D1}} \right) = V_{BE1} = V_T \ln \left( \frac{I_{C1}}{I_{S,D1}} \right)$

- $I_{C1} = \left(\frac{I_{S,Q1}}{I_{S,D1}}\right) I_{C3}$

- For bias point analysis, the circuit can be simplified to the one on the right, which resembles a current mirror

- For a well-defined I<sub>S</sub> ratio, D₁ can be realized as a diode-connected transistor

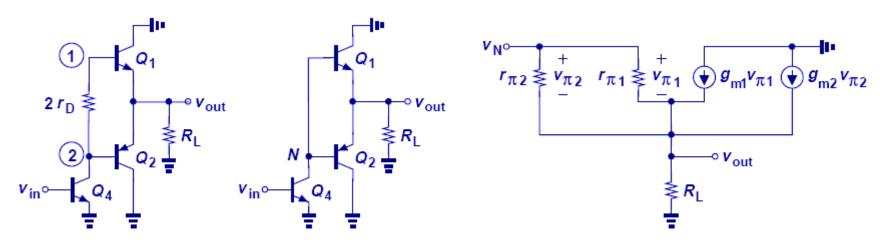

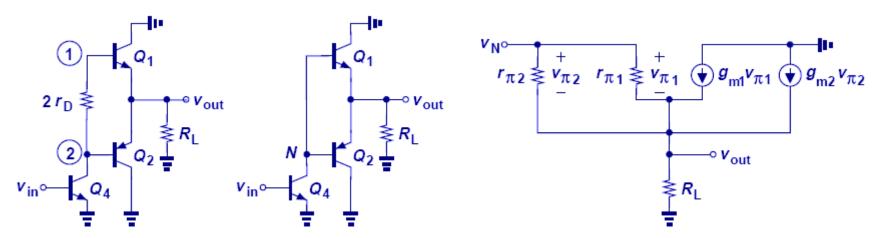

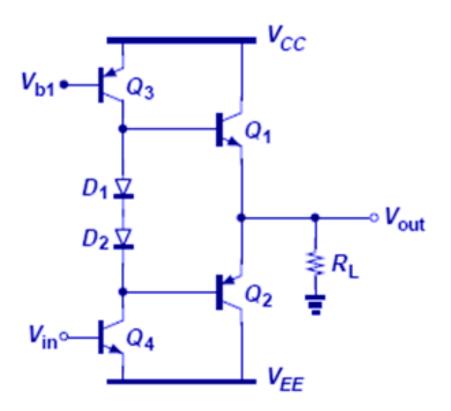

#### **Small-Signal Analysis - I**

In order to derive the gain of the circuit, we can treat it as a two-stage amplifier

$$\frac{v_{out}}{v_{in}} = \frac{v_N}{v_{in}} \cdot \frac{v_{out}}{v_N}$$

Assuming  $V_A = \infty$  and  $r_D = 0$ , the second stage can be viewed as 2 parallel emitter followers

$$\frac{v_{out}}{v_N} = \frac{R_L}{R_L + r_{e1} \| r_{e2}} \approx \frac{R_L}{R_L + \frac{1}{g_{m1} + g_{m2}}}$$

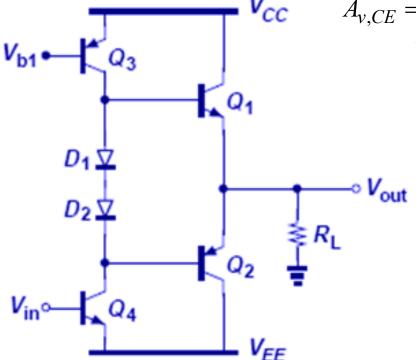

#### **Small-Signal Analysis - II**

The gain of the first stage can be expressed as

$$\frac{v_N}{v_{in}} = -g_{m4}R_N \text{ where}$$

$$R_N = r_{\pi 1} || r_{\pi 2} + (g_{m1} + g_{m2})(r_{\pi 1} || r_{\pi 2}) R_L$$

The overall gain is

$$\frac{v_{out}}{v_{in}} = \frac{v_N}{v_{in}} \cdot \frac{v_{out}}{v_N} = -g_{m4} \left[ r_{\pi 1} \| r_{\pi 2} + (g_{m1} + g_{m2})(r_{\pi 1} \| r_{\pi 2}) R_L \right] \frac{R_L}{R_L + \frac{1}{g_{m1} + g_{m2}}}$$

$\frac{v_{out}}{v_{in}} = -g_{m4}(r_{\pi 1}||r_{\pi 2})(g_{m1} + g_{m2})R_L$

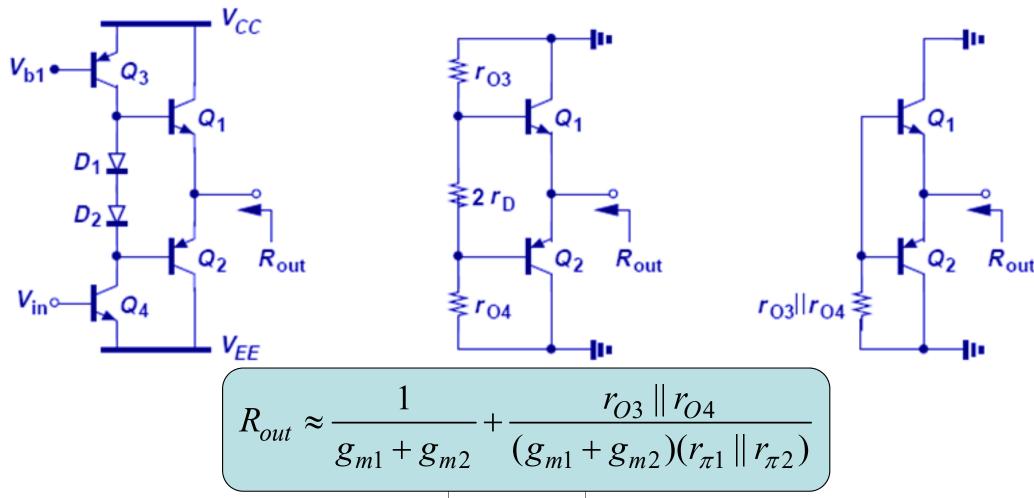

#### **Output Resistance Analysis**

For the output resistance, we do need to consider the finite r<sub>0</sub> of Q<sub>3</sub> & Q<sub>4</sub>

If β is low, the second term of the output resistance will rise, which will be problematic when driving a small resistance.

## Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

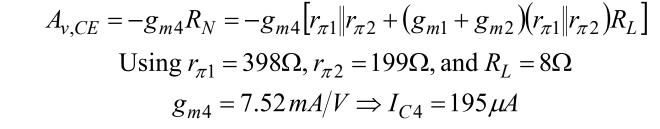

#### **Example: Biasing**

Design Specs:

Common Emitter  $A_v = 5$

Output Stage  $A_v = 0.8$

with

$$R_L = 8\Omega$$

,  $\beta_{npn} = 2\beta_{pnp} = 100$

and assume  $I_{C1} \approx I_{C2}$

1. From the output stage gain and  $I_{C1,2}$  conditions we can find  $g_{m1,2}$  and  $I_{C1,2}$

$$A_{v,OS} = \frac{v_{out}}{v_N} = \frac{R_L}{R_L + \frac{1}{g_{m1} + g_{m2}}} = 0.8$$

$$g_{m1} + g_{m2} = \frac{1}{2\Omega}$$

with

$$I_{C1} = I_{C2} \Rightarrow g_{m1} = g_{m2} = \frac{1}{4} (\Omega^{-1}) = 250 \, mA/V$$

and  $I_{C1} = I_{C2} = 6.5 \, mA$

#### **Example: Biasing**

2. From the Common Emitter gain condition we can find  $I_{C4}$

However, this design procedure neglects any output swing specification!

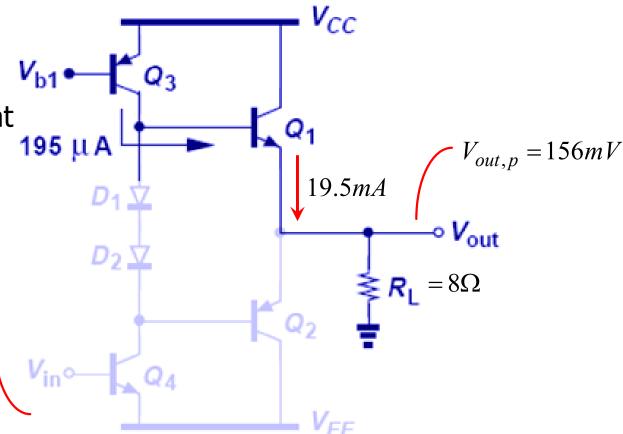

#### **Problem of Base Current**

Note, this assumes that  $I_{C3}$  is the same as  $I_{C4}$ , which may not exactly be the case due to the different  $\beta_{1,2}$

$\triangleright$  195 μA of base current in Q<sub>1</sub> can only support 19.5 mA of collector current, insufficient for high current operation (hundreds of mA).

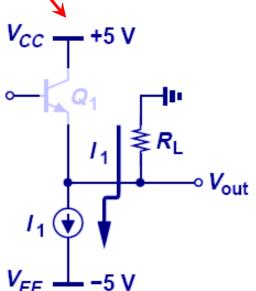

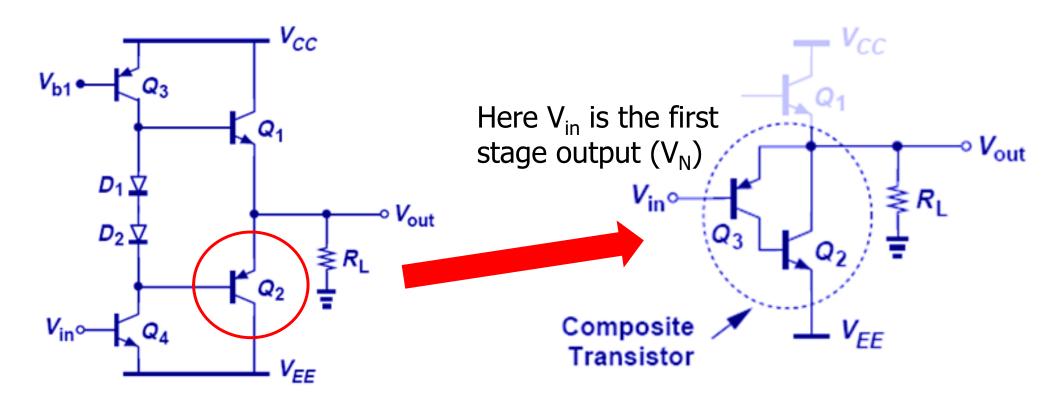

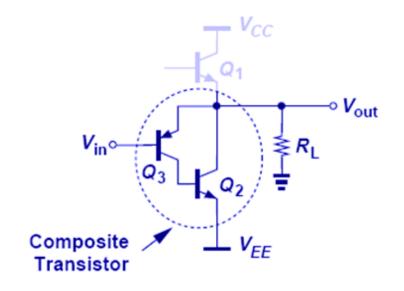

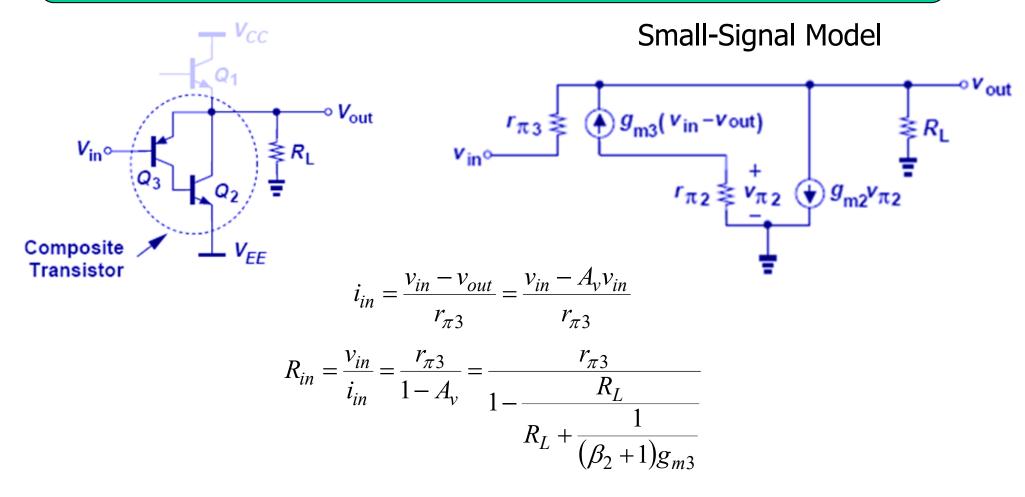

#### **Modification of the PNP Emitter Follower**

- Another output stage issue is that the  $Q_2$  PNP transistor typically have low current gain ( $\beta$ ) and low  $f_T$

- Using a composite transistor consisting of an emitter follower PNP ( $Q_3$ ) and a common emitter NPN ( $Q_2$ ) allows for improved performance

## Modified PNP Emitter Follower Gain & Output Resistance

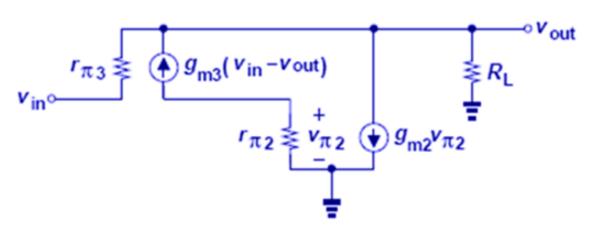

#### **Small-Signal Model**

Writing a KCL at the output node

$$\frac{v_{out} - v_{in}}{r_{\pi 3}} - g_{m3}(v_{in} - v_{out}) + g_{m2}(-g_{m3})(v_{in} - v_{out})r_{\pi 2} + \frac{v_{out}}{R_L} = 0$$

As the  $Q_3$  collector current forms the  $Q_2$  base current

$$g_{m2} = \beta_2 g_{m3}$$

$$\frac{v_{out}}{v_{in}} = \frac{R_L}{R_L + \frac{1}{(\beta_2 + 1)g_{m3} + \frac{1}{r_{\pi 3}}}}$$

$$R_{out} = \frac{1}{(\beta_2 + 1)g_{m3} + \frac{1}{r_{\pi 3}}} \approx \frac{1}{(\beta_2 + 1)g_{m3}}$$

Output resistance has been reduced by  $\beta_2$ +1 factor 32

## Modified PNP Emitter Follower Input Resistance

$$R_{in} = r_{\pi 3} + \beta_3 (\beta_2 + 1) R_L$$

Input resistance has been increased by  $\sim(\beta_2+1)$  factor

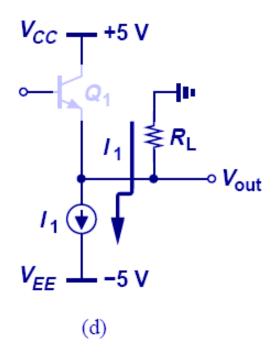

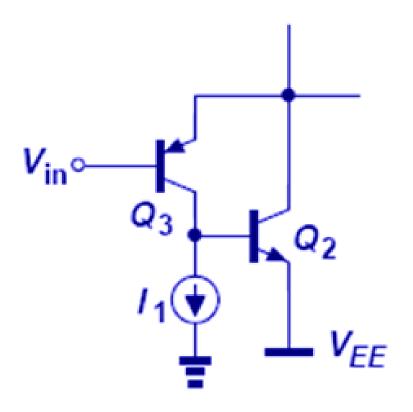

#### **Additional Bias Current**

- Q<sub>2</sub> is often a large transistor to support the output current levels, resulting in large base capacitance

- ▶ I₁ is added to the base of Q₂ to provide an additional bias current to Q₃ so the capacitance at the base of Q₂ can be charged/discharged quickly

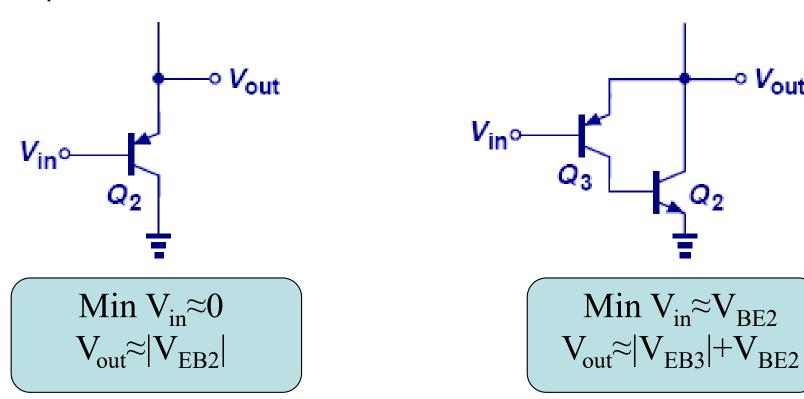

#### **Example: Minimum V**<sub>in</sub>

- There is a minimum Vin for which the effective emitter follower transistors remain in active mode

- Here we conservatively assume for active mode we need a min. V<sub>BC</sub>=0V

Simple PNP Emitter Follower

Modified PNP Emitter Follower

The modified PNP emitter follower has a reduced input range by V<sub>BE2</sub>

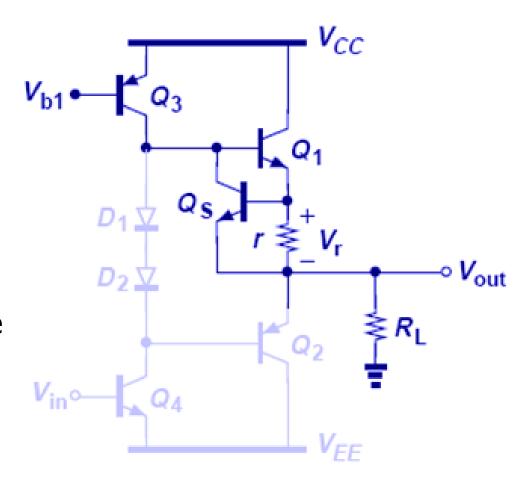

#### HiFi Design

As g<sub>m1</sub> and g<sub>m2</sub> vary dramatically during large signal operation, the circuit displays nonlinear distortion  Placing the output stage in a negative feedback loop allows for a more constant gain, and thus better linearity

#### **Short-Circuit Protection**

- Excessive output stage current can result if the output is shorted to ground, damaging the circuit

- Q<sub>s</sub> and r are used to "steal" some base current away from Q<sub>1</sub> when the output is accidentally shorted to ground, preventing short-circuit damage

- Drawbacks

- r increases output resistance

- Voltage drop across r reduces maximum output swing

### Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

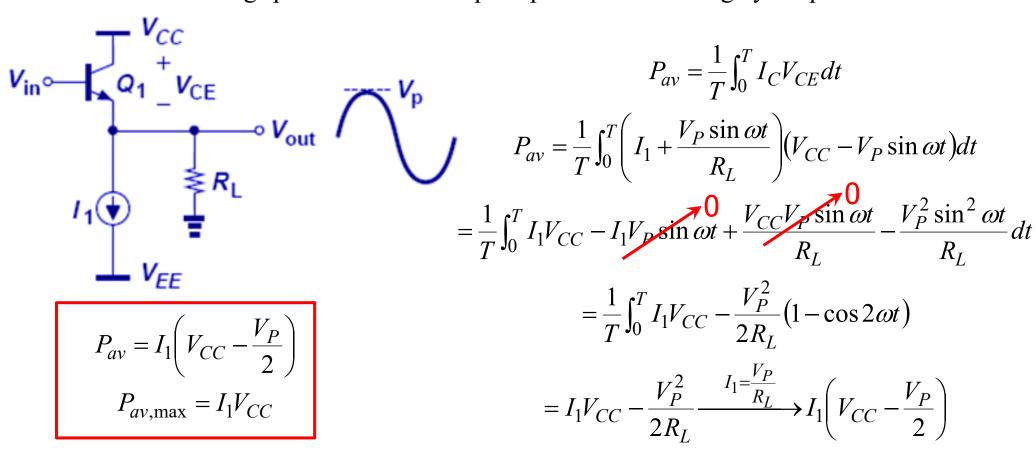

#### **Emitter Follower Power Rating**

The average power dissipated by  $Q_1$  can be calculated by integrated the current - voltage product over a complete period and dividing by the period time.

➤ Maximum power dissipated across Q<sub>1</sub> occurs in the *absence* of a signal.

#### **Example: Current Source Power Dissipation**

The power dissipated by the I<sub>1</sub> current source is also important, as it will

ultimately need to be realized at the transistor level also

Note that the I₁ power is positive, as V<sub>FF</sub> is a negative supply

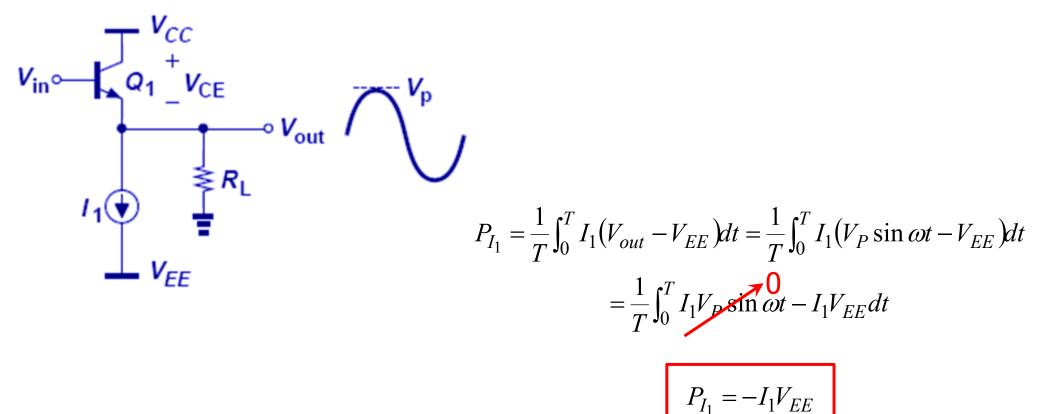

#### **Push-Pull Stage Power Rating**

Assuming a symmetric design, the power ratings of Q1 and Q2 are the same and can be computed by integrating over a half-period.

#### **Push-Pull Stage Power Rating**

$$P_{av} = \frac{1}{T} \int_0^{T/2} V_{CE} I_C dt = \frac{1}{T} \int_0^{T/2} \left( V_{CC} - V_P \sin \omega t \right) \left( \frac{V_P}{R_L} \sin \omega t \right) dt$$

$$= \frac{1}{T} \int_{0}^{T/2} \frac{V_{CC}V_{P}}{R_{L}} \sin \omega t - \frac{V_{P}^{2}}{R_{L}} \sin^{2} \omega t dt$$

$$= \frac{1}{T} \int_{0}^{T/2} \frac{V_{CC}V_{P}}{R_{L}} \sin \omega t dt - \frac{1}{T} \int_{0}^{T/2} \frac{V_{P}^{2}}{2R_{L}} (1 - \cos 2\omega t) dt$$

$$= \frac{V_{CC}V_{P}}{\pi R_{L}} - \frac{V_{P}^{2}}{4R_{L}}$$

$$P_{av} = \frac{V_P}{R_L} \left( \frac{V_{CC}}{\pi} - \frac{V_P}{4} \right)$$

Maximum power occurs with

$$V_P = \frac{2V_{CC}}{\pi}$$

$$P_{av,\text{max}} = \frac{V_{CC}^2}{\pi^2 R_L}$$

#### Example: Push-Pull Pav

$$P_{av} = \frac{V_P}{R_L} \left( \frac{V_{CC}}{\pi} - \frac{V_P}{4} \right)$$

If

$$V_p = 4V_{CC}/\pi \rightarrow P_{av}=0$$

Impossible since  $V_p$  cannot go above supply  $(V_{CC})$

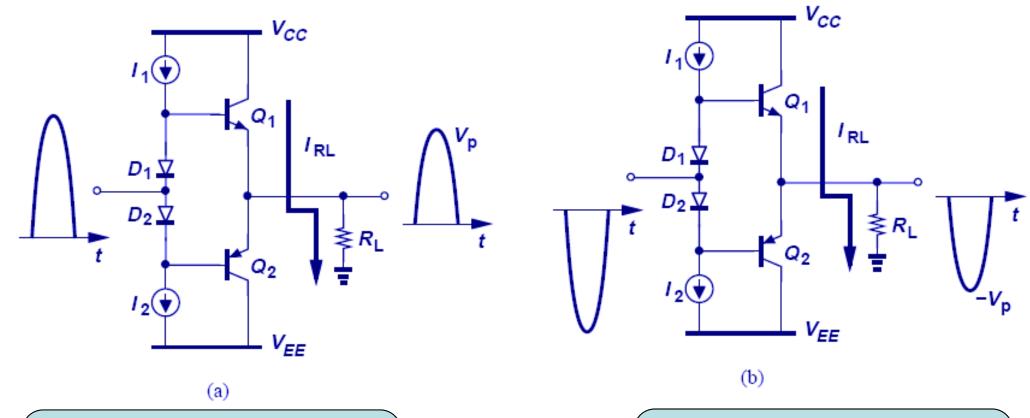

#### **Heat Sink**

Heat sink, provides large surface area to dissipate heat from the chip.

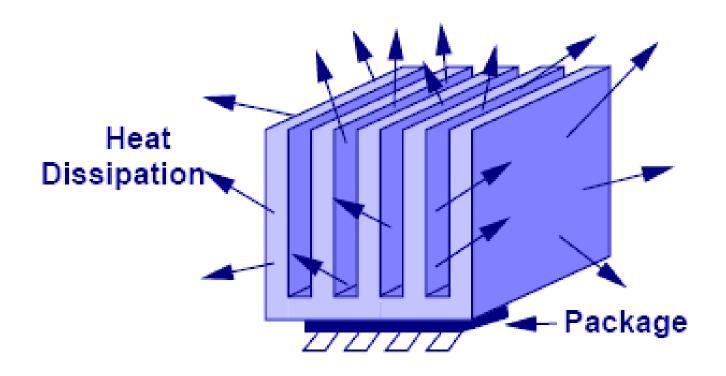

#### **Thermal Runaway**

- For a constant I<sub>C</sub>, V<sub>BE</sub> has a negativeto-absolute-temperature (NTAT) coefficient of approximately -2mV/°K

- Conversely, if the push-pull output stage is biased with a constant voltage, the current will increase with temperature

- This increased current results in more heat (higher temperature), and thus more current

- This positive feedback loop is called thermal runaway and can result in transistor damage

#### **Thermal Runaway Mitigation**

• Assuming that  $Q_3$  and  $Q_4$  have relatively constant bias currents with temperature (using good current mirror techniques), the diode voltages drop with temperature

Diode Voltages

$$V_{D1} + V_{D2} = V_T \ln \frac{I_{D1}}{I_{S,D1}} + V_T \ln \frac{I_{D2}}{I_{S,D2}} = V_T \ln \frac{I_{D1}I_{D2}}{I_{S,D1}I_{S,D2}}$$

Transistor  $V_{BE}$  Voltages

$$V_{BE1} + V_{BE2} = V_T \ln \frac{I_{C1}}{I_{S,Q1}} + V_T \ln \frac{I_{C2}}{I_{S,Q2}} = V_T \ln \frac{I_{C1}I_{C2}}{I_{S,Q1}I_{S,Q2}}$$

From a KVL, these voltage pairs are the same

$$V_T \ln \frac{I_{D1}I_{D2}}{I_{S,D1}I_{S,D2}} = V_T \ln \frac{I_{C1}I_{C2}}{I_{S,Q1}I_{S,Q2}}$$

$$\frac{I_{D1}I_{D2}}{I_{S,D1}I_{S,D2}} = \frac{I_{C1}I_{C2}}{I_{S,Q1}I_{S,Q2}}$$

Using diode biasing prevents thermal runaway since the currents in  $Q_1$  and  $Q_2$  will track those of  $D_1$  and  $D_2$  as long as their  $I_s$ 's track with temperature.

### Agenda

- General Output Stage Considerations

- Emitter Follower as a Power Amplifier

- Push-Pull Stage

- Improved Push-Pull Stage

- Large-Signal Considerations

- Heat Dissipation

- Efficiency and Power Amplifier Classes

### Power Amplifier Efficiency

Power amplifier efficiency is critical because PAs draw a significant amount of power from the supply voltages

Power amplifier efficiency is the ratio of the average power delivered to the load over the total power consumed from the supplies

$$\eta = \frac{\text{Power Delivered to Load}}{\text{Power Drawn from Supply}} = \frac{P_{out}}{P_{out} + P_{ckt}}$$

### **Emitter Follower Efficiency**

The average power delivered to the load is

$$P_{out} = \frac{V_P^2}{2R_L}$$

The average power consumed by  $Q_1$  is

$$P_{Q_1} = I_1 \left( V_{CC} - \frac{V_P}{2} \right)$$

The average power consumed by  $I_1$  is

$$P_{I_1} = -I_1 V_{EE} = I_1 V_{CC}$$

with  $V_{EE} = -V_{CC}$

Thus the total average circuit power is

$$P_{ckt} = I_1 \left( V_{CC} - \frac{V_P}{2} \right) + I_1 V_{CC} = I_1 \left( 2V_{CC} - \frac{V_P}{2} \right)$$

- The Emitter Follower Efficiency is  $\eta_{EF} = \frac{\frac{V_P^2}{2R_L}}{\frac{V_P^2}{2R_L} + I_1 \left(2V_{CC} \frac{V_P}{2}\right)}$  The emitter follower out stage only has a peak efficiency of 25% as  $V_P$  goes to  $V_{CC}$

- with  $I_1 = \frac{V_P}{R_L}$   $\Rightarrow$   $\eta_{EF} = \frac{V_P}{4V_{CC}}$

- The emitter follower output

- Note, this can't actually be achieved, as we need some V<sub>CF</sub> and voltage across I<sub>1</sub>

## Emitter Follower Efficiency Example

• What if the emitter follower is designed to deliver  $V_p$ , but only operates with  $V_p = V_{CC}/2$ ?

Now the average power delivered to the load is

$$P_{out} = \frac{\left(\frac{V_P}{2}\right)^2}{2R_L} = \frac{V_P^2}{8R_L}$$

The total average circuit power becomes

$$P_{ckt} = I_1 \left( 2V_{CC} - \frac{V_P}{4} \right) = \frac{2V_P^2}{R_L} - \frac{V_P^2}{4R_L} \text{ with } I_1 = \frac{V_P}{R_L} \text{ and } V_{CC} = V_P$$

$$\eta_{EF} = \frac{\frac{V_P^2}{8R_L}}{\frac{V_P^2}{8R_L} + \frac{2V_P^2}{R_L} - \frac{V_P^2}{4R_L}} = \frac{1}{15}$$

Now the efficiency drops to only 6.7%

# Push-Pull Stage Efficiency

The average power delivered to the load is

$$P_{out} = \frac{V_P^2}{2R_L}$$

Both  $Q_1$  and  $Q_2$  consume an average power of

$$P_{Q_{1,2}} = \frac{V_P}{R_L} \left( \frac{V_{CC}}{\pi} - \frac{V_P}{4} \right)$$

- The push-pull output stage has a peak efficiency of 78.5% as  $V_P$  goes to  $V_{CC}$

- Also, we are excluding the input bias stage

The Push - Pull Stage Efficiency is  $\eta_{PP} = \frac{\frac{V_P}{2R_L}}{\frac{V_P^2}{2R_L} + \frac{2V_P}{R} \left( \frac{V_{CC}}{\pi} - \frac{V_P}{4} \right)}$ Note, uns can caccam, achieved, as we need some  $V_{CE}$  across both  $V_{CE}$  and  $V_{CE}$  across both  $V_{CE}$  and  $V_{CE}$  across both  $V_{CE}$  and  $V_{CE}$

$$\eta_{PP} = \frac{\pi V_P}{4V_{CC}}$$

## Total Push-Pull Stage Efficiency

Assume that I<sub>1</sub>=I<sub>2</sub> and that they are chosen to allow a peak swing of V<sub>P</sub>

In order to support a peak swing of  $V_P$

$$I_1 = \frac{V_P}{\beta R_L}$$

The input bias stage power is

$$\frac{2V_{CC}V_P}{\beta R_L}$$

Thus the total push - pull stage efficiency is

$$\eta_{PP} = \frac{\frac{V_{P}^{2}}{2R_{L}}}{\frac{2V_{P}V_{CC}}{\pi R_{L}} + \frac{2V_{CC}V_{P}}{\beta R_{L}}}$$

$$\eta_{PP} = \frac{1}{4} \left( \frac{V_P}{\frac{V_{CC}}{\pi} + \frac{V_P}{\beta}} \right)$$

### Class A Power Amplifiers

- Each transistor is on for the entire cycle

- Emitter follower is a Class A power amplifier

Display high linearity, but low efficiency (25% maximum)

### Class B Power Amplifiers

- Each transistor conducts for half the cycle

- Simple push-pull stage is a Class B power amp

- Display high efficiency, but low linearity

- Bad crossover distortion

### Class AB Power Amplifiers

- Each transistor conducts for slightly more than a half-cycle

- Improved push-pull stage is a Class AB power amp

- Compromise between Class A and B

- Good distortion at slightly degraded efficiency

- Many other PA classes exist (C, D, E, ...) and are often studied in grad-level RF circuit design classes

#### Thanks for the fun semester!!!