### ECEN326: Electronic Circuits Spring 2022

Lecture 4: Cascode Stages and Current Mirrors

Sam Palermo Analog & Mixed-Signal Center Texas A&M University

### Announcements

- HW4 due Mar 8

- Reading

- Razavi Chapter 9

• Cascode Stages

• Current Mirrors

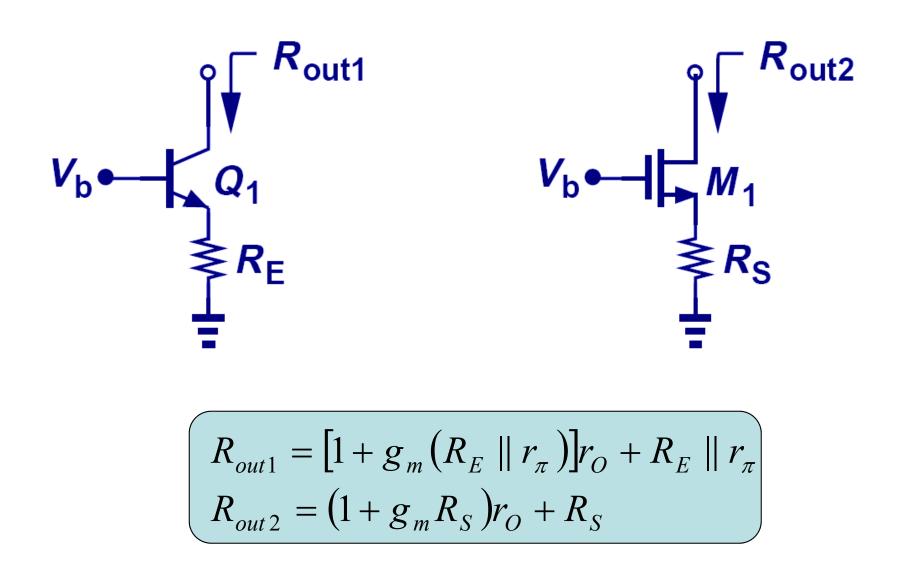

### **Boosted Output Impedances**

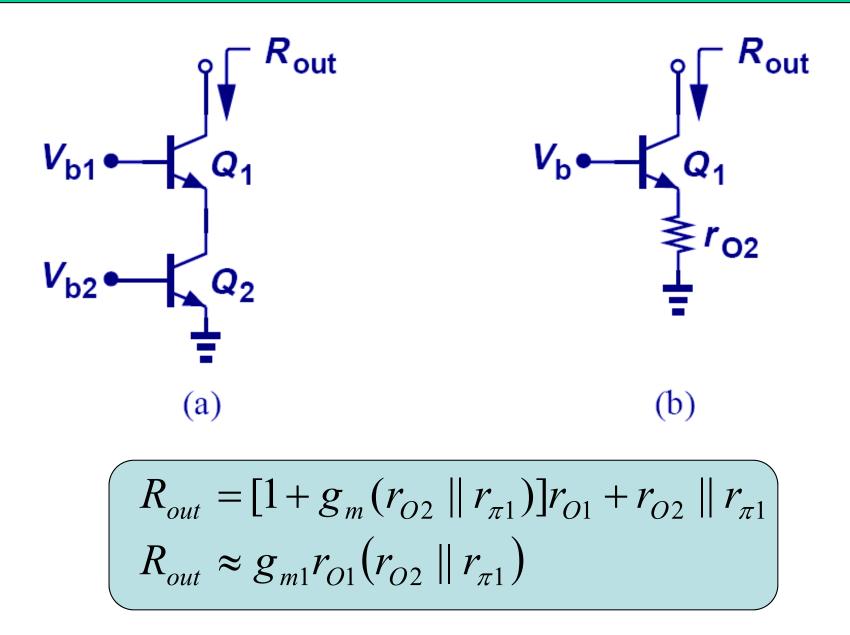

### **Bipolar Cascode Stage**

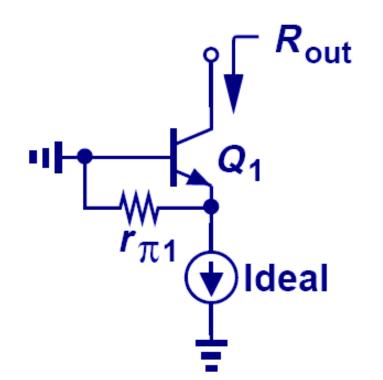

### Maximum Bipolar Cascode Output Impedance

$R_{out,\max} \approx g_{m1} r_{O1} r_{\pi 1}$  $R_{out,\max} \approx \beta_1 r_{O1}$

#### The maximum output impedance of a bipolar cascode is bounded by the ever-present r<sub>π</sub> between emitter and ground of Q<sub>1</sub>.

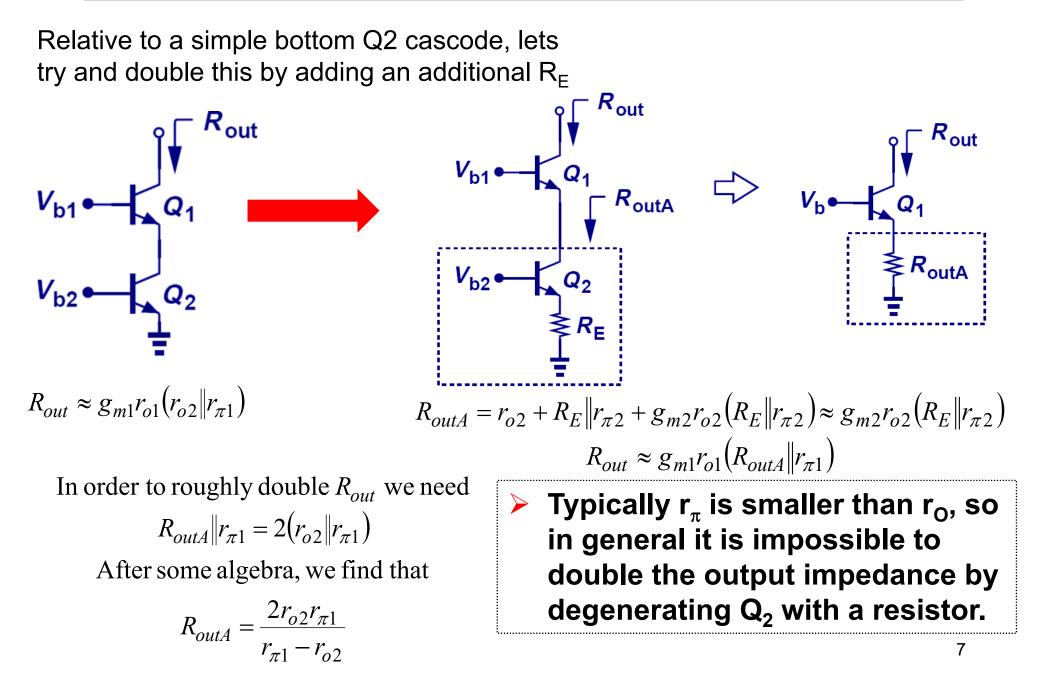

# Example: Trying to Double Output Impedance using R<sub>E</sub>

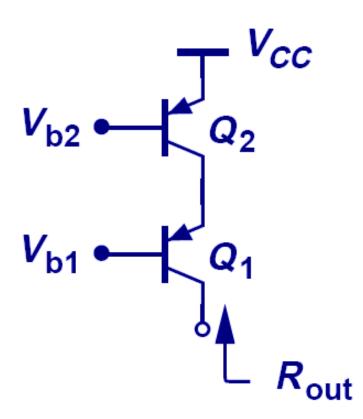

### **PNP Cascode Stage**

$$\begin{aligned} R_{out} &= [1 + g_m (r_{O2} \parallel r_{\pi 1})] r_{O1} + r_{O2} \parallel r_{\pi 1} \\ R_{out} &\approx g_{m1} r_{O1} (r_{O2} \parallel r_{\pi 1}) \end{aligned}$$

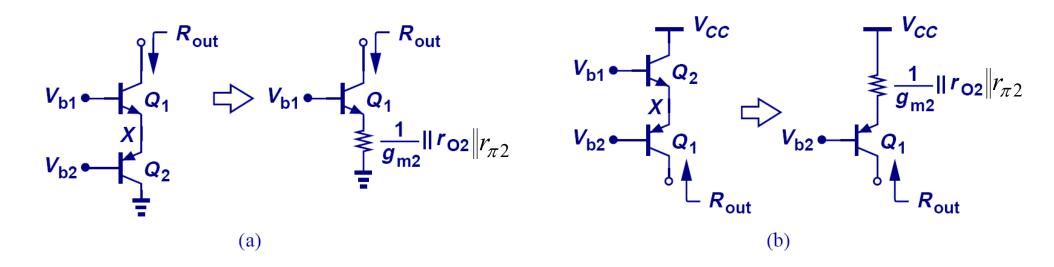

### **Another Interpretation of Bipolar Cascode**

$$V_{b2} \leftarrow Q_{2}$$

$$V_{b1} \leftarrow Q_{1}$$

$$V_{b2} \leftarrow Q_{2}$$

$$V_{b2} \leftarrow Q_{2}$$

$$V_{b2} \leftarrow Q_{2}$$

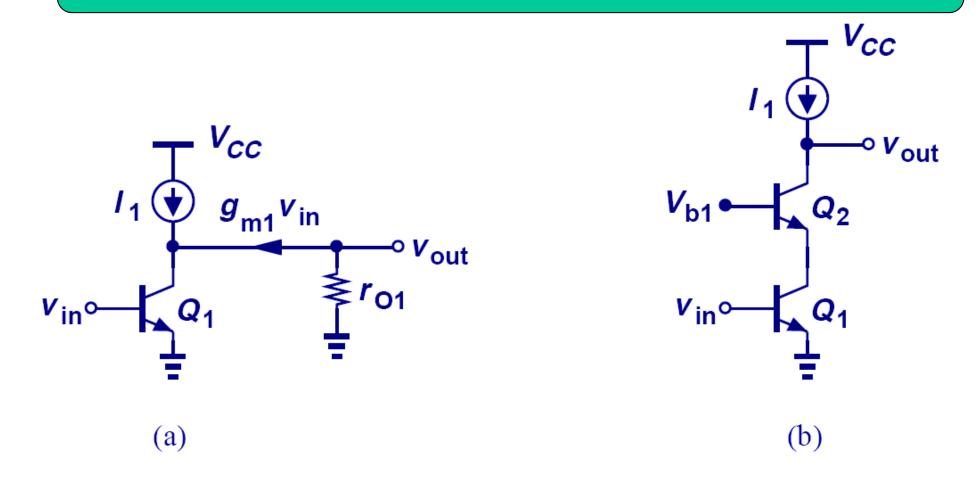

Instead of treating cascode as Q<sub>2</sub> degenerating Q<sub>1</sub>, we can also think of it as Q<sub>1</sub> stacking on top of Q<sub>2</sub> (current source) to boost Q<sub>2</sub>'s output impedance.

### **False Cascodes**

$$\begin{aligned} R_{out} &= \left[ 1 + g_{m1} \left( \frac{1}{g_{m2}} \parallel r_{O2} \parallel r_{\pi 2} \parallel r_{\pi 1} \right) \right] r_{O1} + \frac{1}{g_{m2}} \parallel r_{O2} \parallel r_{\pi 2} \parallel r_{\pi 1} \\ R_{out} &\approx \left( 1 + \frac{g_{m1}}{g_{m2}} \right) r_{O1} + \frac{1}{g_{m2}} \approx 2r_{O1} \end{aligned}$$

When the emitter of Q<sub>1</sub> is connected to the emitter of Q<sub>2</sub>, it's no longer a cascode since Q<sub>2</sub> becomes a diode-connected device instead of a current source.

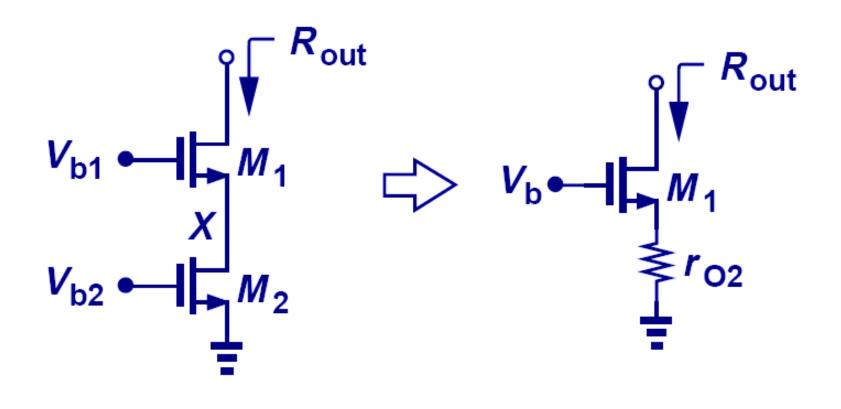

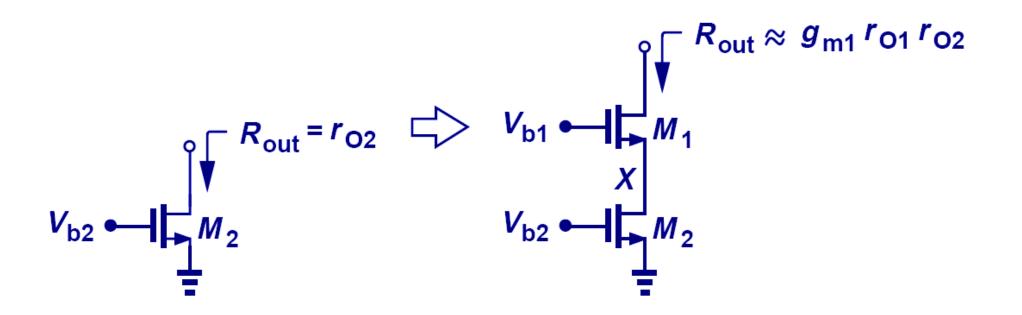

### **MOS Cascode Stage**

$$R_{out} = (1 + g_{m1}r_{O2})r_{O1} + r_{O2}$$

$$R_{out} \approx g_{m1}r_{O1}r_{O2}$$

### **Another Interpretation of MOS Cascode**

- Similar to its bipolar counterpart, MOS cascode can be thought of as stacking a transistor on top of a current source.

- Unlike bipolar cascode, the output impedance is not limited by β.

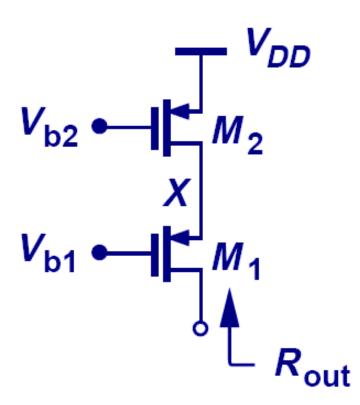

### **PMOS Cascode Stage**

$$\begin{aligned} R_{out} &= (1 + g_{m1} r_{O2}) r_{O1} + r_{O2} \\ R_{out} &\approx g_{m1} r_{O1} r_{O2} \end{aligned}$$

### **Example: Parasitic Resistance**

#### R<sub>P</sub> will lower the output impedance, since its parallel combination with r<sub>01</sub> will always be lower than r<sub>01</sub>.

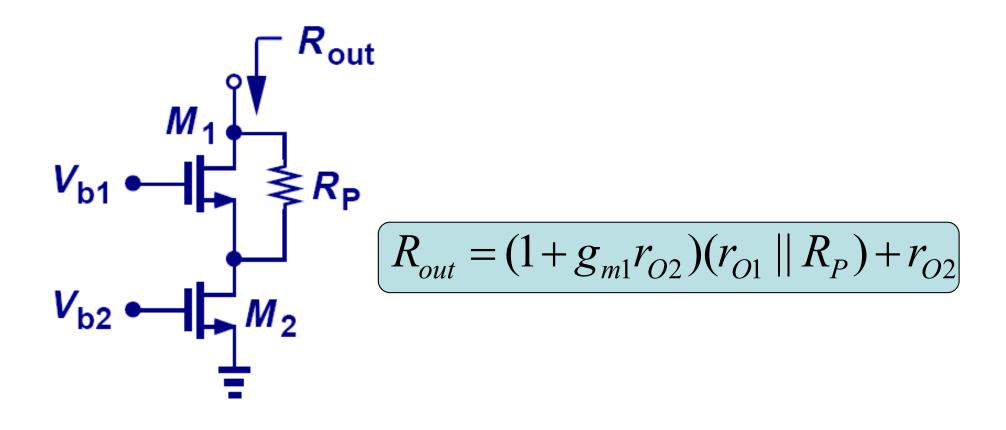

### **Comparison between Bipolar Cascode and CE Stage**

#### Since the output impedance of bipolar cascode is higher than that of the CE stage, we would expect its voltage gain to be higher as well.

### **Voltage Gain of Bipolar Cascode Amplifier**

Since r<sub>o</sub> is much larger than 1/g<sub>m</sub>, most of I<sub>C,Q1</sub> flows into the diode-connected Q<sub>2</sub>. Using R<sub>out</sub> as before, A<sub>V</sub> is easily calculated.

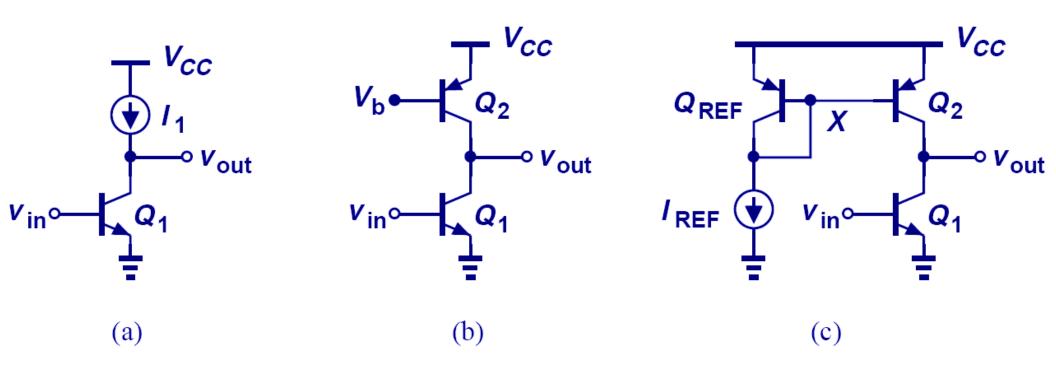

### **Practical Cascode Stage**

### Since no current source can be ideal, the output impedance drops.

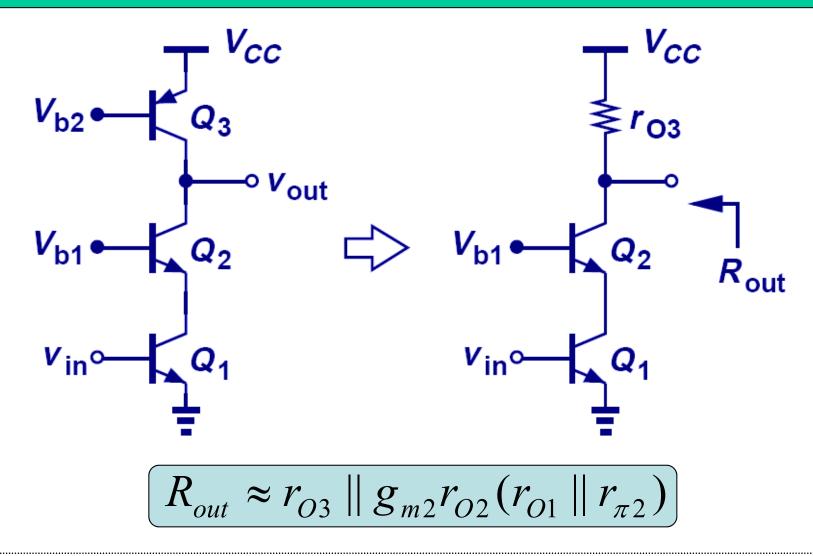

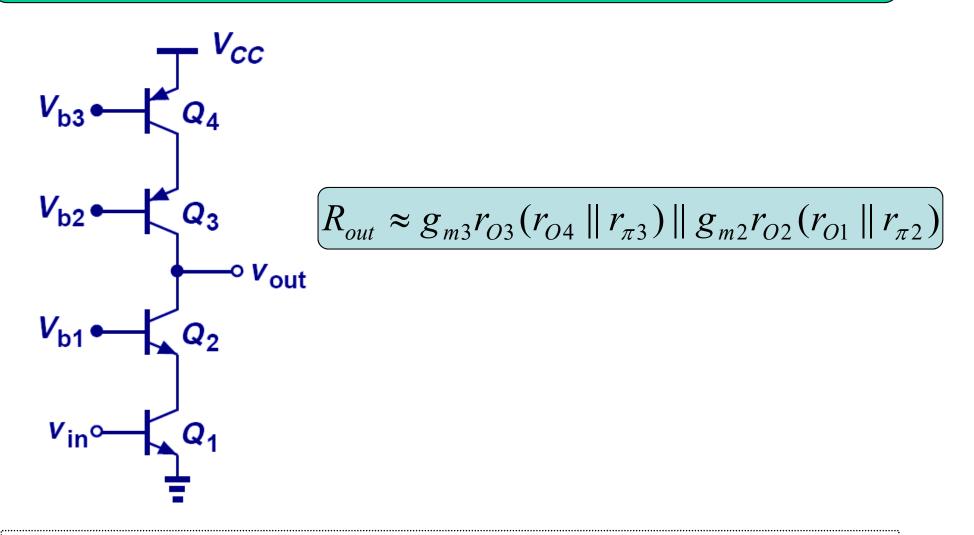

### Improved Cascode Stage

#### In order to preserve the high output impedance, a cascode PNP current source is used.

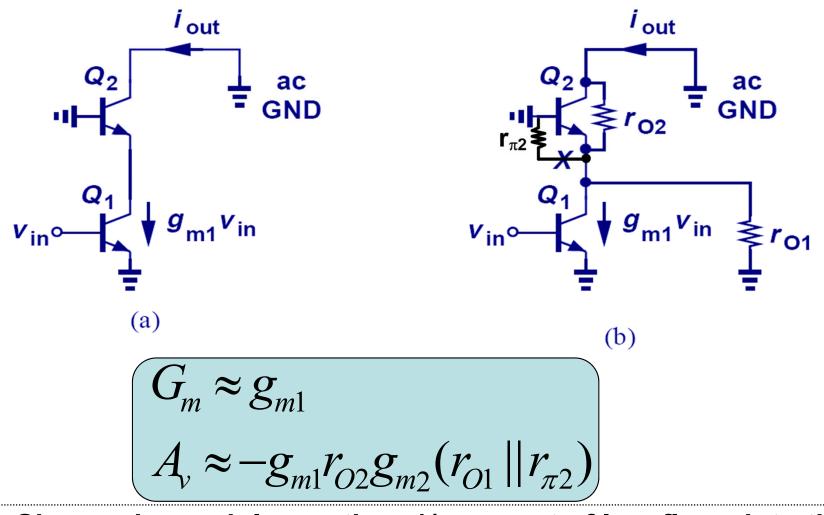

### **MOS Cascode Amplifier**

$$\begin{aligned} A_{v} &= -G_{m}R_{out} \\ A_{v} &\approx -g_{m1} \Big[ (1 + g_{m2}r_{O2})r_{O1} + r_{O2} \Big] \\ A_{v} &\approx -g_{m1}g_{m2}r_{O2}r_{O1} \end{aligned}$$

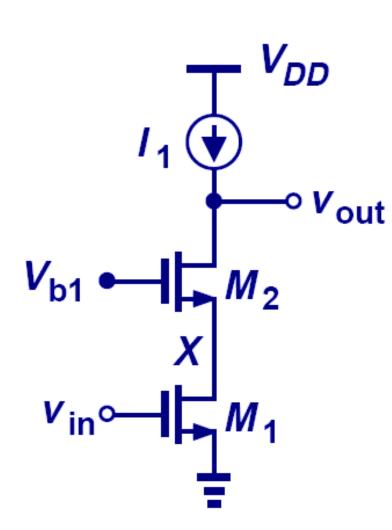

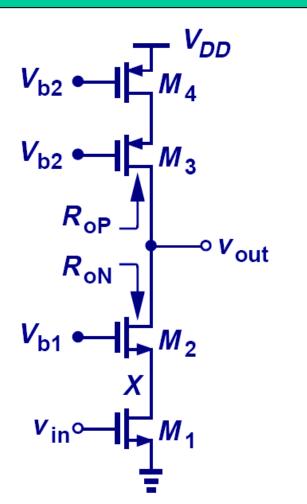

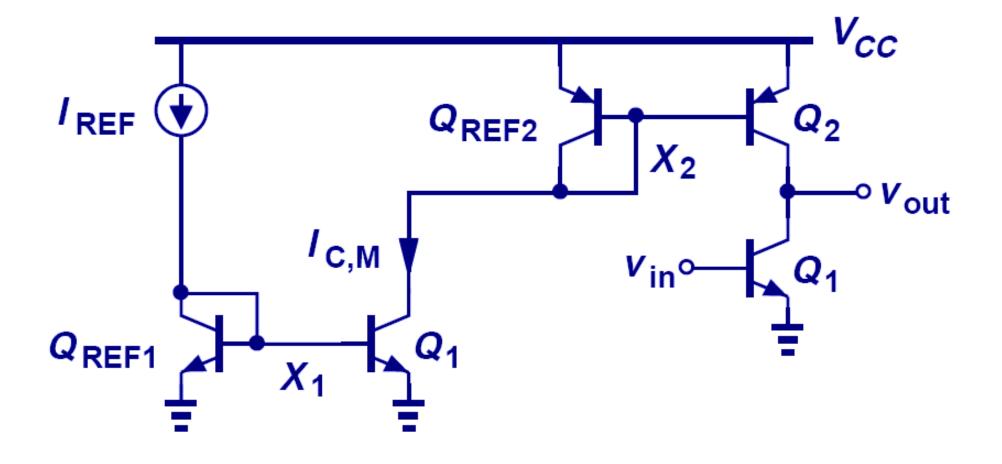

### Improved MOS Cascode Amplifier

$$R_{on} \approx g_{m2} r_{O2} r_{O1}$$

$$R_{op} \approx g_{m3} r_{O3} r_{O4}$$

$$R_{out} = R_{on} \parallel R_{op}$$

Similar to its bipolar counterpart, the output impedance of a MOS cascode amplifier can be improved by using a PMOS cascode current source.

### Agenda

- Cascode Stages

- Current Mirrors

- BJT Current Mirror Basics

- MOS Current Mirrors Basics

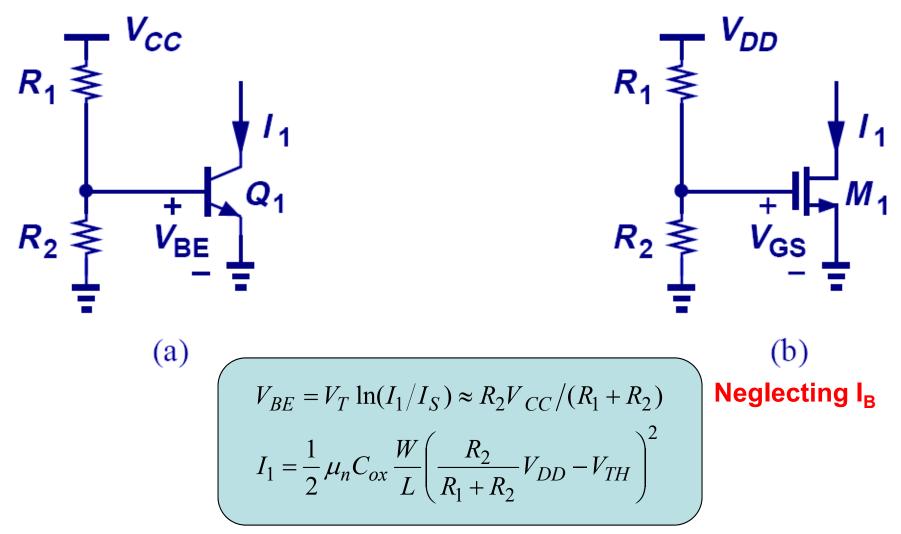

### Temperature and Supply Dependence of Bias Current

Since  $V_T$ ,  $I_S$ ,  $\mu_n$ , and  $V_{TH}$  all depend on temperature,  $I_1$  for both bipolar and MOS depends on temperature and supply.

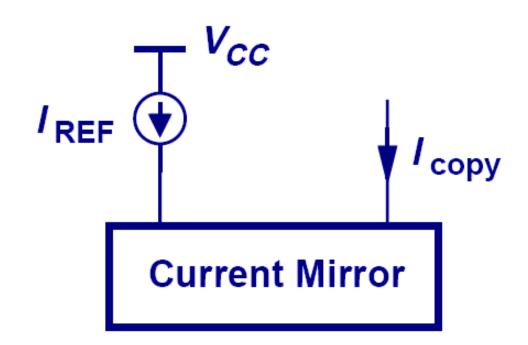

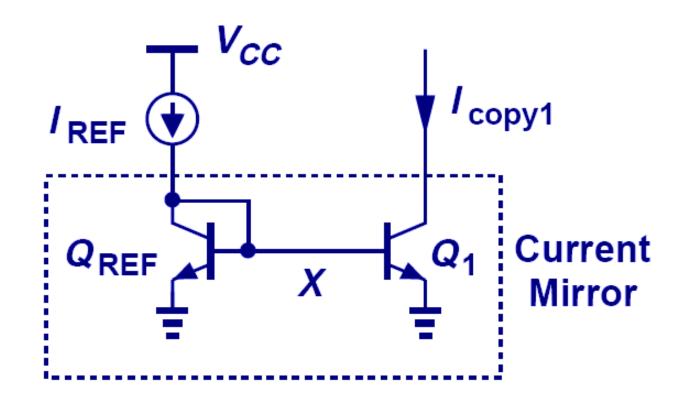

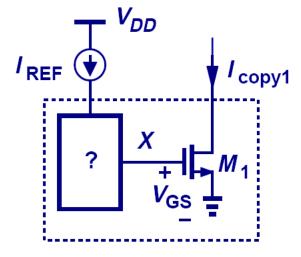

### **Concept of Current Mirror**

The motivation behind a current mirror is to sense the current from a "golden current source" and duplicate this "golden current" to other locations.

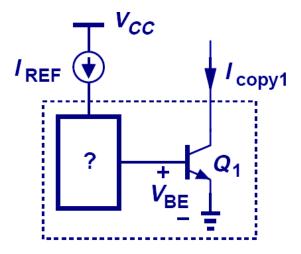

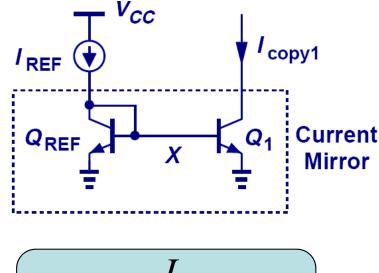

### **Bipolar Current Mirror Circuitry**

$$\left(I_{copy} = \frac{I_{S1}}{I_{S,REF}}I_{REF}\right)$$

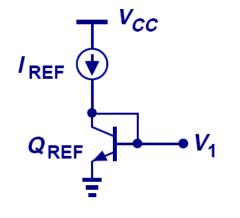

The diode-connected Q<sub>REF</sub> produces an output voltage V<sub>1</sub> that forces I<sub>copy1</sub> = I<sub>REF</sub>, if Q<sub>1</sub> = Q<sub>REF</sub>.

Neglecting base current for now (assuming high  $\beta$ ),

from the  $I_C$  expression

$$I_C = I_S \left( e^{\frac{V_{BE}}{V_T}} - 1 \right) \approx I_S e^{\frac{V_{BE}}{V_T}}$$

the voltage produced by the diode connected transistor is

$$V_1 = V_T \ln \left( \frac{I_{REF}}{I_{S,REF}} \right)$$

this voltage forms the  $V_{BE}$  of the output current source to produce

$$I_{copy} = I_{S1}e^{\frac{V_T \ln\left(\frac{I_{REF}}{I_{S,REF}}\right)}{V_T}} = \frac{I_{S1}}{I_{S,REF}}I_{REF}$$

CH 9 Cascode Stages and Current Mirrors

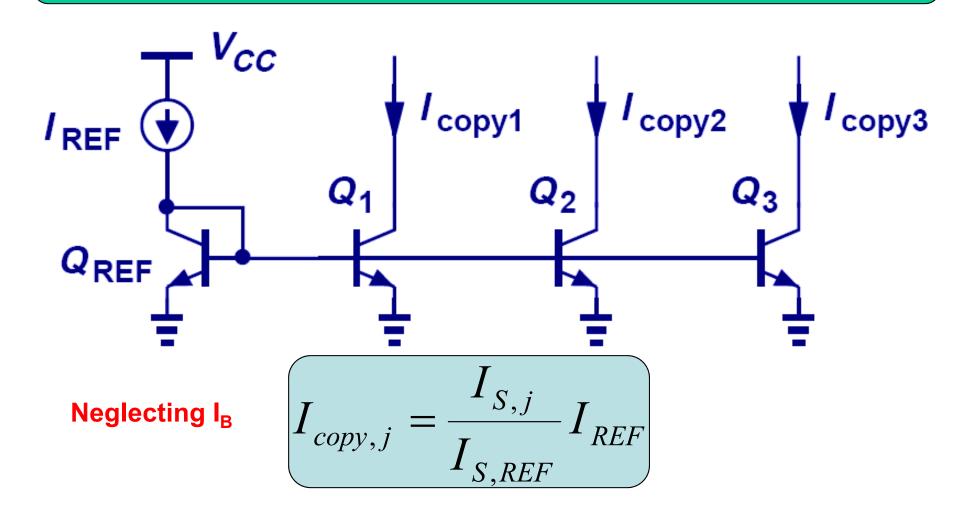

### Multiple Copies of ${\rm I}_{\rm REF}$

Multiple copies of I<sub>REF</sub> can be generated at different locations by simply applying the idea of current mirror to more transistors.

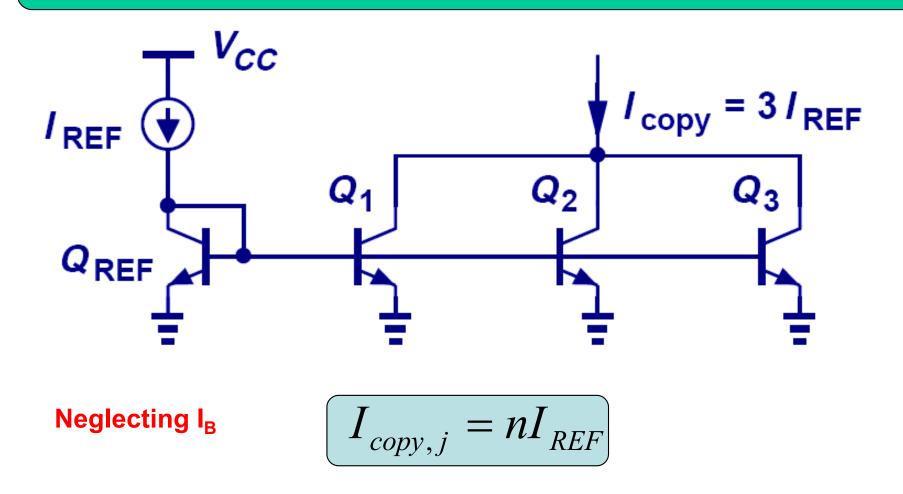

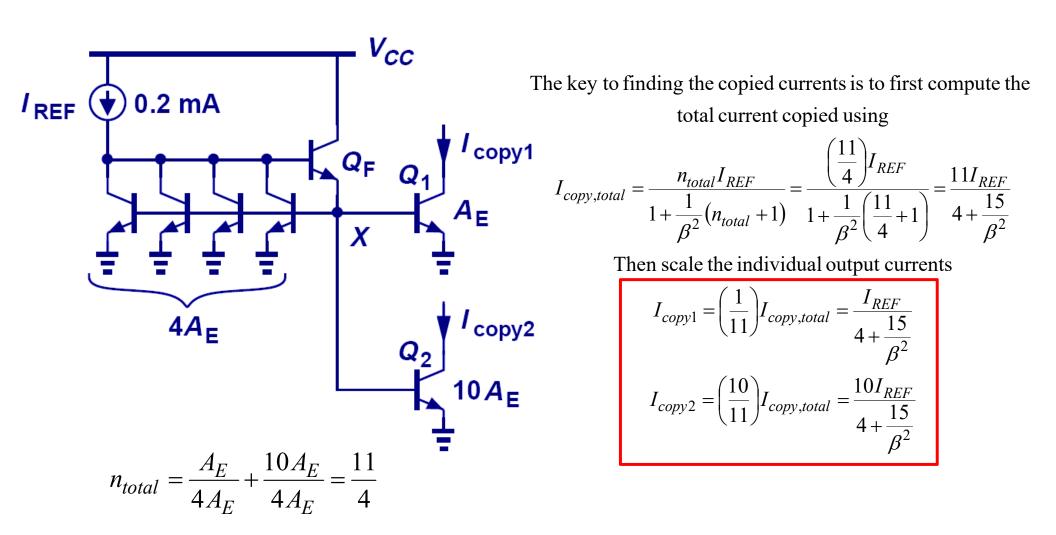

### **Current Scaling**

By scaling the emitter area of Q<sub>j</sub> n times with respect to Q<sub>REF</sub>, I<sub>copy,j</sub> is also n times larger than I<sub>REF</sub>. This is equivalent to placing n unit-size transistors in parallel.

### **Example: Scaled Current**

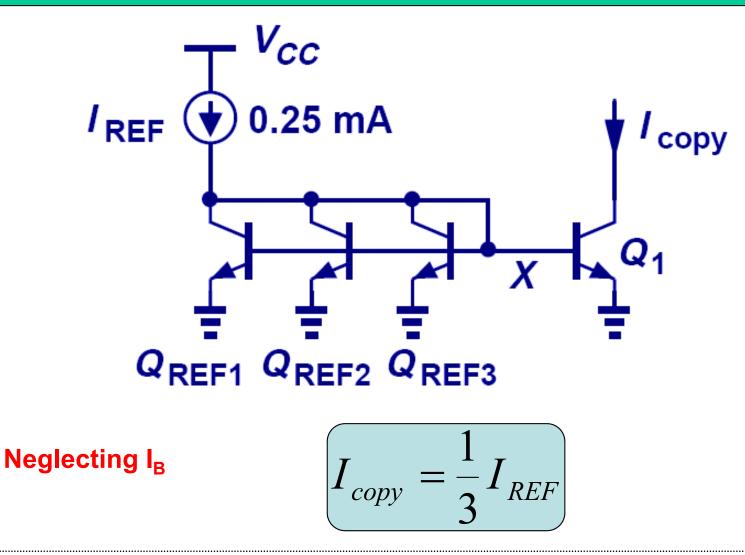

### **Fractional Scaling**

A fraction of I<sub>REF</sub> can be created on Q<sub>1</sub> by scaling up the emitter area of Q<sub>REF</sub>.

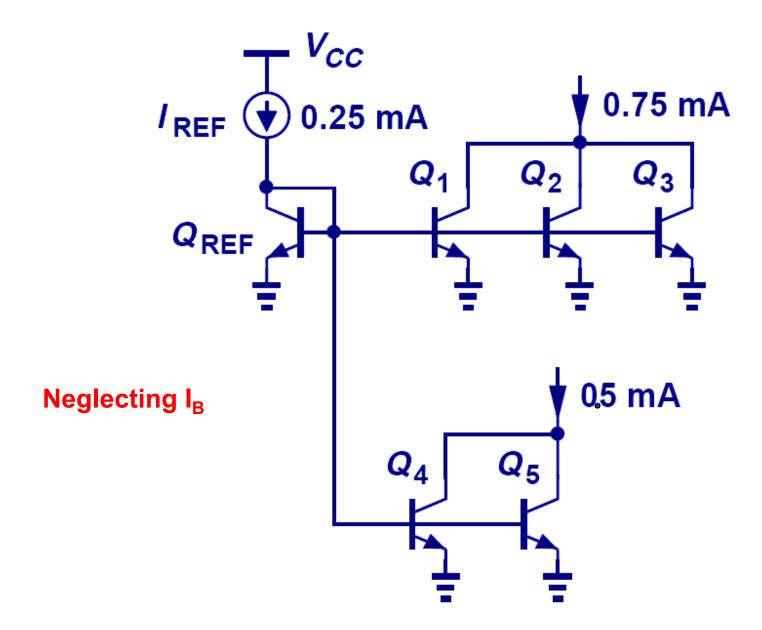

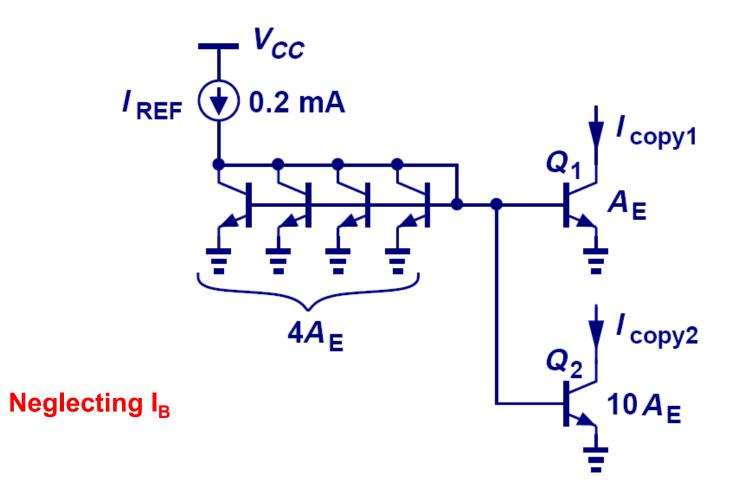

### **Example: Different Mirroring Ratio**

Using the idea of current scaling and fractional scaling, I<sub>copy2</sub> is 0.5mA and I<sub>copy1</sub> is 0.05mA respectively. All coming from a source of 0.2mA.

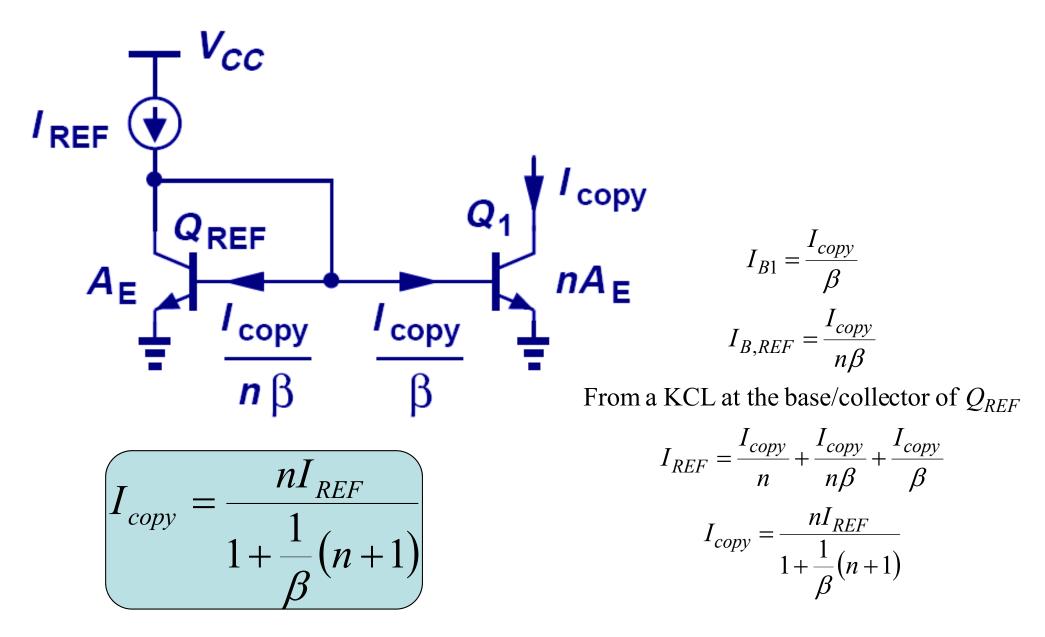

### **Mirroring Error Due to Base Currents**

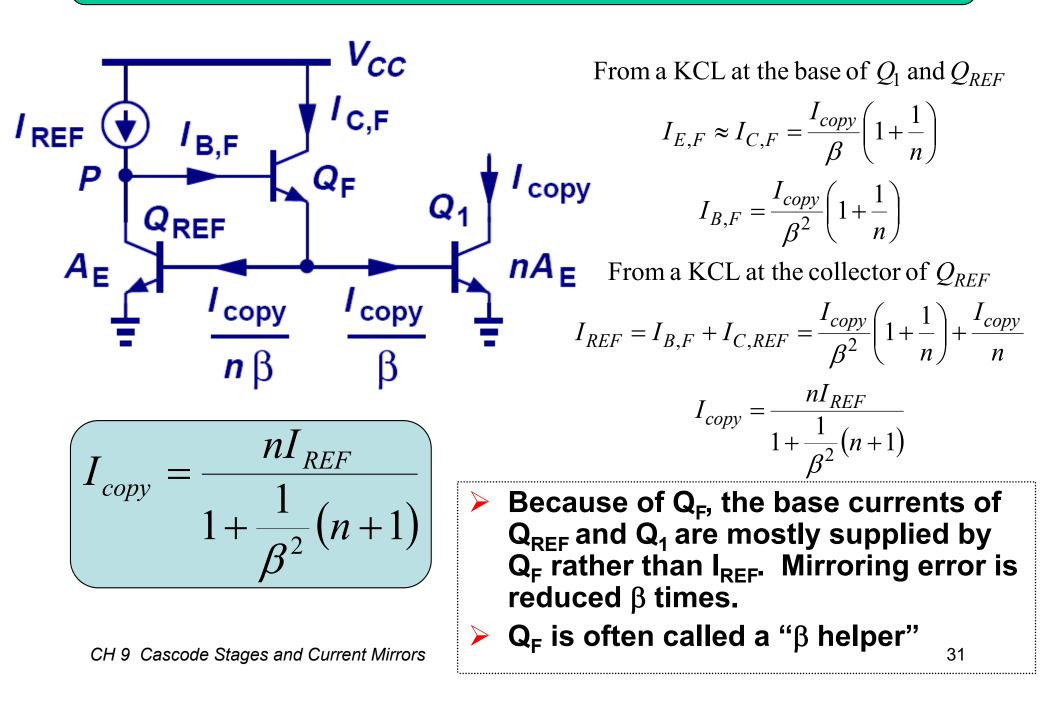

### **Improved Mirroring Accuracy**

### **Example: Different Mirroring Ratio Accuracy**

### **PNP Current Mirror**

PNP current mirror is used as a current source load to an NPN amplifier stage.

But what if we only have 1 ideal reference current that flows from V<sub>cc</sub>, as in all the previous NPN current mirror examples?

### **Generation of I<sub>REF</sub> for PNP Current Mirror**

### **Example: Current Mirror with Discrete Devices**

- Let Q<sub>REF</sub> and Q<sub>1</sub> be discrete NPN devices. I<sub>REF</sub> and I<sub>copy1</sub> can vary in large magnitude due to I<sub>s</sub> mismatch.

- Thus, current mirrors may not be used that often in discrete (board-level) design, but are pervasive in integrated circuit (IC) design

### Agenda

Cascode Stages

- Current Mirrors

- BJT Current Mirror Basics

- MOS Current Mirrors Basics

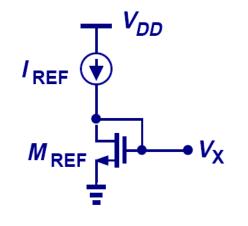

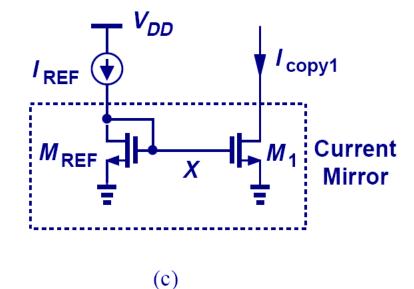

### **MOS Current Mirror**

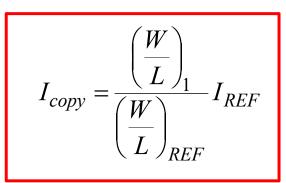

From the saturation current equation

$$I_{D} = \frac{\mu_{n} C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{TH,n})^{2}$$

the voltage produced by the diode connected transistor is

$$V_X = \sqrt{\frac{2I_{REF}}{\mu_n C_{ox} \left(\frac{W}{L}\right)_{REF}}} + V_{TH,n}$$

this voltage forms the  $V_{GS}$  of the output current source to produce

$$I_{copy} = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right)_1 \left(\sqrt{\frac{2I_{REF}}{\mu_n C_{ox}} \left(\frac{W}{L}\right)_{REF}} + V_{TH,n} - V_{TH,n}\right)^2 = \frac{\left(\frac{W}{L}\right)_1}{\left(\frac{W}{L}\right)_{REF}} I_{REF}$$

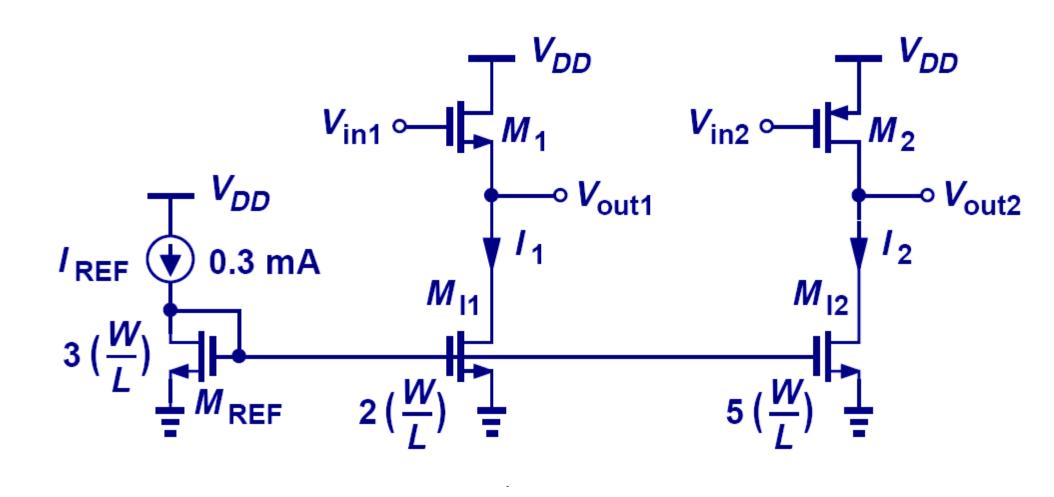

### **Example: Current Scaling**

Similar to their bipolar counterpart, MOS current mirrors can also scale I<sub>REF</sub> up or down (I<sub>1</sub> = 0.2mA, I<sub>2</sub> = 0.5mA).

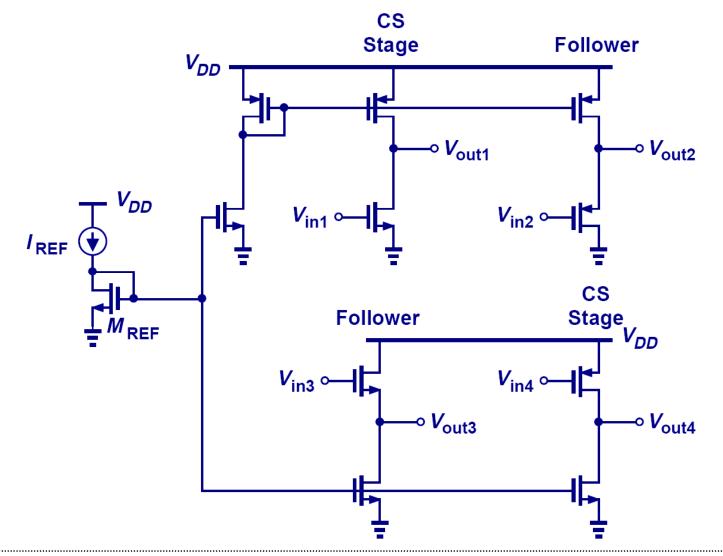

### **CMOS Current Mirror**

The idea of combining NMOS and PMOS to produce CMOS current mirror is shown above.

## Next Time

### Operational Transconductance Amplifiers

• Lab 7