## ECEN326: Electronic Circuits Fall 2022

## Lecture 3: Differential Amplifiers

Sam Palermo Analog & Mixed-Signal Center Texas A&M University

## Announcements

- HW

- HW3 due today

- Reading

- Razavi Chapter 10

## Exam 1

- In class on Feb 24

- 9:35 11:00 (10 extra minutes)

- Closed book w/ one standard note sheet

- 8.5"x11" front & back

- Bring your calculator

- Covers through Lecture 3

- Sample Exam1s posted on website

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

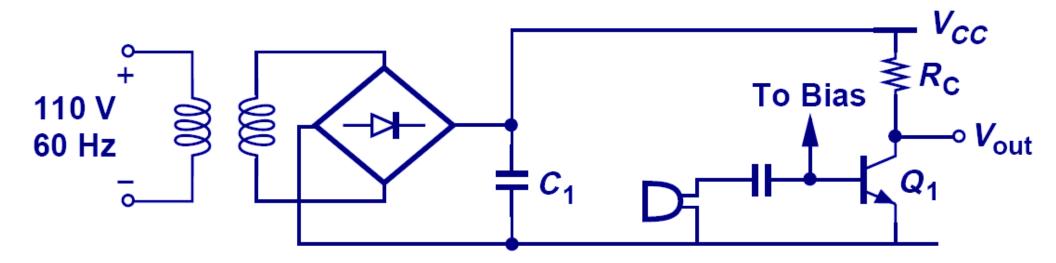

## **Audio Amplifier Example**

An audio amplifier is constructed above that takes on a rectified AC voltage as its supply and amplifies an audio signal from a microphone.

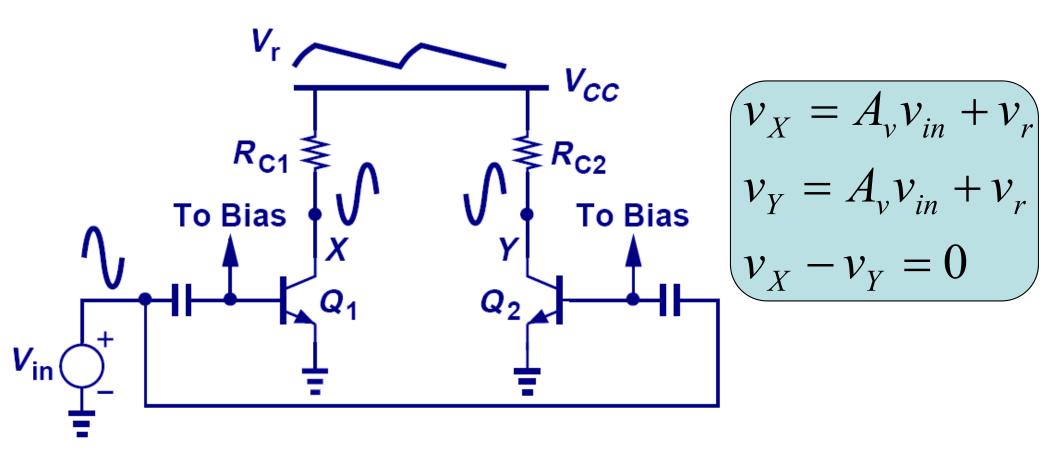

## "Humming" Noise in Audio Amplifier Example

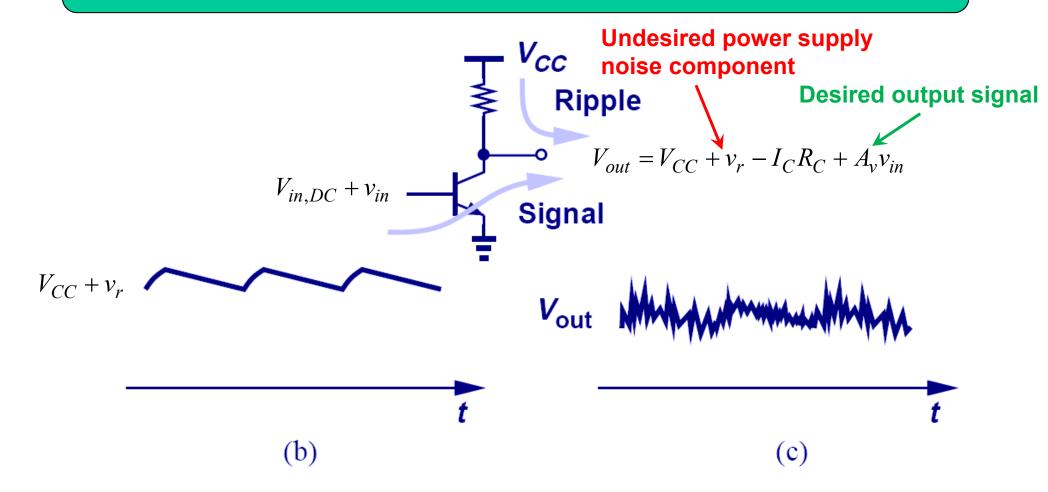

However, V<sub>CC</sub> contains a ripple from rectification that leaks to the output and is perceived as a "humming" noise by the user.

### **Supply Ripple Rejection**

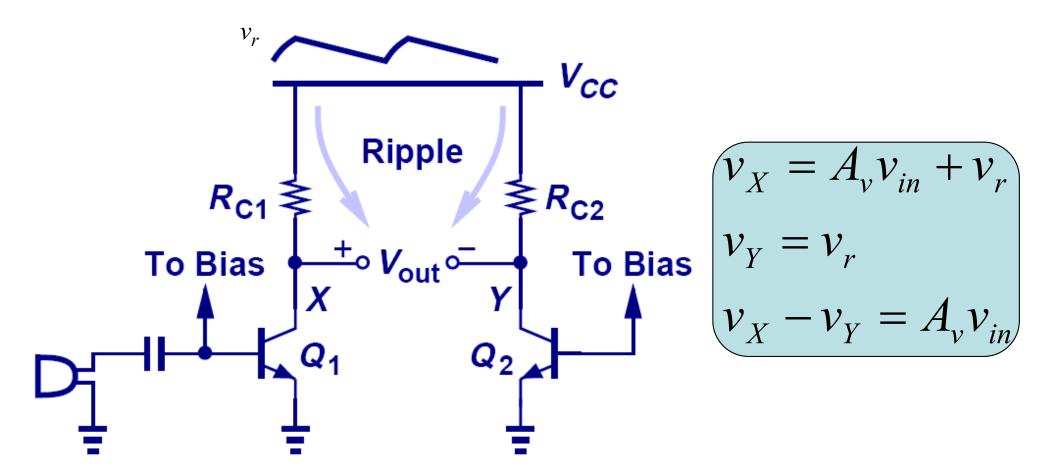

Since both node X and Y contain the ripple, v<sub>r</sub>, their difference will be free of ripple.

## **Ripple-Free Differential Output**

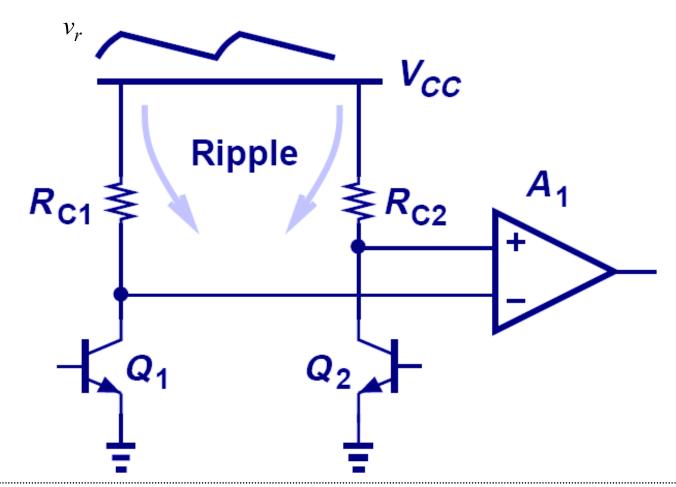

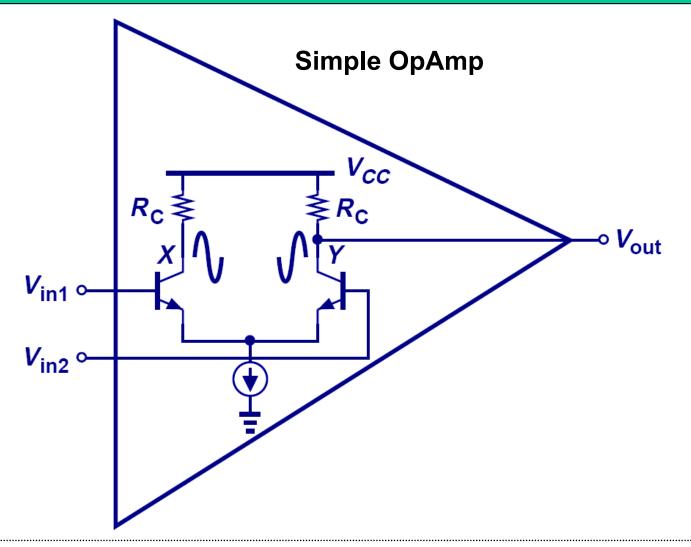

Since the signal is taken as a difference between two nodes, an amplifier that senses differential signals is needed.

How can we construct this differential amplifier?

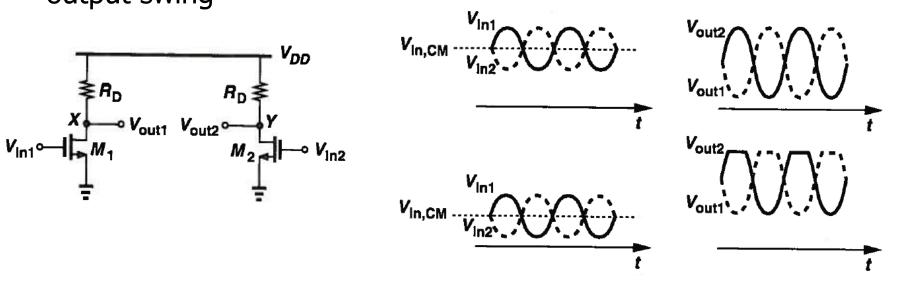

#### **Common Inputs to Differential Amplifier**

Signals cannot be applied in phase to the inputs of a differential amplifier, since the outputs will also be in phase, producing zero differential output.

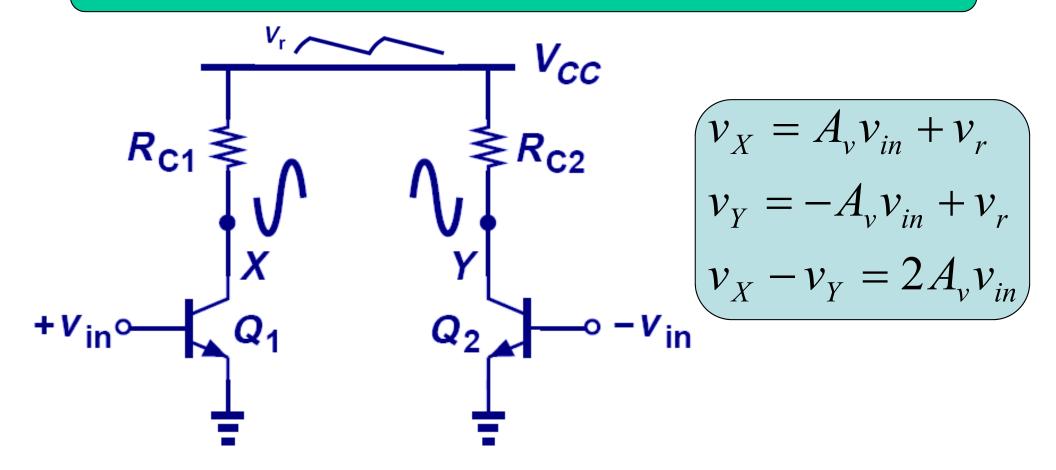

#### **Differential Inputs to Differential Amplifier**

When the inputs are applied differentially, the outputs are 180° out of phase; enhancing each other when sensed differentially.

Provides twice the output swing of the original amplifier

### **Differential Signals**

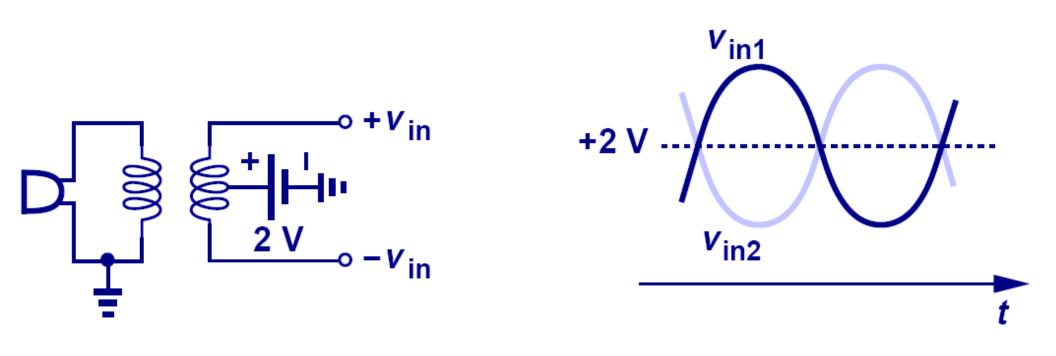

A pair of differential signals can be generated, among other ways, by a transformer.

Differential signals have the property that they share the same average value to ground and are equal in magnitude but opposite in phase.

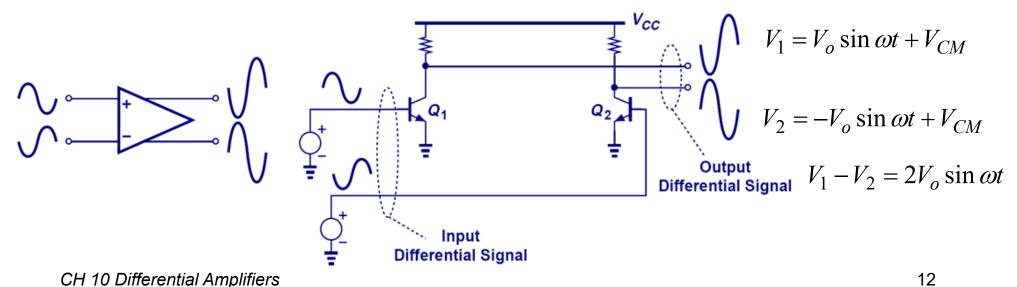

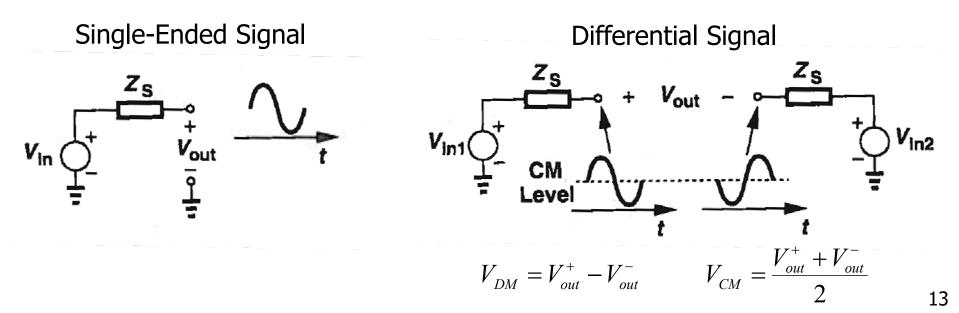

### Single-ended vs. Differential Signals

out

$V_{out} = V_o \sin \omega t + V_{CM}$

- Single-Ended Signals

- Measured with respect to the common ground

- Reside on one "line" or node

- Differential Signals

- Measured between two nodes

- Reside on two differential "lines" or nodes

# Single-Ended & Differential Signals

- A single-ended signal is measured with respect to a fixed potential (ground)

- A differential signal is measured between two equal and opposite signals which swing around a fixed potential (common-mode level)

- You can decompose differential signals into a differential mode (difference) and a common-mode (average)

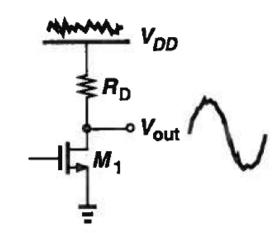

# Single-Ended & Differential Amplifiers

- Differential signaling advantages

- Common-mode noise rejection

- Higher (ideally double) potential output swing

- Simpler biasing

- Improved linearity

- Main disadvantage is area, which is roughly double

- Although, to get the same performance in single-ended designs, we often have to increase the area dramatically

Max Output Swing

$$V_{DD} - \left(V_{GS} - V_{Tn}\right)$$

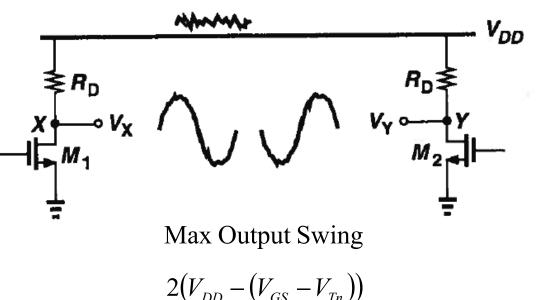

## Common-Mode Level Sensitivity

- A design which uses two single-ended amplifiers to realize a differential amplifier is very sensitive to the common-mode input level

- The transistors' bias current and transconductance can vary dramatically with the common-mode input

- Impacts small-signal gain

- Changes the output common-mode, which impacts the maximum output swing

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

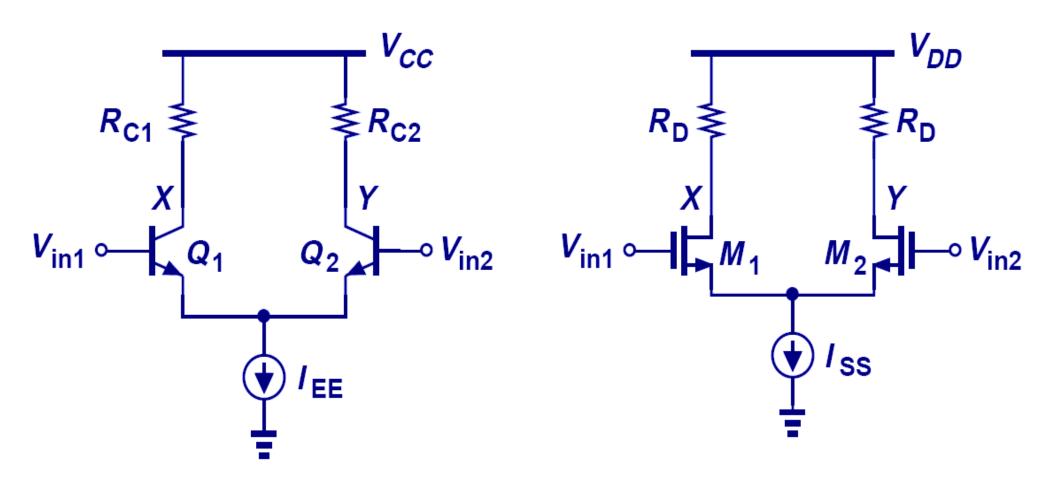

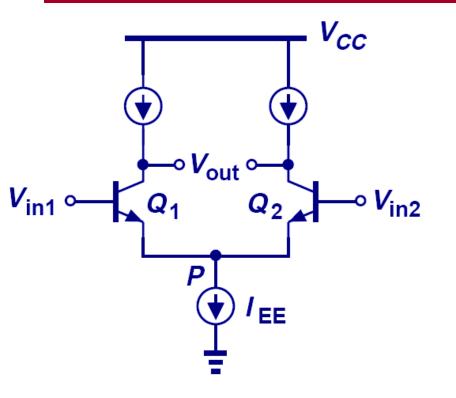

### **Differential Pair**

With the addition of a tail current, the circuits above operate as an elegant, yet robust differential pair.

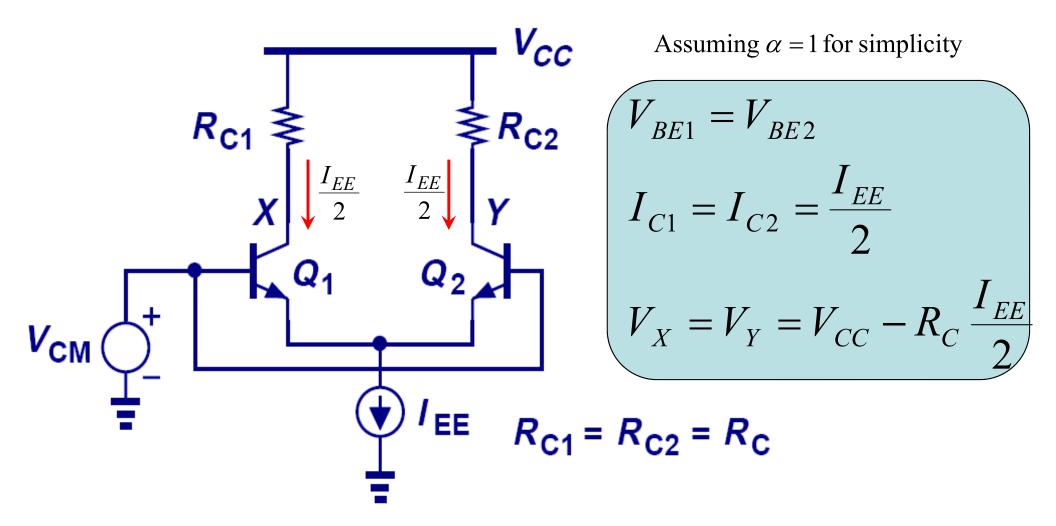

#### **Common-Mode Response**

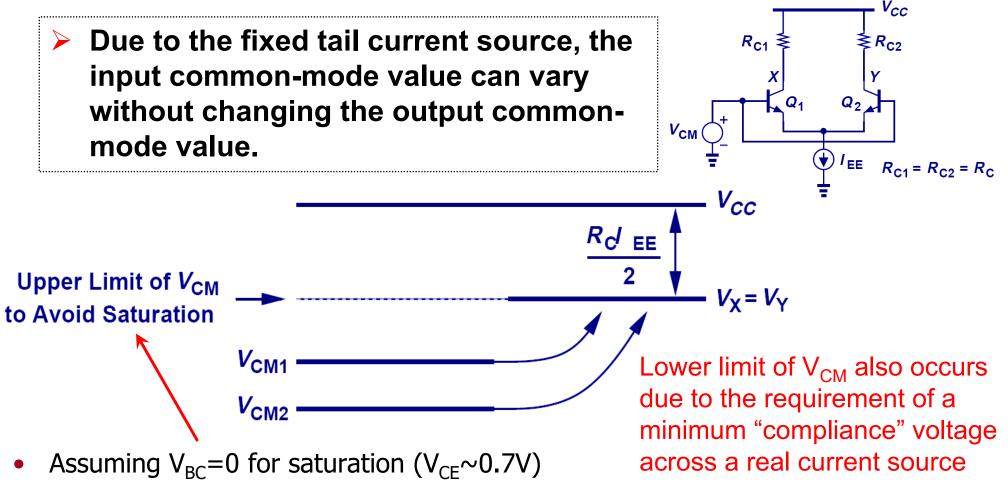

## **Common-Mode Rejection**

- Often we allow for  $V_{BC}=0.4V$  or  $V_{CE}\sim0.3V$  and still consider "active" mode operation, although this is formally "soft saturation"

- In any problems, I'll make it clear what assumptions to use

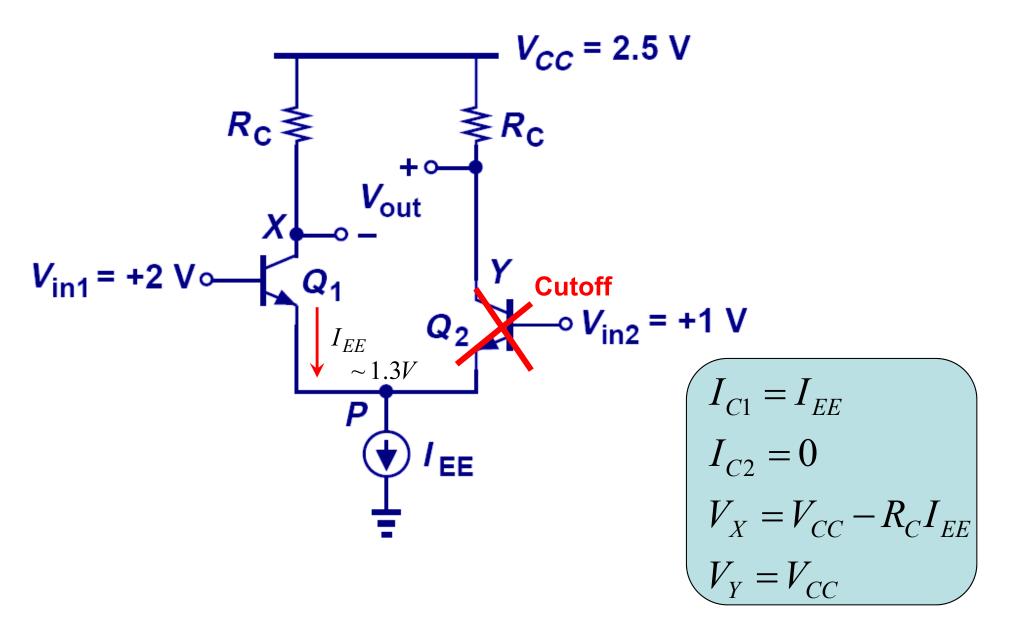

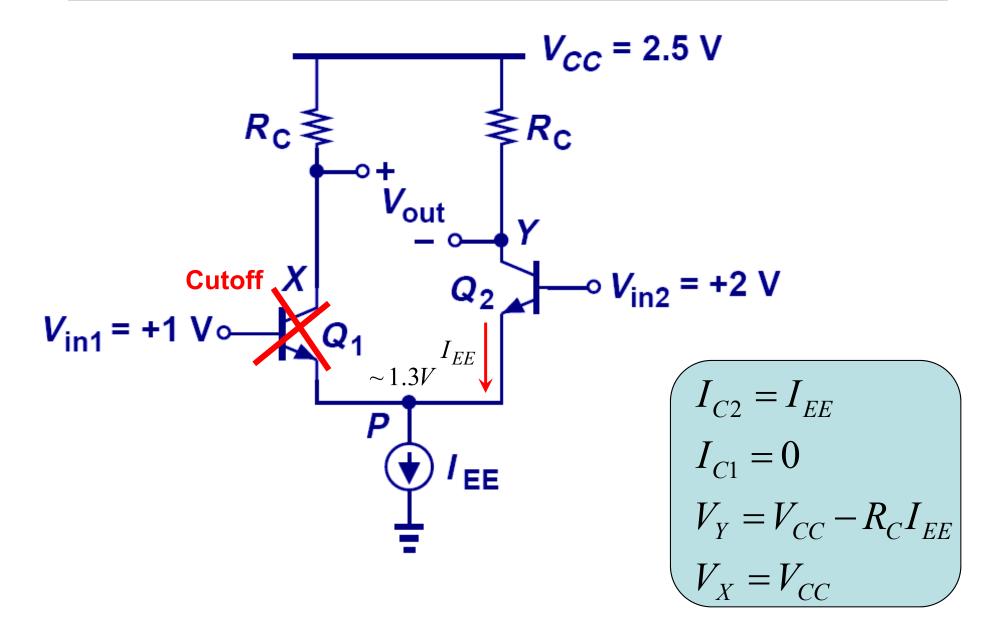

#### **Differential Response I – Big Differential Input**

#### **Differential Response II – Big Differential Input**

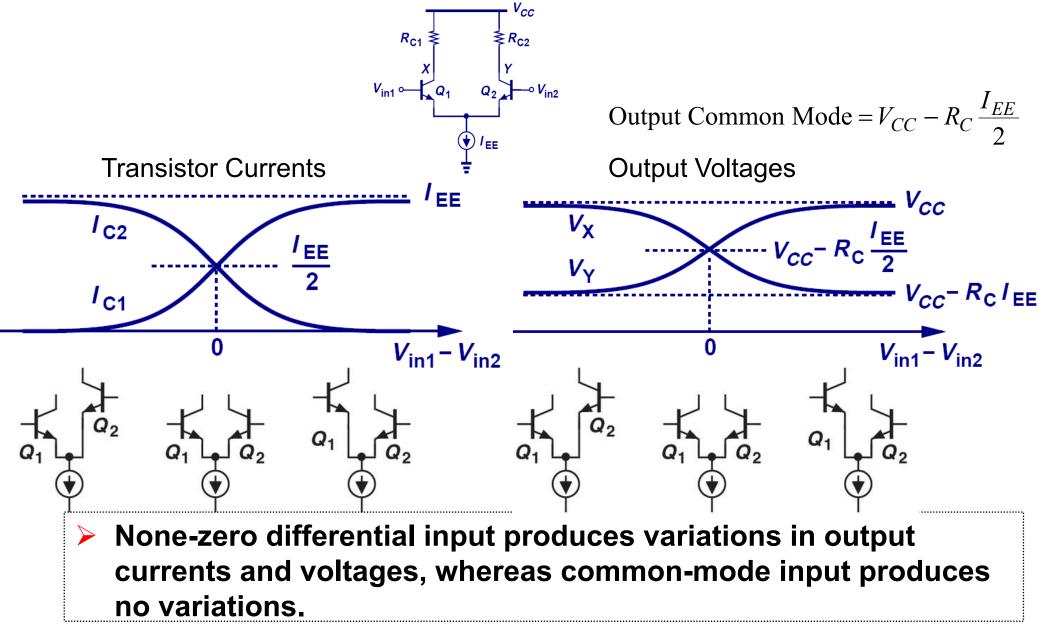

#### **Differential Pair Characteristics**

CH 10 Differential Amplifiers

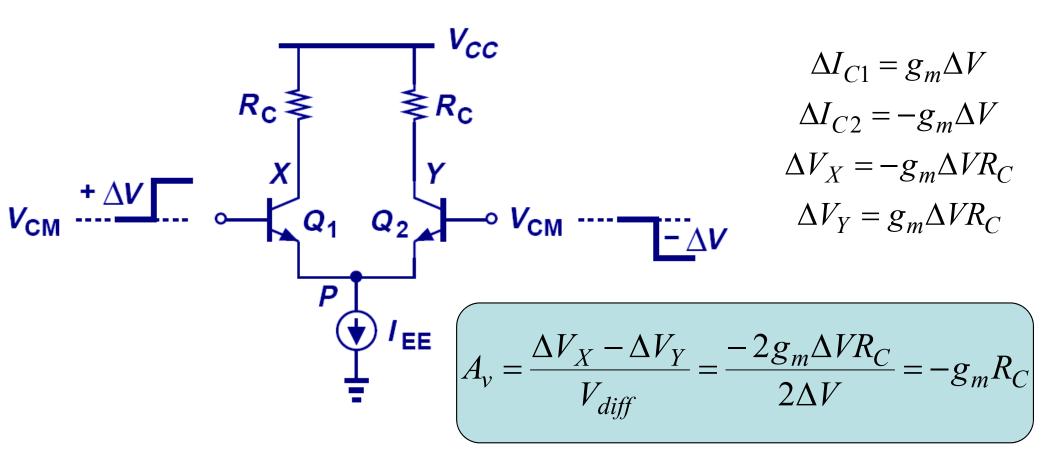

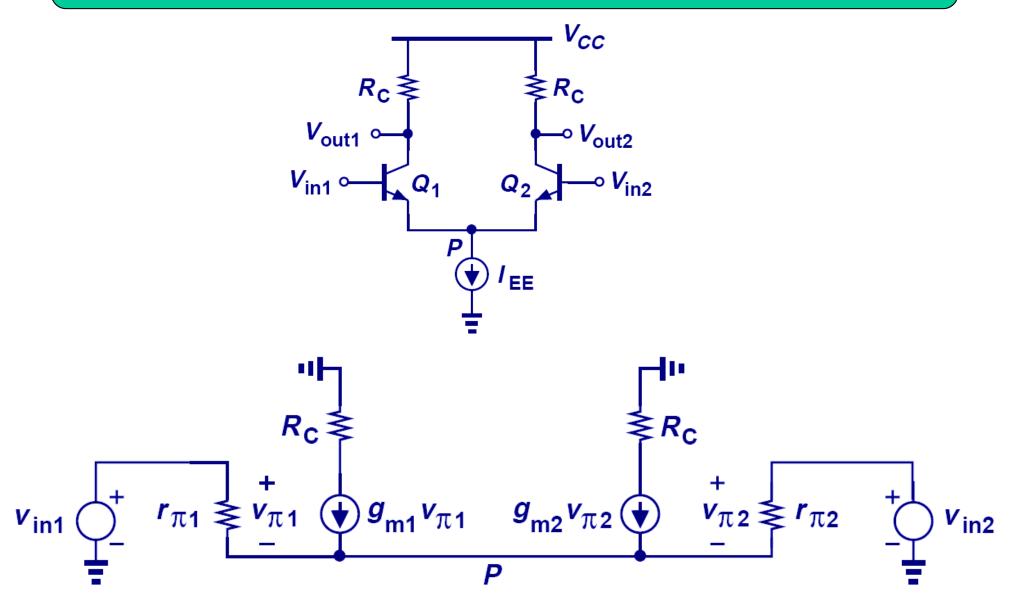

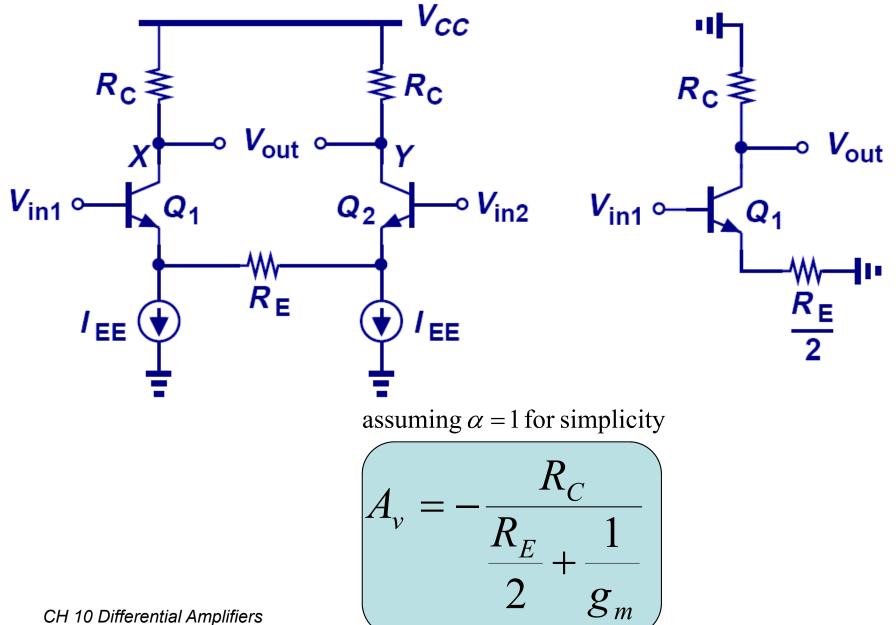

## **Small-Signal Analysis**

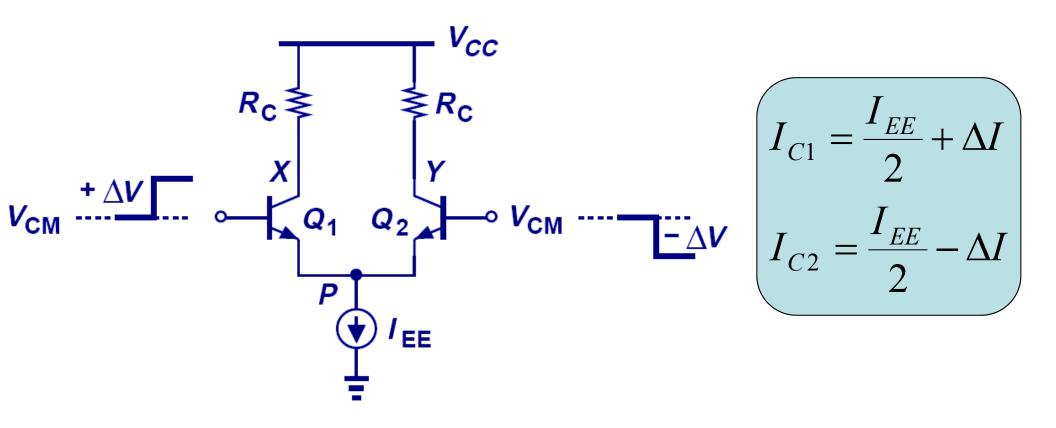

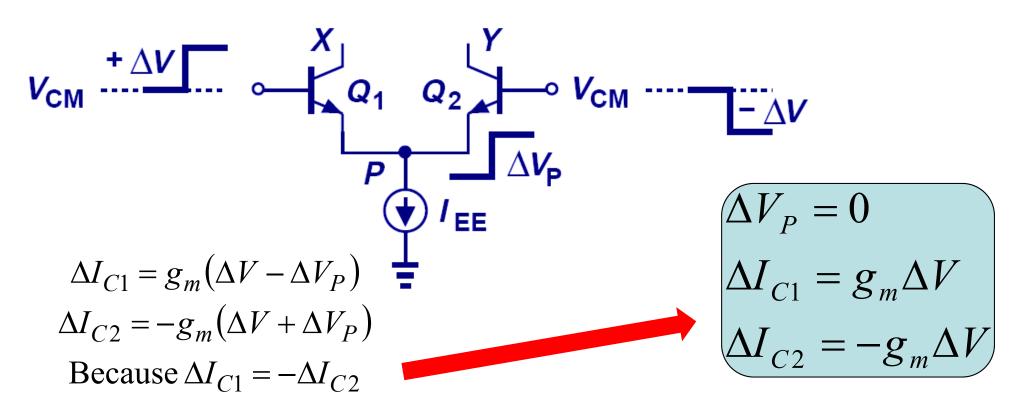

Since the input to Q<sub>1</sub> and Q<sub>2</sub> rises and falls by the same amount, and their bases are tied together, the rise in I<sub>C1</sub> has the same magnitude as the fall in I<sub>C2</sub>.

## **Virtual Ground**

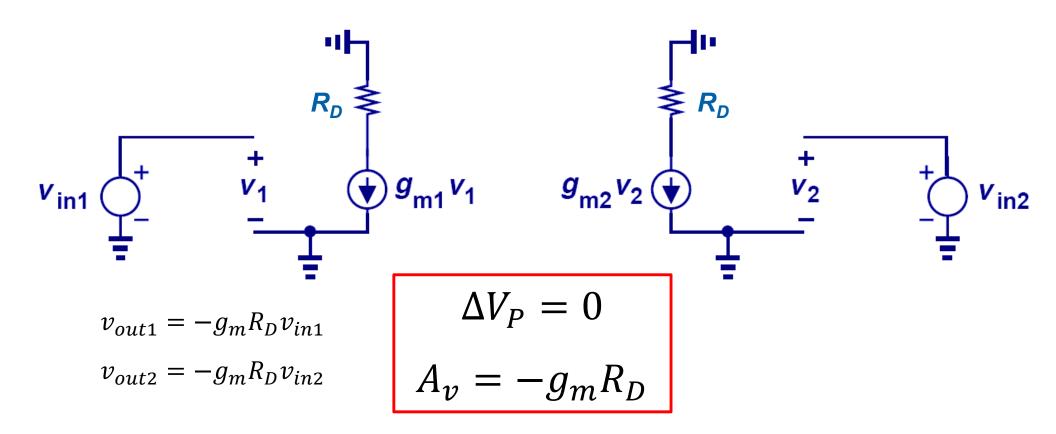

For small changes at inputs, the g<sub>m</sub>'s are the same, and the respective increase and decrease of I<sub>C1</sub> and I<sub>C2</sub> are the same, node P must stay constant to accommodate these changes. Therefore, node P can be viewed as AC ground.

### **Small-Signal Differential Gain**

Since the output changes by  $-2g_m \Delta VR_c$  and input by  $2\Delta V$ , the small signal gain is  $-g_m R_c$ , similar to that of the CE stage. However, to obtain same gain as the CE stage, power dissipation is doubled.

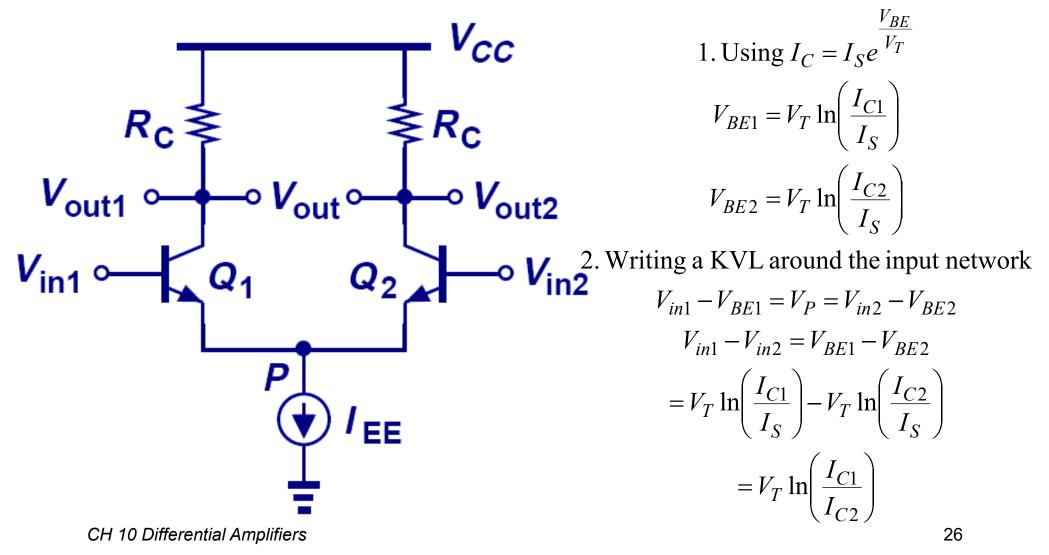

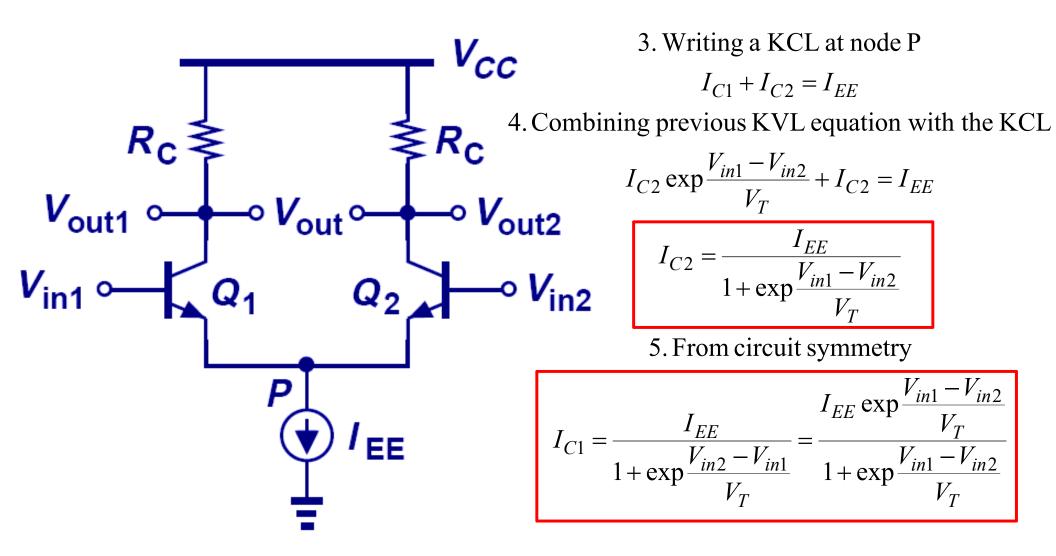

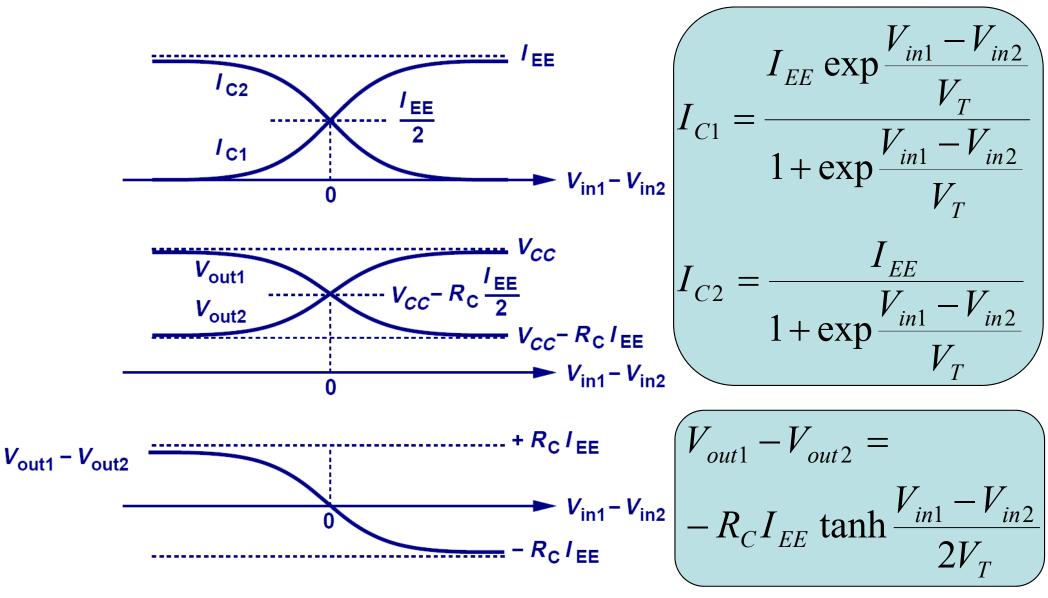

## **Large Signal Analysis**

- Objective: Find expressions for  $I_{C1}$  and  $I_{C2}$  as a function of the differential input  $V_{in1}\text{-}V_{in2}$

- This can then be used to find the differential output voltage

## **Large Signal Analysis**

#### **Input/Output Characteristics**

• If  $V_{in1}$ - $V_{in2} \ge 4V_T = 104$ mV, the majority of the current is steered through  $Q_1$ CH 10 Differential Amplifiers 28

#### **Linear/Nonlinear Regions**

The left column operates in linear region, whereas the right column operates in nonlinear region.

CH 10 Differential Amplifiers

#### **Small-Signal Model**

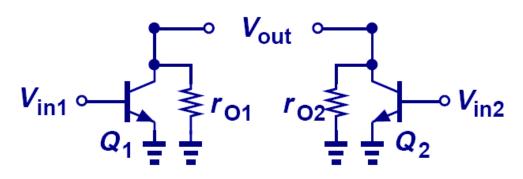

• We can use the virtual GND concept discussed in Slide 23 to simplify this CH 10 Differential Amplifiers

## Virtual GND Proof

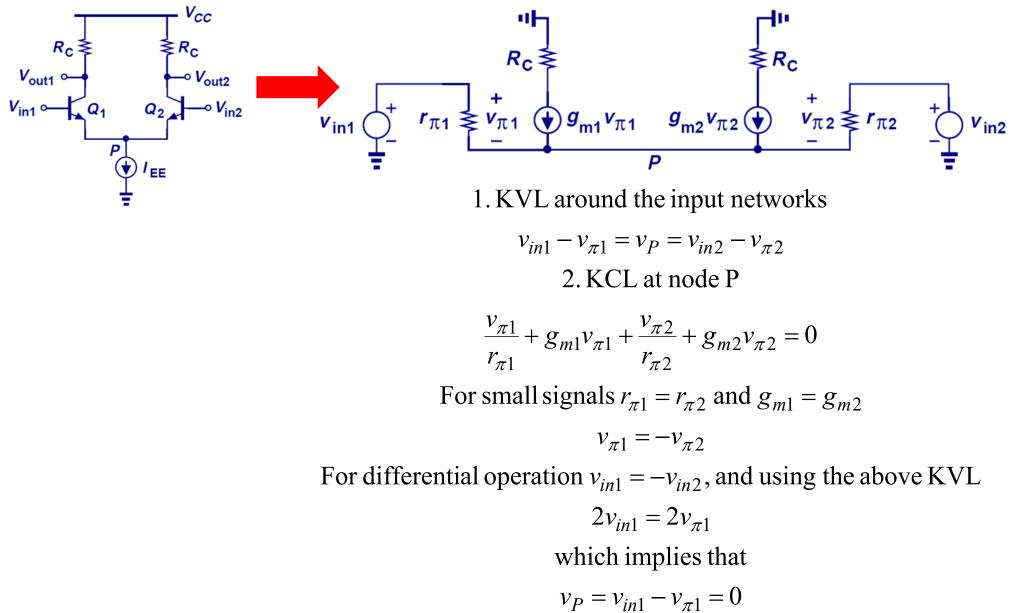

## **Half Circuits**

- Since V<sub>P</sub> is grounded, we can treat the differential pair as two CE "half circuits", with half the output swing on either side

- If the circuit is symmetrical, we can just analyze the half-circuit with a virtual ground to get the gain equation

CH 10 Differential Amplifiers

#### **Example: Differential Gain**

## **Extension of Virtual Ground**

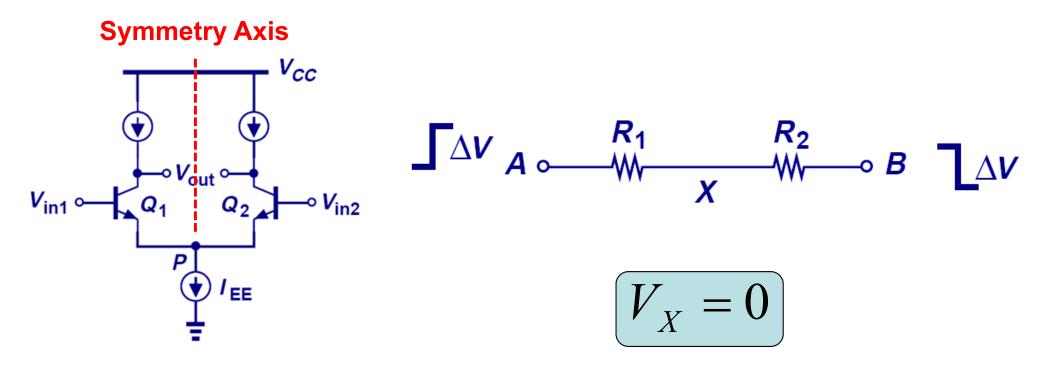

➢ It can be shown that if  $R_1 = R_2$ , and points A and B go up and down by the same amount respectively, V<sub>X</sub> does not move.

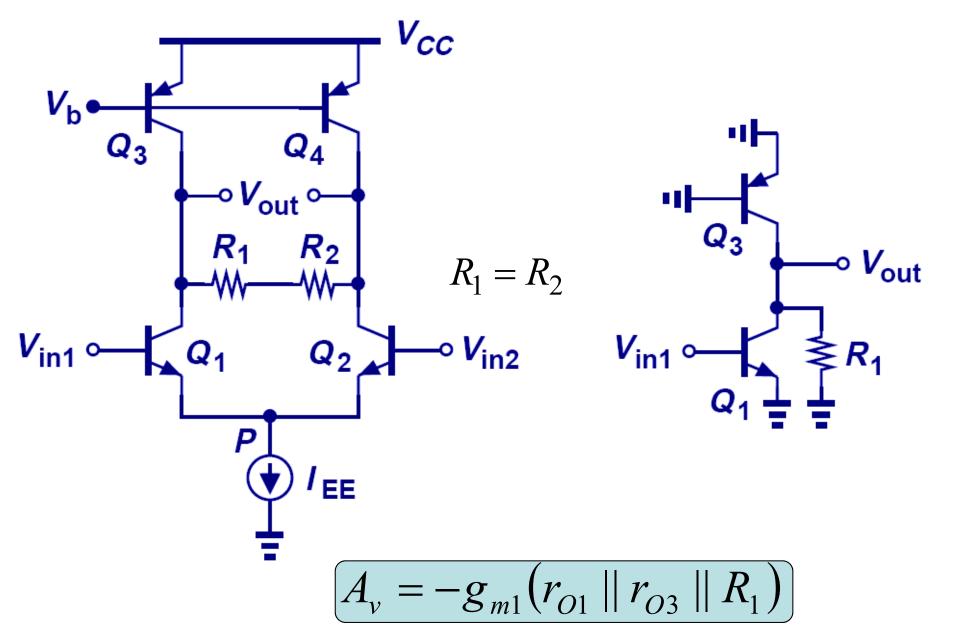

#### Half Circuit Example I

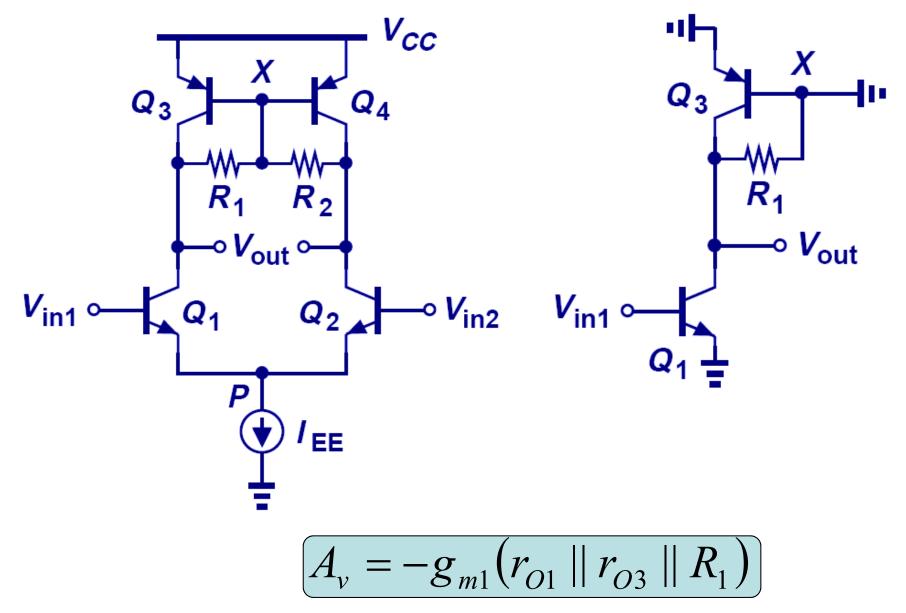

#### Half Circuit Example II

CH 10 Differential Amplifiers

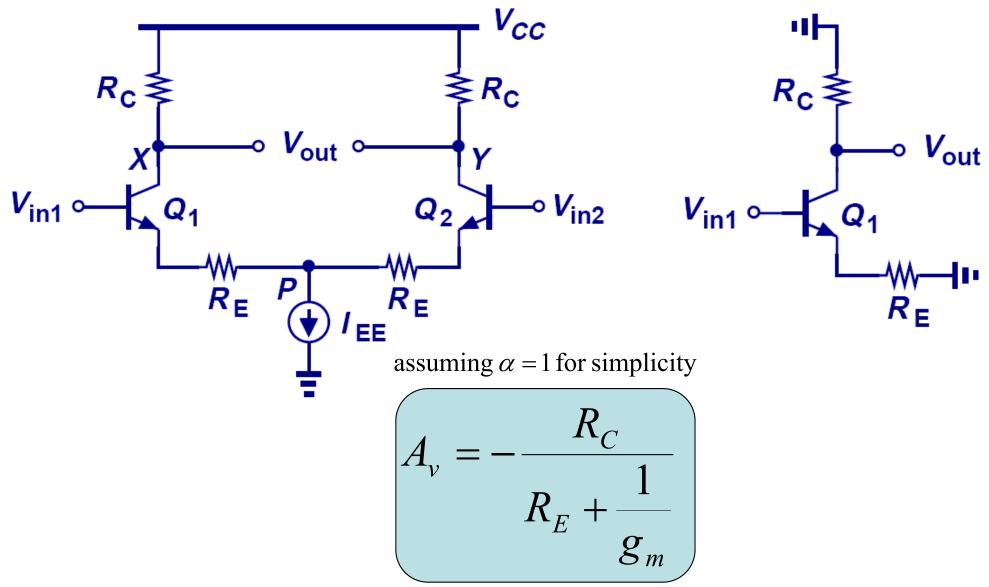

### Half Circuit Example III

### Half Circuit Example IV

38

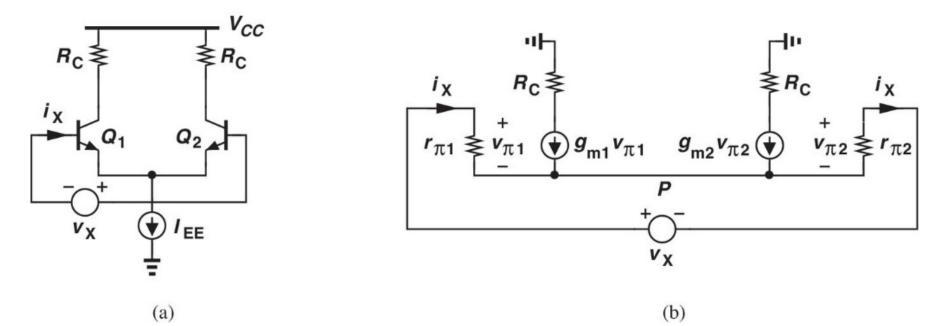

# **BJT Differential Pair Input Resistance**

In order to obtain the differential input resistance, apply a test differential voltage v<sub>x</sub> and find the developed current i<sub>x</sub>

$$\frac{v_{\pi 1}}{r_{\pi 1}} = i_X = -\frac{v_{\pi 2}}{r_{\pi 2}}$$

$$v_X = v_{\pi 1} - v_{\pi 2} = 2r_{\pi}i_X$$

Differential  $R_{in} = \frac{v_X}{i_X} = 2r_{\pi}$

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

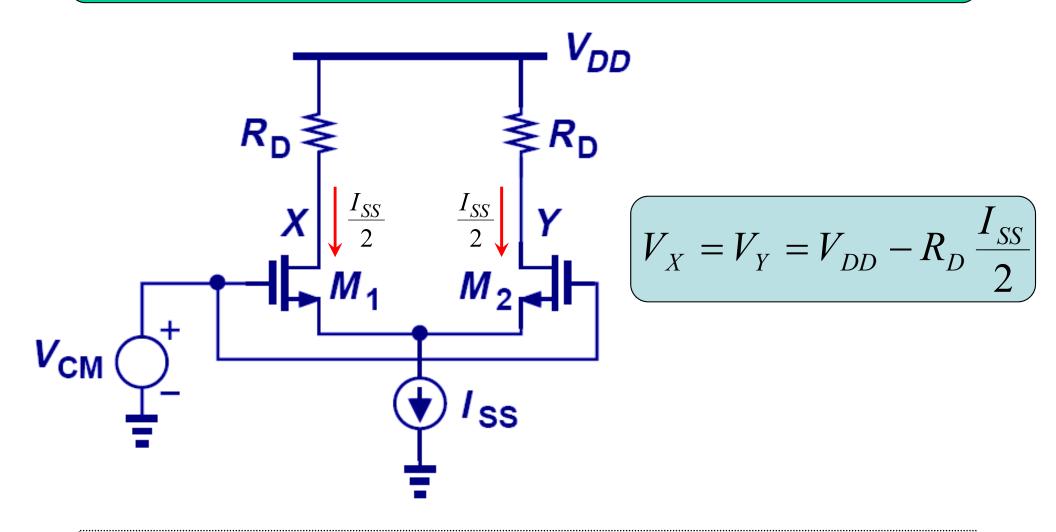

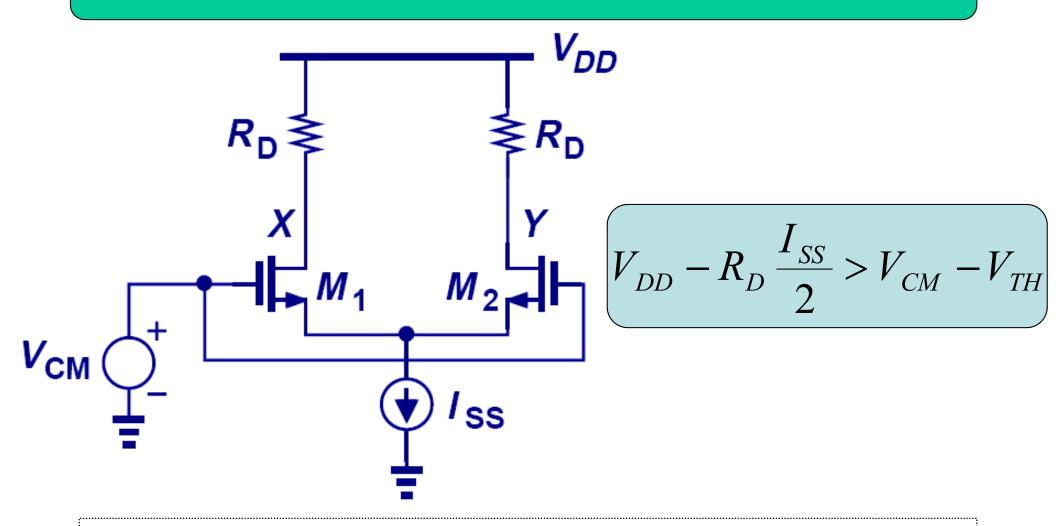

### **MOS Differential Pair's Common-Mode Response**

Similar to its bipolar counterpart, MOS differential pair produces zero differential output as V<sub>CM</sub> changes.

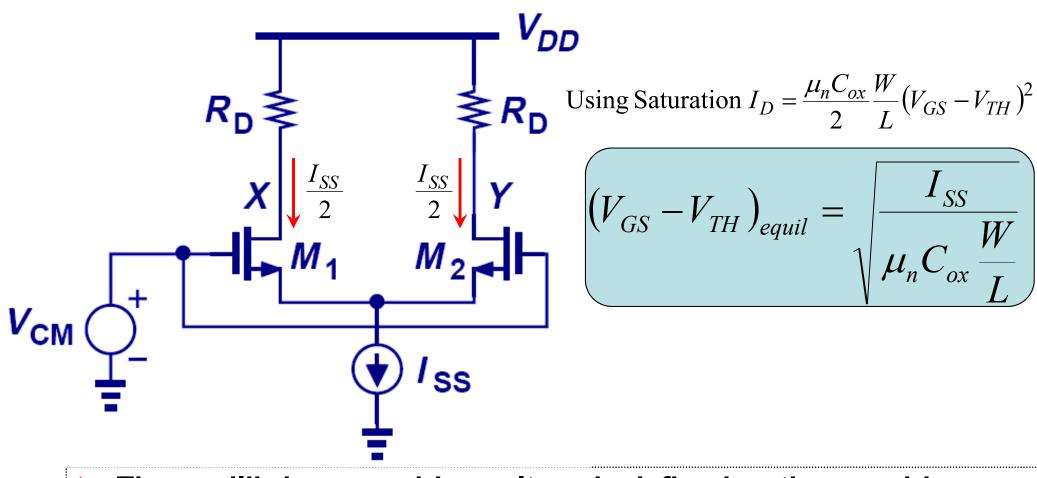

## **Equilibrium Overdrive Voltage**

- The equilibrium overdrive voltage is defined as the overdrive voltage seen by M<sub>1</sub> and M<sub>2</sub> when both carry an I<sub>ss</sub>/2 current

- Larger tail current or smaller W/L results in a larger equilibrium overdrive voltage

### Minimum Common-mode Output Voltage

In order to maintain M<sub>1</sub> and M<sub>2</sub> in saturation, the common-mode output voltage cannot fall below the value above.

This value usually limits voltage gain.

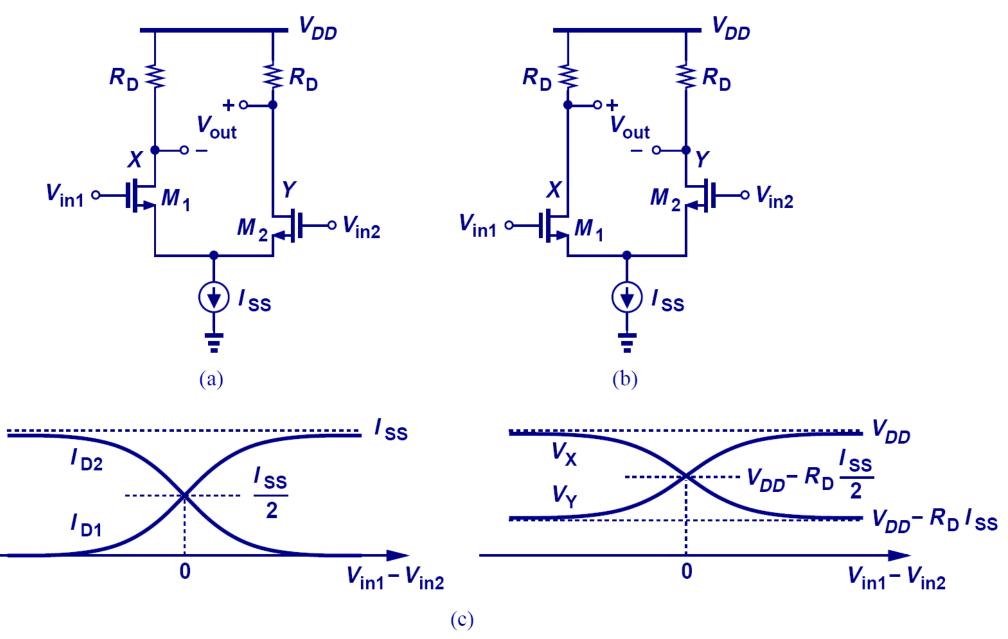

### **Differential Response**

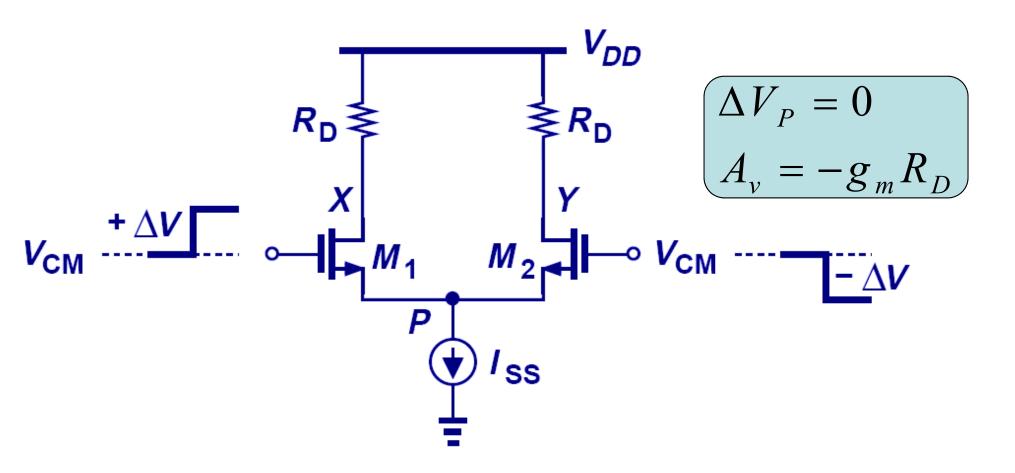

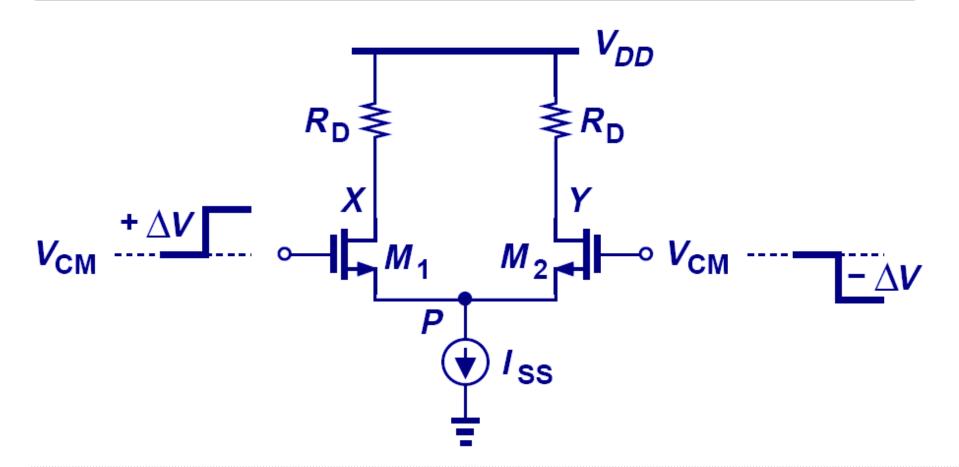

## **Small-Signal Response**

Similar to its bipolar counterpart, the MOS differential pair exhibits the same virtual ground node and small signal gain.

## **Power and Gain Tradeoff**

In order to obtain the source gain as a CS stage, a MOS differential pair must dissipate twice the amount of current (assuming the same MOSFET overdrive voltage). This power and gain tradeoff is also echoed in its bipolar counterpart.

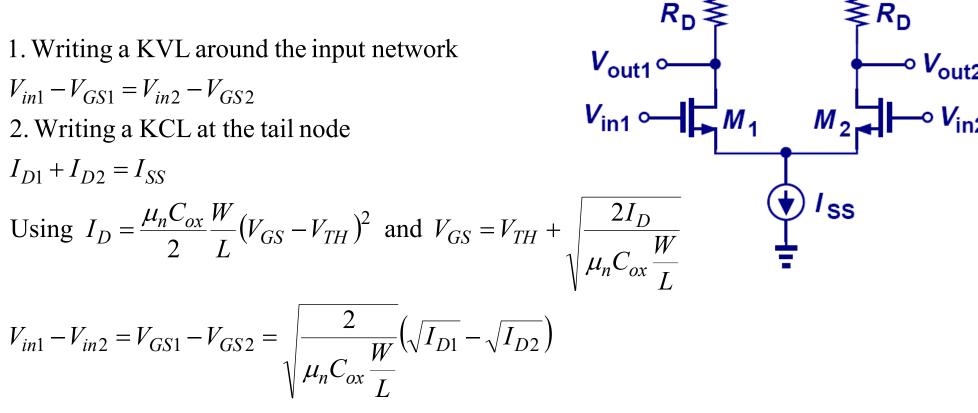

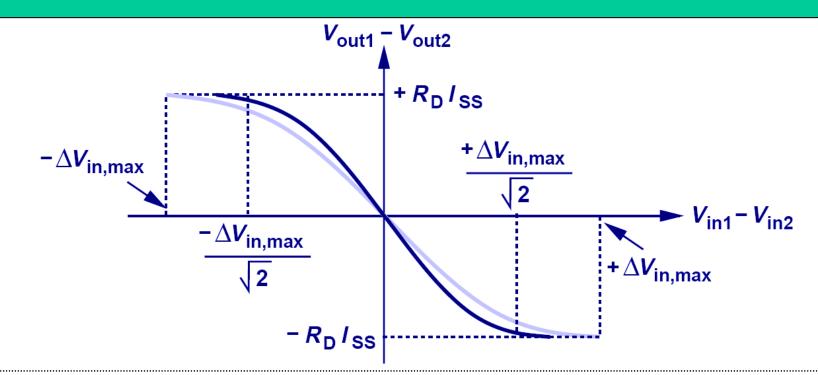

### **MOS Differential Pair's Large-Signal Response**

Squaring both sides

$$(V_{in1} - V_{in2})^2 = \frac{2}{\mu_n C_{ox}} \frac{W}{L} \left( I_{D1} + I_{D2} - 2\sqrt{I_{D1}I_{D2}} \right) = \frac{2}{\mu_n C_{ox}} \frac{W}{L} \left( I_{SS} - 2\sqrt{I_{D1}I_{D2}} \right)$$

CH 10 Differential Amplifiers

$V_{DD}$

### **MOS Differential Pair's Large-Signal Response**

After some algebraic manipulations (see Razavi 10.3.2), can show that

$$I_{D1} = \frac{I_{SS}}{2} + \frac{V_{in1} - V_{in2}}{4} \sqrt{\mu_n C_{ox} \frac{W}{L} \left[ 4I_{SS} - \mu_n C_{ox} \frac{W}{L} (V_{in1} - V_{in2})^2 \right]}$$

$$I_{D2} = \frac{I_{SS}}{2} + \frac{V_{in2} - V_{in1}}{4} \sqrt{\mu_n C_{ox} \frac{W}{L} \left[ 4I_{SS} - \mu_n C_{ox} \frac{W}{L} (V_{in2} - V_{in1})^2 \right]}$$

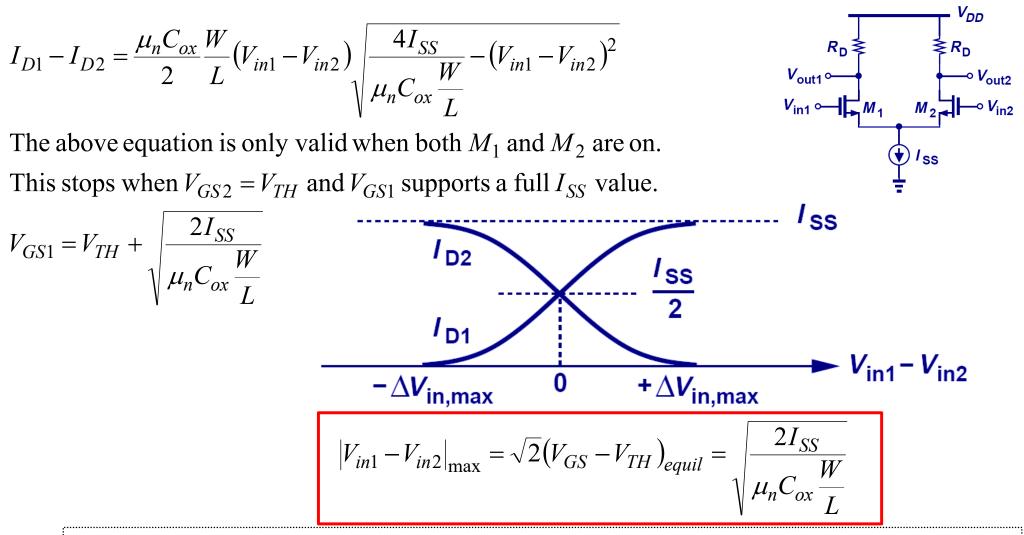

\*Note, this equation is only valid for a certain maximum input differential voltage  $V_{in1} - V_{in2}$

### **Maximum Differential Input Voltage**

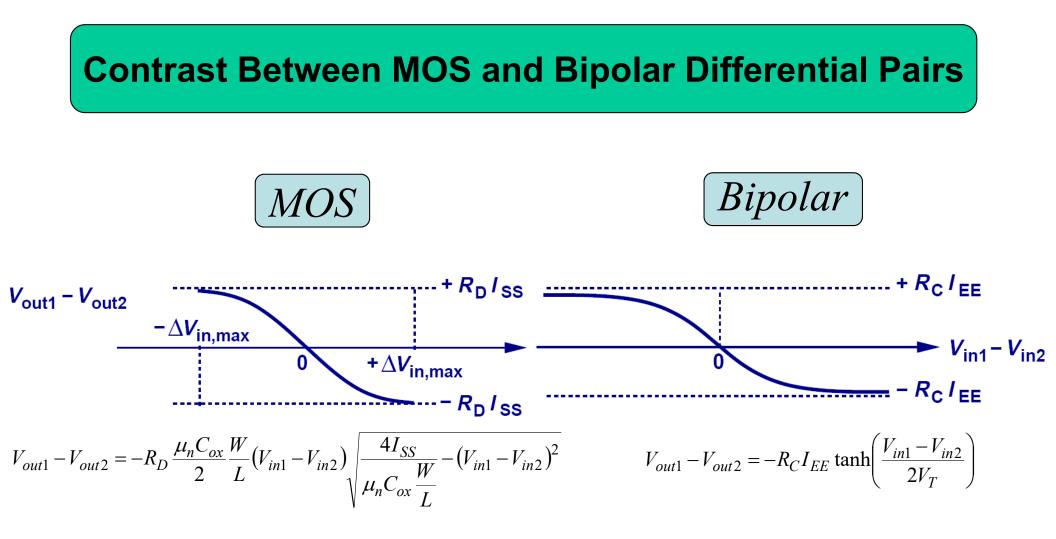

There exists a finite differential input voltage that completely steers the tail current from one transistor to the other. This value is known as the maximum differential input voltage. CH 10 Differential Amplifiers

In a MOS differential pair, there exists a finite differential input voltage to completely switch the current from one transistor to the other, whereas, in a bipolar pair that voltage is infinite.

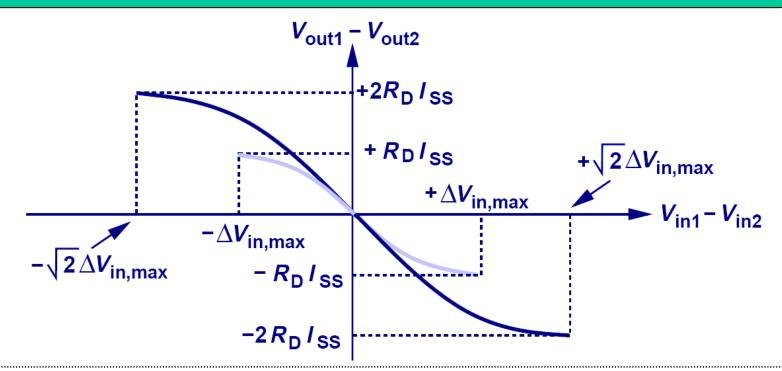

### The effects of Doubling the Tail Current

- Since I<sub>SS</sub> is doubled and W/L is unchanged, the equilibrium overdrive voltage for each transistor must increase by  $\sqrt{2}$  to accommodate this change, thus  $\Delta V_{in,max}$  increases by  $\sqrt{2}$  as well. Moreover, since I<sub>SS</sub> is doubled, the differential output swing will double.

- > Small signal gain also increases by  $\sqrt{2}$

- Linear input range increases, assuming RD value is small enough to keep transistors in saturation

## The effects of Doubling W/L

- Since W/L is doubled and the tail current remains unchanged, the equilibrium overdrive voltage will be lowered by  $\sqrt{2}$  to accommodate this change, thus  $\Delta V_{in,max}$  will be lowered by  $\sqrt{2}$  as well. Moreover, the differential output swing will remain unchanged since neither  $I_{SS}$  nor  $R_D$  has changed

- > Small signal gain increases by  $\sqrt{2}$

- Linear input range decreases

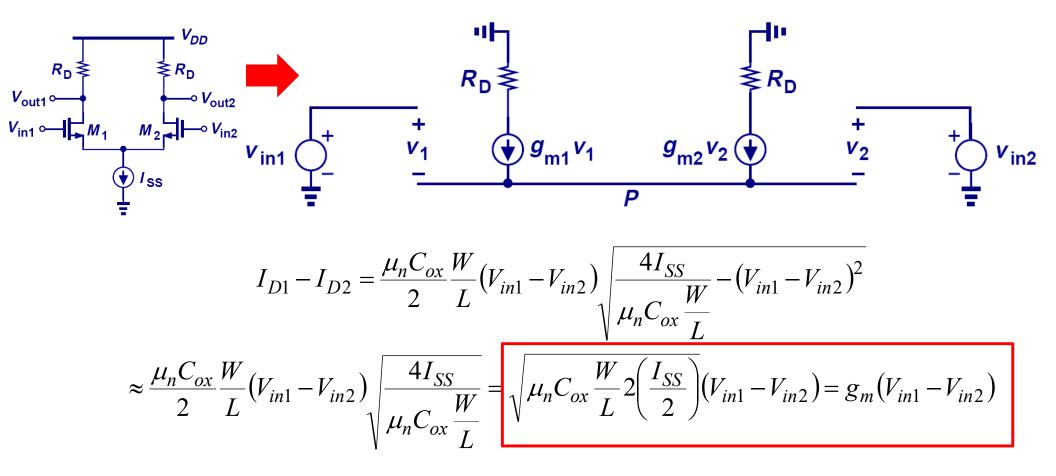

## **Small-Signal Analysis of MOS Differential Pair**

> When the input differential signal is small compared to  $4I_{ss}/\mu_nC_{ox}(W/L)$ , the output differential current is linearly proportional to it, and small-signal model can be applied.

## **Virtual Ground and Half Circuit**

Applying the same analysis as the bipolar case, we will arrive at the same conclusion that node P will not move for small input signals and the concept of half circuit can be used to calculate the gain.

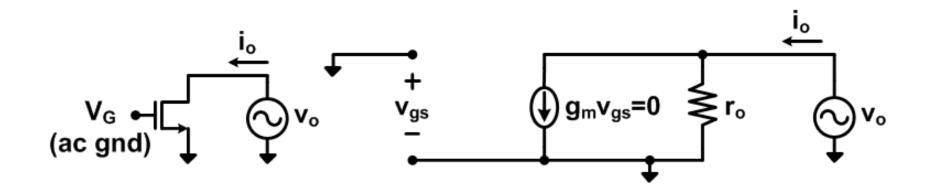

# Small-Signal Impedance: Simple Current Source (Finite r<sub>o</sub>)

$$r_{out} = \frac{1}{g_o}$$

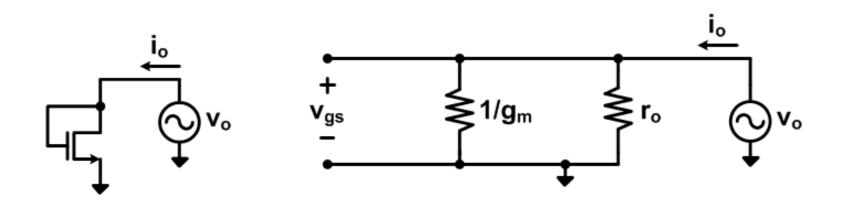

# Small-Signal Impedance: "Diode" Load (Finite r<sub>o</sub>)

$$r_{out} = \frac{1}{g_m} \left\| r_o = \frac{1}{g_m + g_o} \approx \frac{1}{g_m} \right\|$$

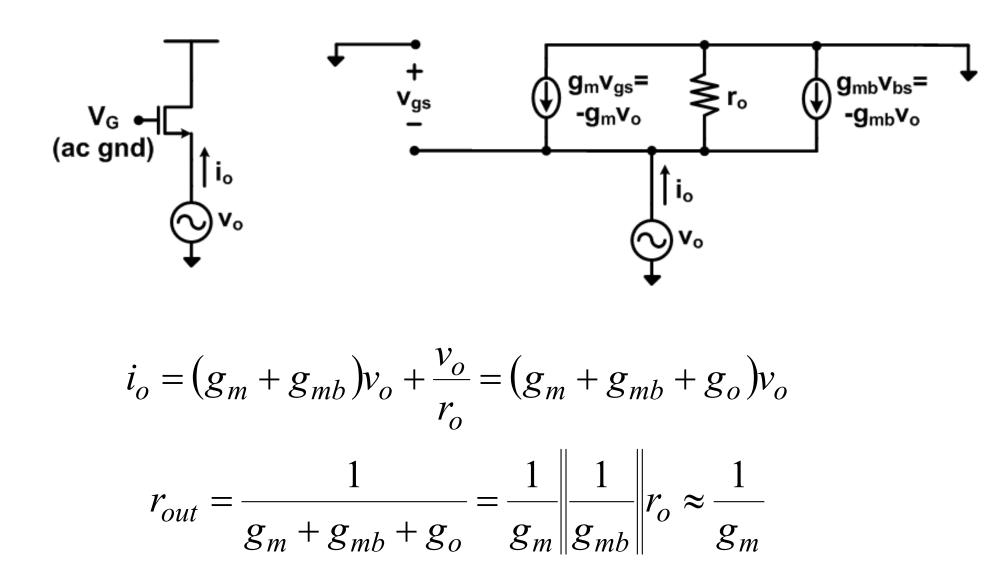

# Small-Signal Impedance: Looking Into Source (Finite r<sub>o</sub> and g<sub>mb</sub>)

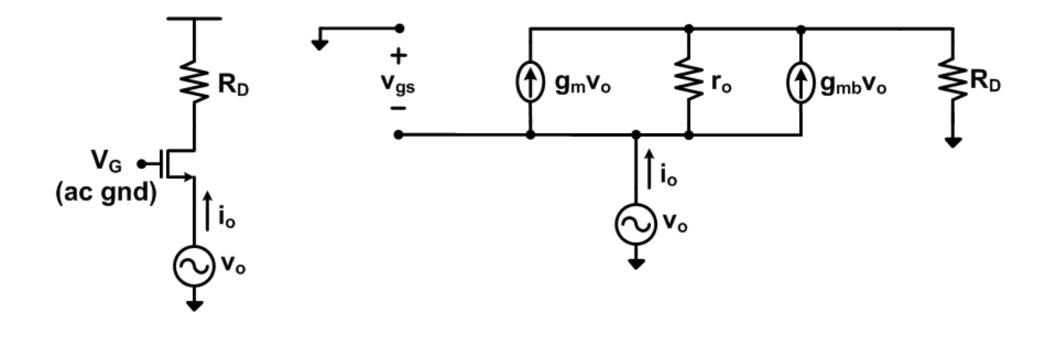

# Small-Signal Impedance: Looking Into Source w/ R<sub>D</sub> (Finite r<sub>o</sub> and g<sub>mb</sub>)

$$r_{out} = \frac{1}{g_m + g_{mb} + g_o} \left( 1 + \frac{R_D}{r_o} \right)$$

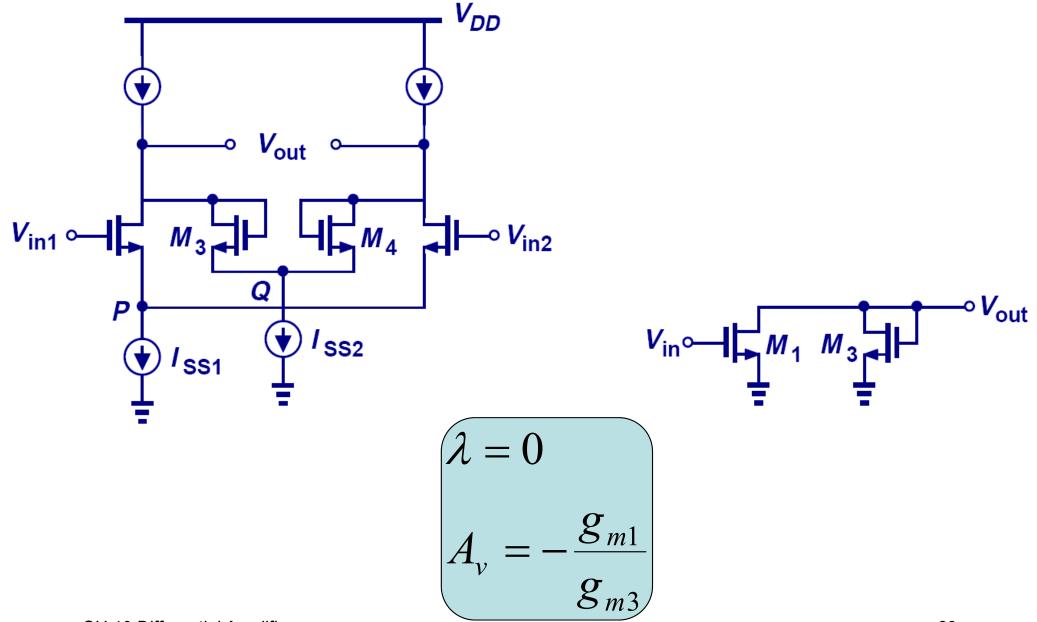

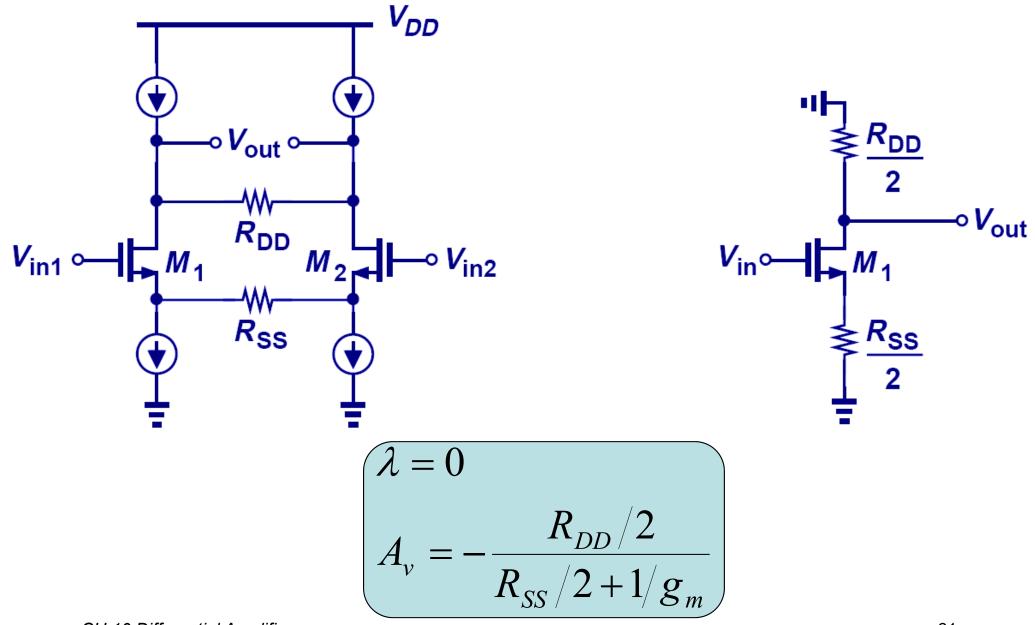

### **MOS Differential Pair Half Circuit Example I**

### **MOS Differential Pair Half Circuit Example II**

CH 10 Differential Amplifiers

60

### **MOS Differential Pair Half Circuit Example III**

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

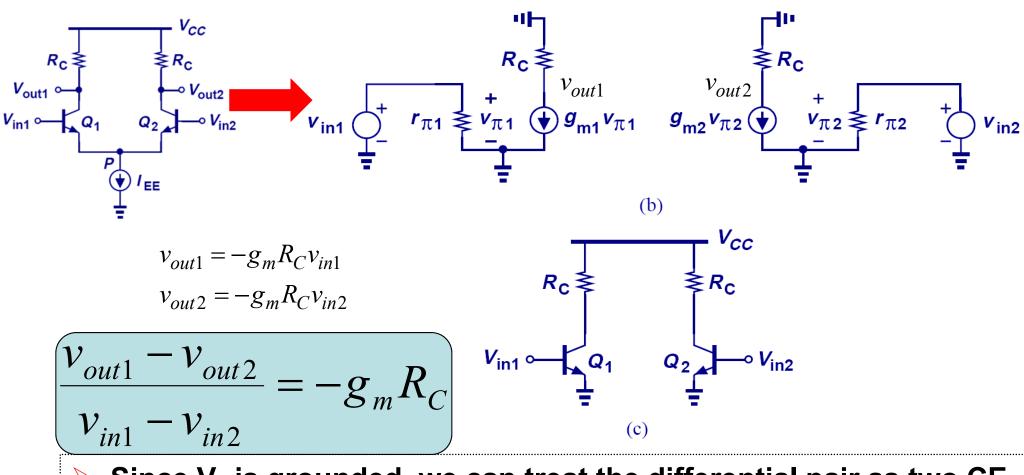

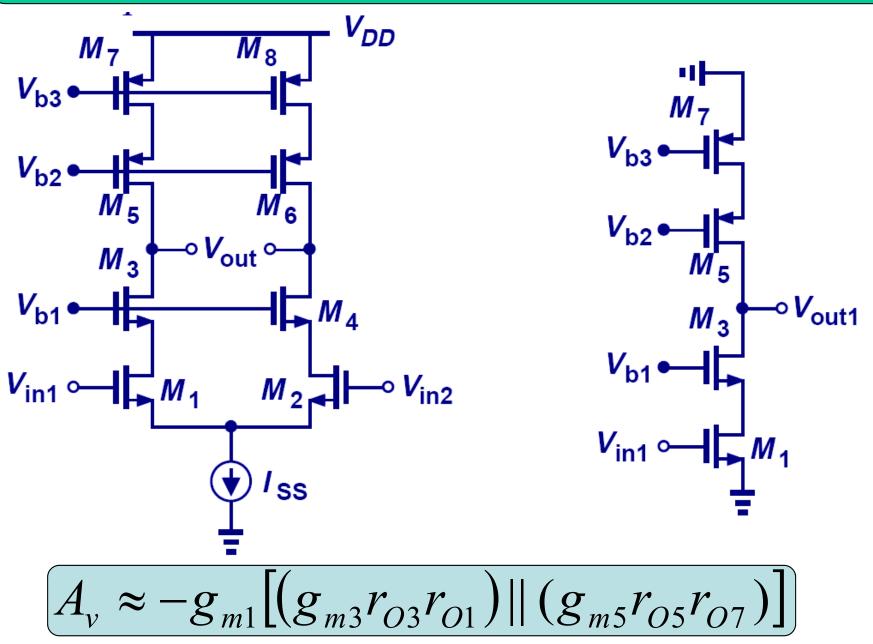

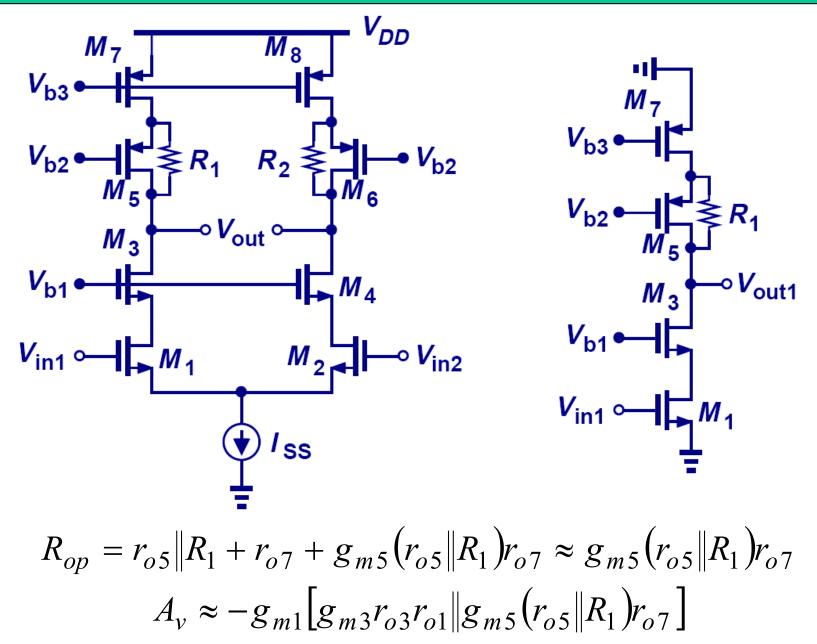

# Maximum Differential Amplifier Gain

$$\frac{v_{out1} - v_{out2}}{v_{in1} - v_{in2}} = -g_m r_0$$

w/ finite r<sub>o</sub>

- With ideal current source loads, the differential gain is limited by the intrinsic transistor gain (g<sub>m</sub>r<sub>o</sub>)

- How to increase the gain further?

- Use a topology which boosts the output resistance

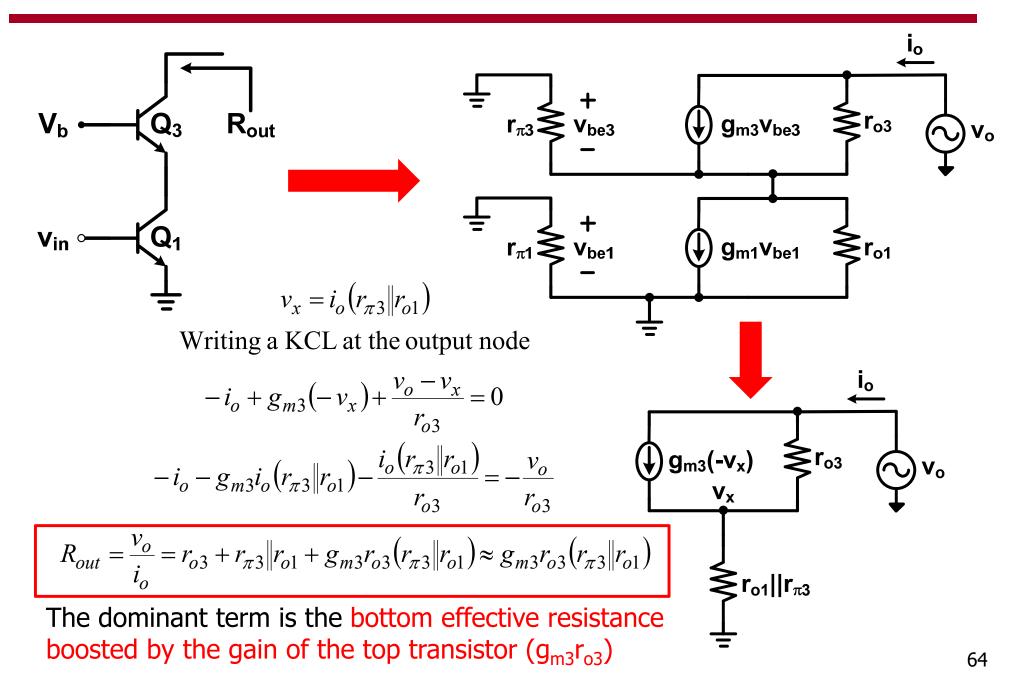

# **Bipolar Cascode Topology**

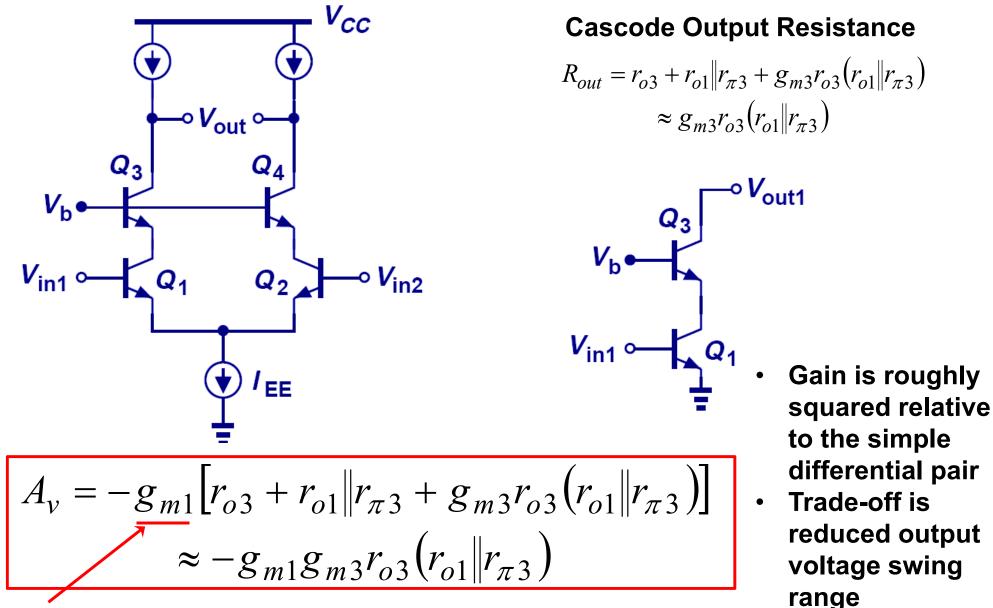

### **Bipolar Cascode Differential Pair**

Slight approximation here. More when we study Cascodes in detail.

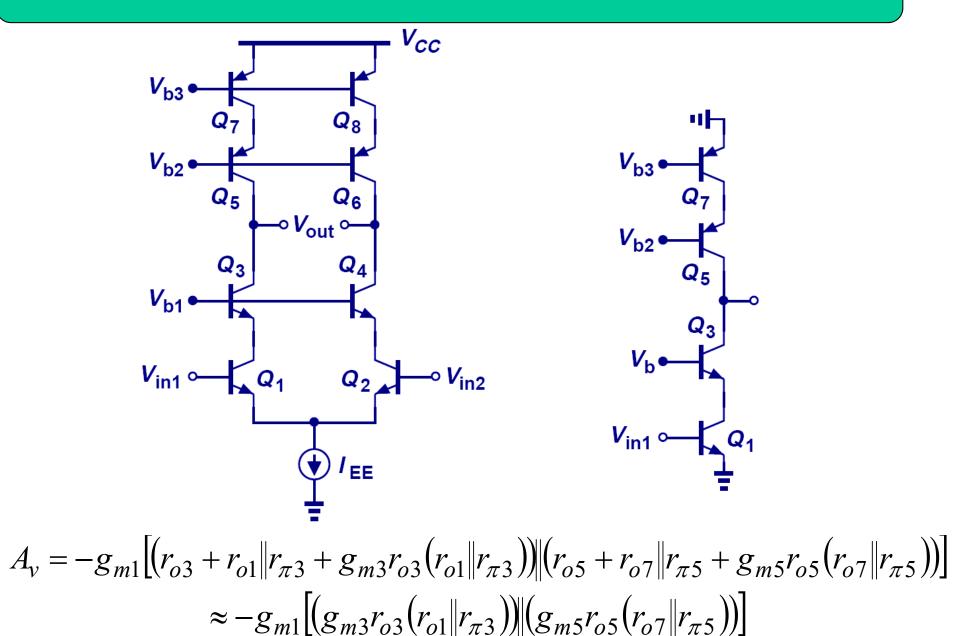

#### **Bipolar Telescopic Cascode**

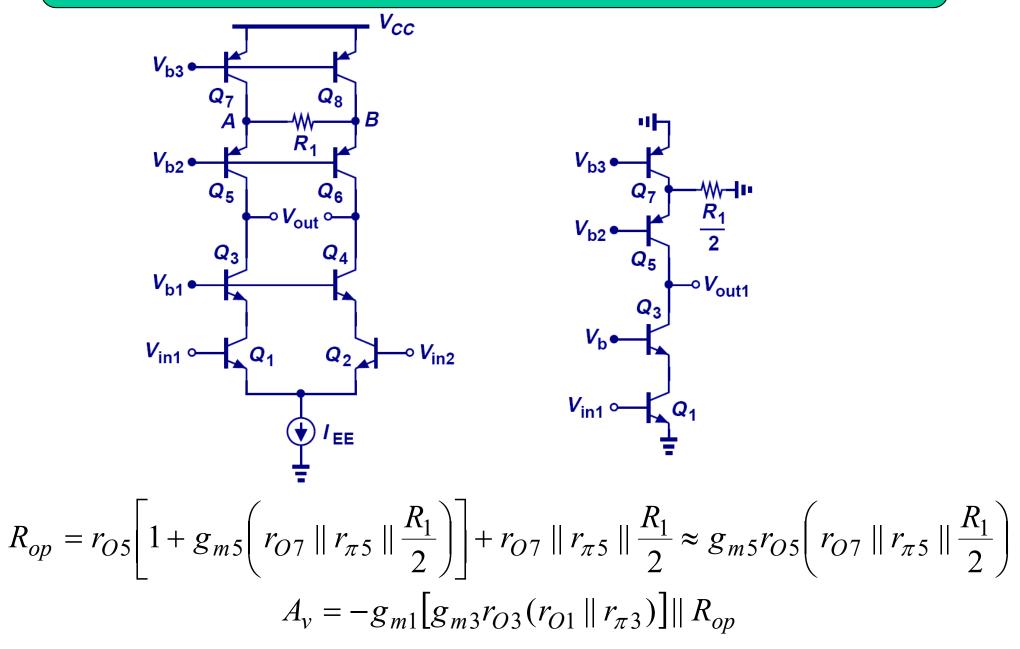

#### **Example: Bipolar Telescopic Parasitic Resistance**

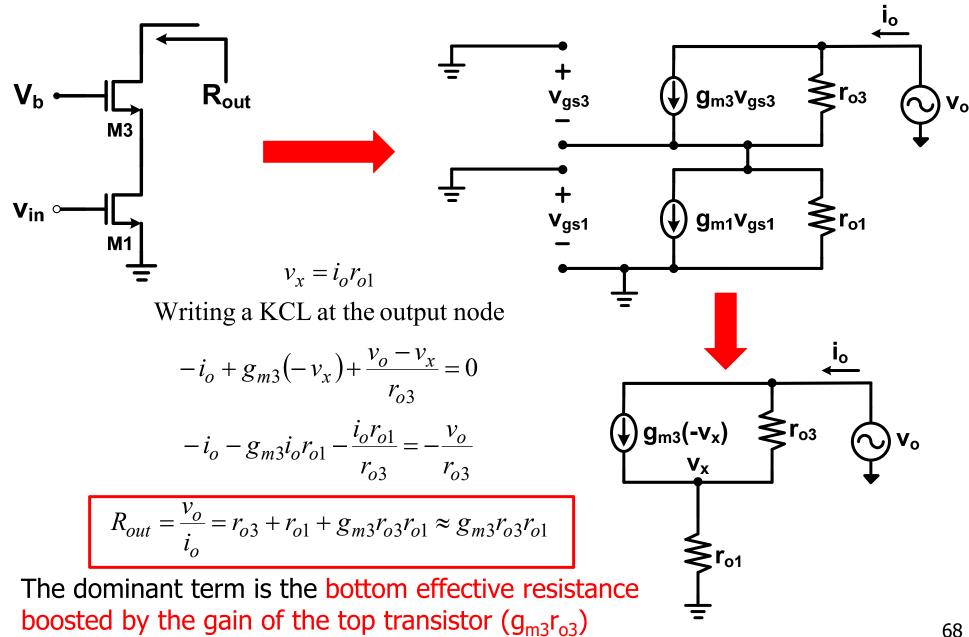

# MOS Cascode Topology

### **MOS Cascode Differential Pair**

$V_{b1}$

V<sub>in1</sub>

Cascode

Output

Resistance

$$R_{out} = r_{o3} + r_{o1} + g_{m3}r_{o3}r_{o1}$$

$\approx g_{m3}r_{o3}r_{o1}$

$M_3$

- Gain is roughly squared relative to the simple differential pair

- Trade-off is reduced output voltage swing range

$A_{v} = -g_{m1} [r_{o3} + r_{o1} + g_{m3} r_{o3} r_{o1}]$

$\approx -g_{m1}g_{m3}r_{o3}r_{o1}$

#### **MOS Telescopic Cascode**

#### **Example: MOS Telescopic Parasitic Resistance**

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

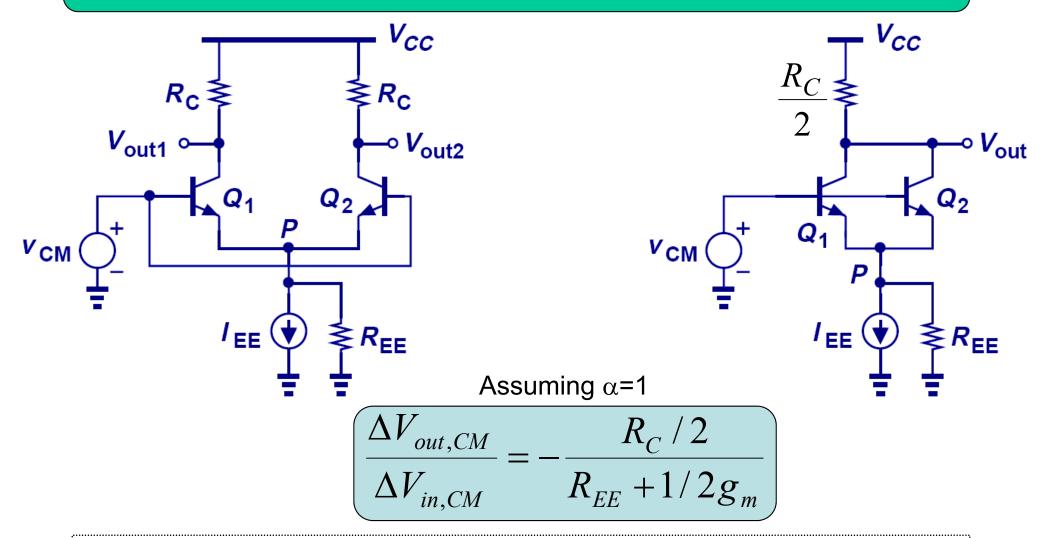

## **Effect of Finite Tail Impedance**

If the tail current source is not ideal, then when a input CM voltage is applied, the currents in Q<sub>1</sub> and Q<sub>2</sub> and hence output CM voltage will change.

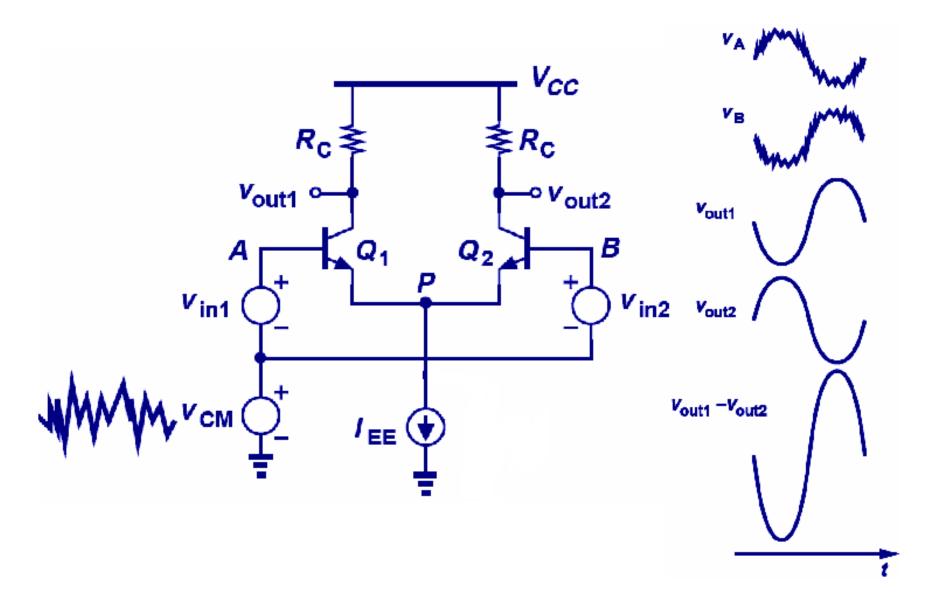

#### **Input CM Noise with Ideal Tail Current**

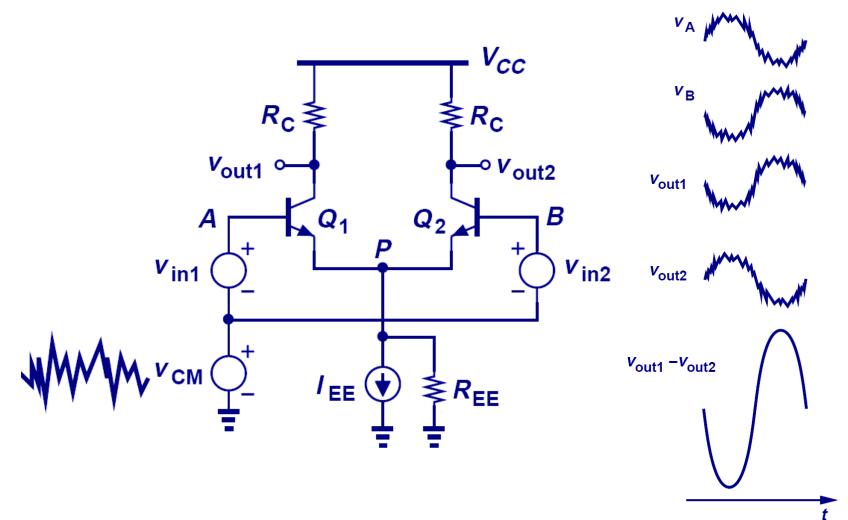

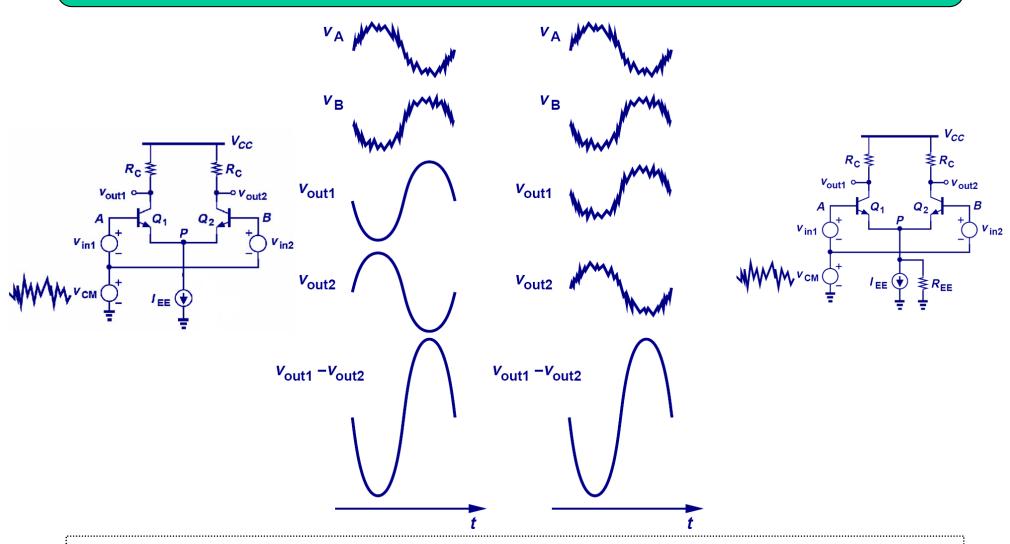

### Input CM Noise with Non-ideal Tail Current

- Common-mode noise is now transferred to the single-ended outputs

- However, output differential signal is still ideally unaffected by common-mode noise CH 10 Differential Amplifiers 75

#### Comparison

As it can be seen, the differential output voltages for both cases are the same. So for small input CM noise, the differential pair is not affected.

CH 10 Differential Amplifiers

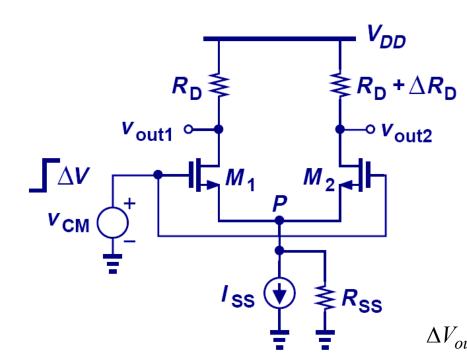

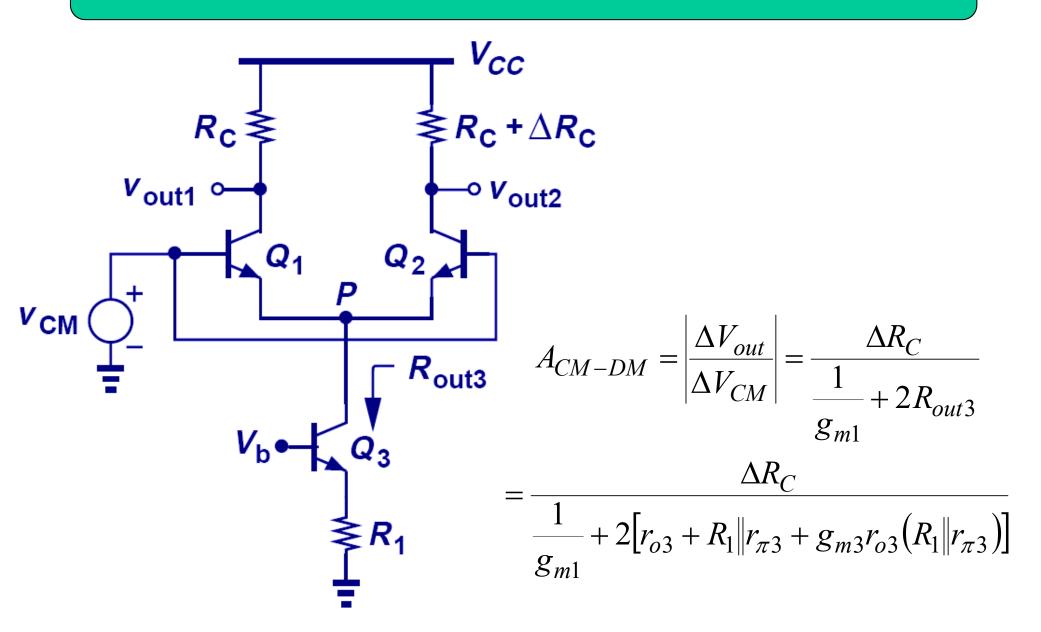

## CM to DM Conversion, A<sub>CM-DM</sub>

Assuming high  $r_o$  in the diff. pair transistors  $\Delta I_{D1} = \Delta I_{D2} = \Delta I_D$  and  $\Delta V_{GS1} = \Delta V_{GS2} = \Delta V_{GS}$ A net current of  $2\Delta I_D$  will flow through  $R_{SS}$   $\Delta V_{CM} = \Delta V_{GS} + 2\Delta I_D R_{SS}$   $\Delta V_{CM} = \Delta I_D \left(\frac{1}{g_m} + 2R_{SS}\right)$   $\Delta I_D = \frac{\Delta V_{CM}}{\frac{1}{g_m} + 2R_{SS}}$   $\Delta V_{out} = \Delta V_{out1} - \Delta V_{out2} = \Delta I_D R_D - \Delta I_D (R_D + \Delta R_D) = -\Delta I_D \Delta R_D$  $\Delta V_{out} = -\frac{\Delta V_{CM}}{\frac{1}{1}} \Delta R_D$

If finite tail impedance and asymmetry are both present, then the differential output signal will contain a portion of input common-mode signal.

$$\frac{1}{g_m} + 2R_{SS}$$

$$\frac{\Delta V_{out}}{\Delta V_{CM}} = \frac{\Delta R_D}{\frac{1}{g_m} + 2R_{SS}}$$

# Example: A<sub>CM-DM</sub>

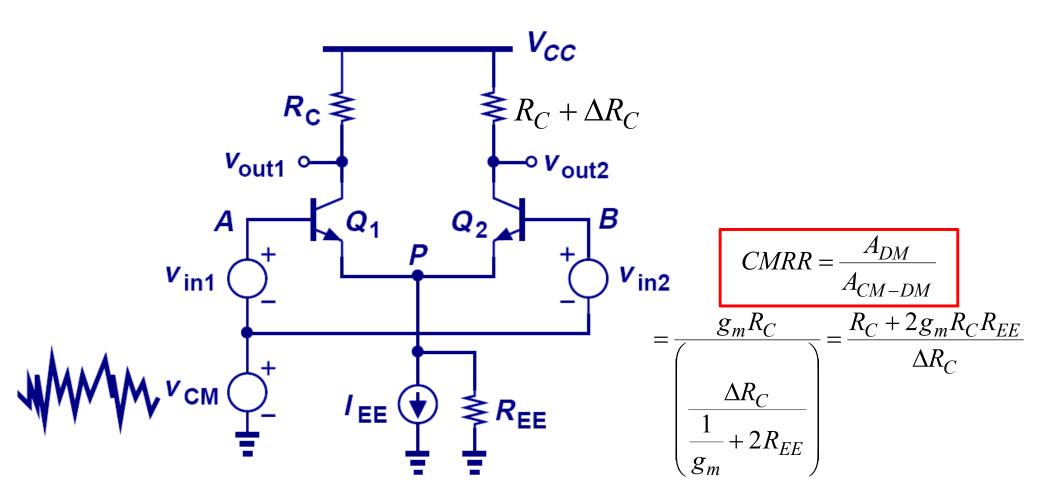

#### **CMRR**

CMRR defines the ratio of wanted amplified differential input signal to unwanted converted input common-mode noise that appears at the output.

- General considerations

- Bipolar differential pair

- MOS differential pair

- Cascode differential amplifiers

- Common-mode rejection

- Differential pair with active load

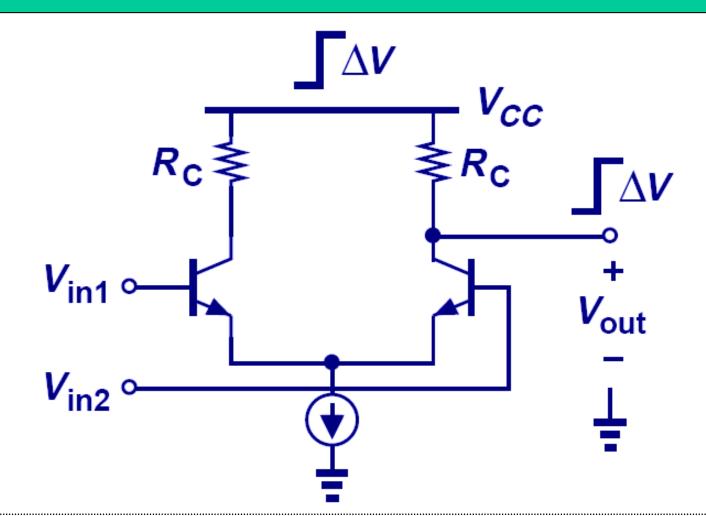

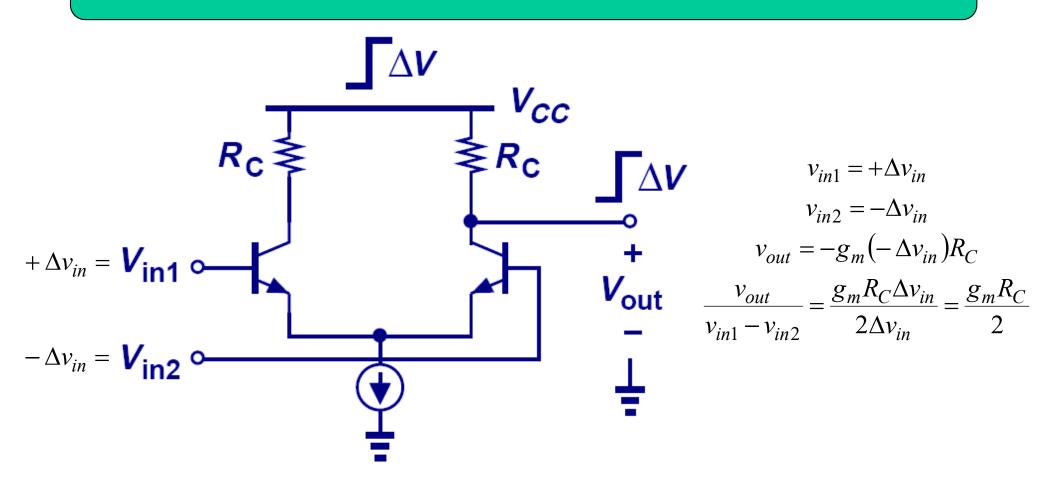

#### **Differential to Single-ended Conversion**

Many circuits require a differential to single-ended conversion, however, the above topology is not very good.

# **Supply Noise Corruption**

The most critical drawback of this topology is supply noise corruption, since no common-mode cancellation mechanism exists. Also, we lose half of the signal.

### **Gain Reduction**

The most critical drawback of this topology is supply noise corruption, since no common-mode cancellation mechanism exists. Also, we lose half of the signal.

This circuit topology performs differential to single-ended conversion with no loss of gain.

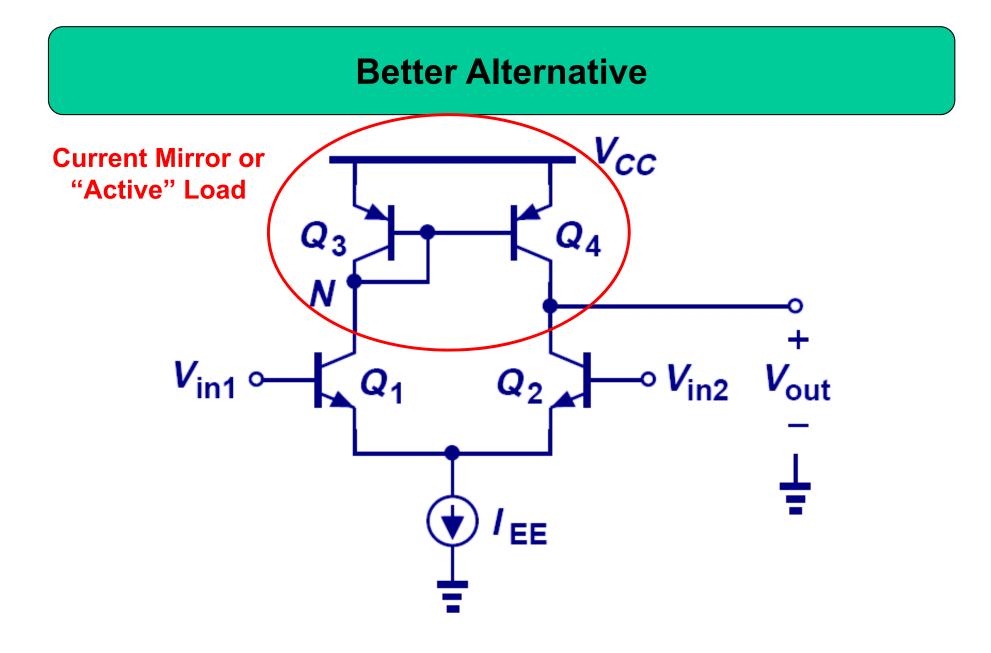

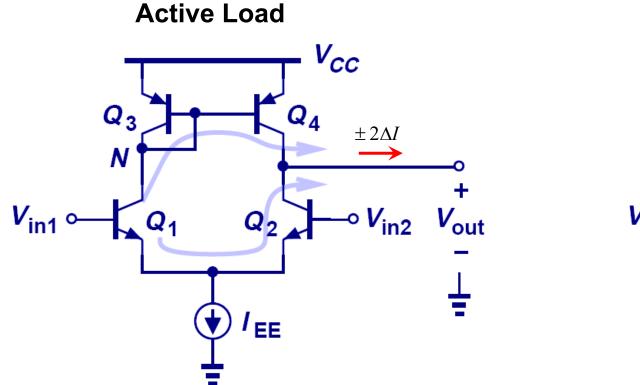

#### **Active Load**

- > With current mirror used as the load, the signal current produced by the  $Q_1$  can be replicated onto  $Q_4$ .

- This type of load is different from the conventional "static load" and is known as an "active load".

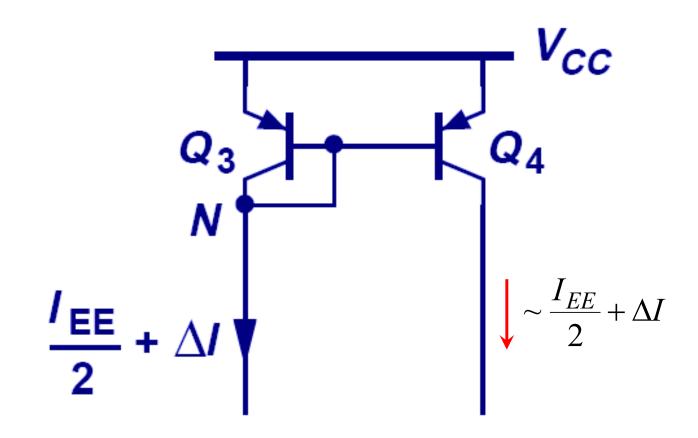

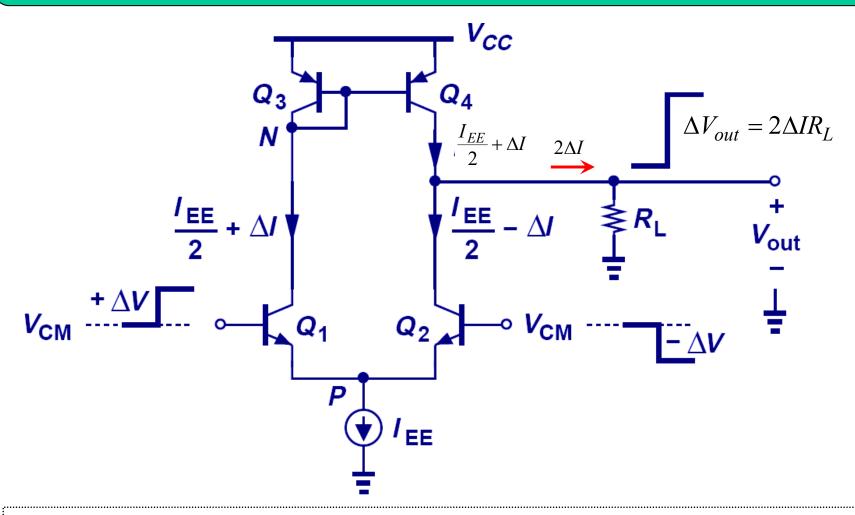

#### **Differential Pair with Active Load**

> The input differential pair decreases the current drawn from  $R_L$  by  $\Delta I$  and the active load pushes an extra  $\Delta I$  into  $R_L$  by current mirror action; these effects enhance each other.

#### Active Load vs. Static Load

**Static Load**

#### The load on the left responds to the input signal and enhances the single-ended output, whereas the load on the right does not.

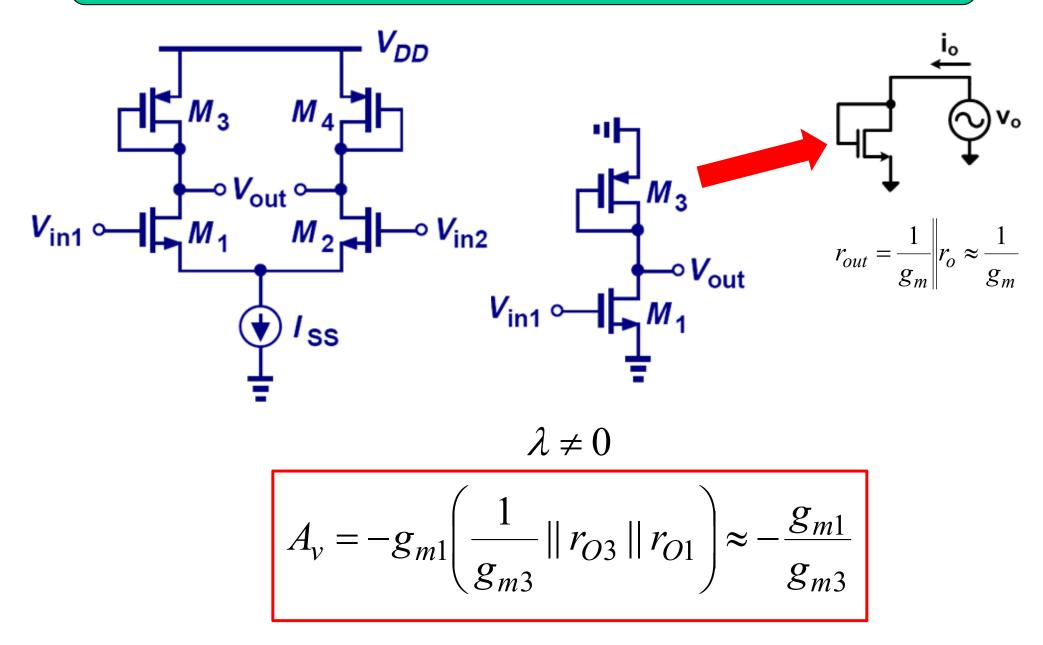

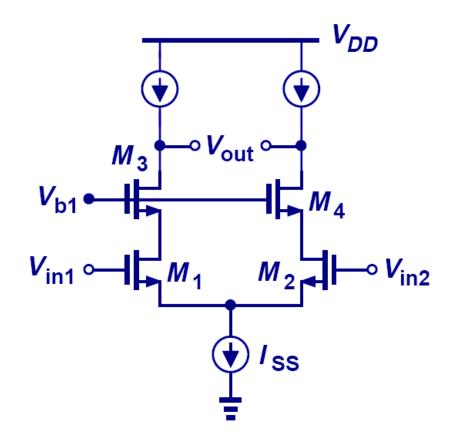

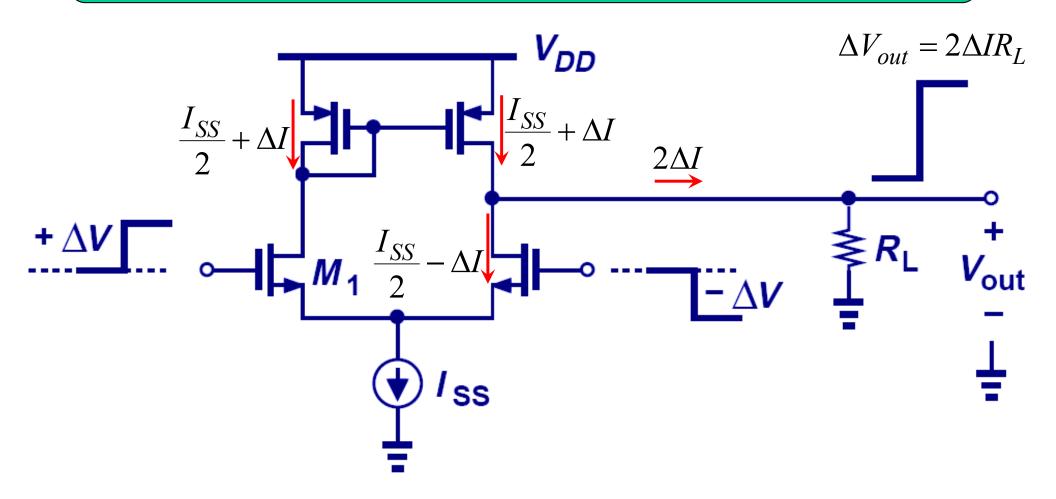

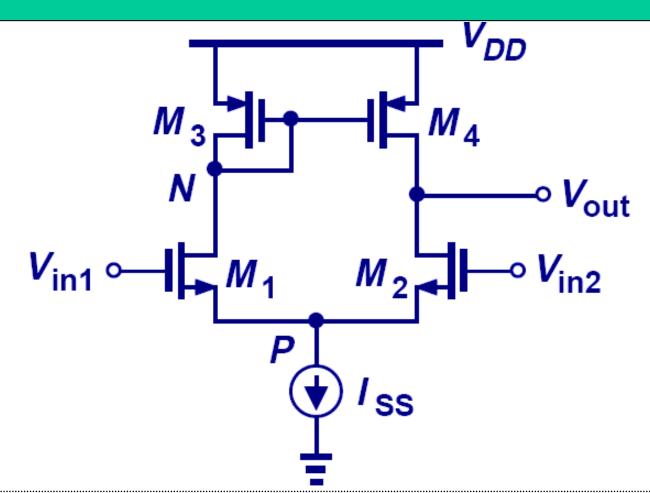

### **MOS Differential Pair with Active Load**

Similar to its bipolar counterpart, MOS differential pair can also use active load to enhance its single-ended output.

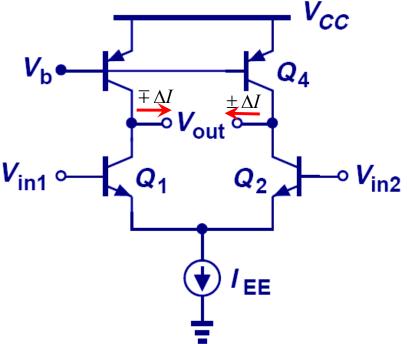

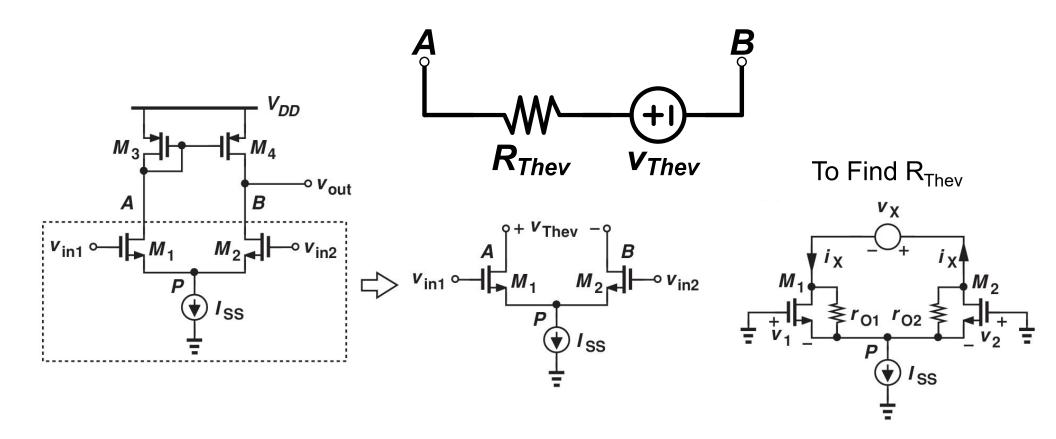

# **Asymmetric Differential Pair**

Because of the vastly different resistance magnitude at the drains of M<sub>1</sub> and M<sub>2</sub>, the voltage swings at these two nodes are different and therefore node P cannot be viewed as a virtual ground.

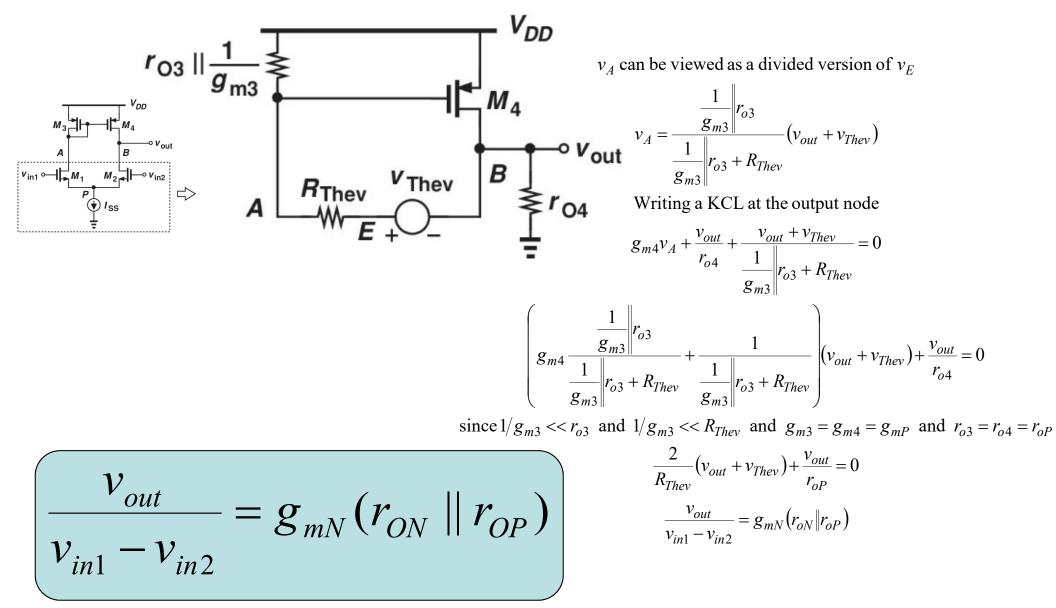

#### **Thevenin Equivalent of the Input Pair**

$$\begin{aligned} v_{Thev} &= -g_{mN} r_{oN} (v_{in1} - v_{in2}) \\ R_{Thev} &= 2r_{oN} \end{aligned}$$

CH 10 Differential Amplifiers

#### **Simplified Differential Pair with Active Load**

CH 10 Differential Amplifiers

# Next Time

- Cascode Stages & Current Mirrors

- Razavi Chapter 9