# ECEN 326 Lab 3 Design of a Two-Stage MOSFET Amplifier

### **Circuit Topology**

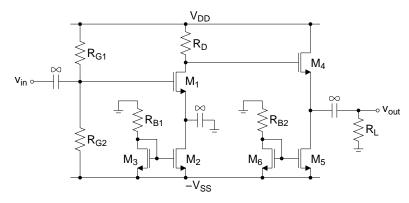

The following figure shows the two-stage dual-supply MOSFET amplifier circuit that will be designed in this lab.

DC drain currents of  $M_1$  and  $M_4$  are set by the two current mirrors as follows:

$$I_{D1} = I_{D2} = I_{D3} = \frac{V_{SS} - V_{GS3}}{R_{B1}} = \frac{k'_n}{2} \frac{W}{L} (V_{GS3} - V_{tn})^2$$

(1)

$$I_{D4} = I_{D5} = I_{D6} = \frac{V_{S5} - V_{GS6}}{R_{B2}} = \frac{k'_n}{2} \frac{W}{L} (V_{GS6} - V_{tn})^2$$

(2)

For  $M_1$ ,  $M_2$  and  $M_5$ , the following should be satisfied for the active operation:

$$V_{DS} \ge V_{ov} = V_{GS} - V_{tn} \tag{3}$$

The signal swing at the drain of  $M_1$  is limited by  $V_{DD}$  and  $-V_{SS} + V_{ov2} + V_{ov1}$ , provided that the gate bias of  $M_1$  is arranged to have the maximum possible swing. However, the minimum value at  $V_{d1}$  is usually limited by  $-V_{SS} + V_{ov5} + V_{GS4}$ , which is typically higher than  $-V_{SS} + V_{ov2} + V_{ov1}$ . In order to maximize the symmetrical swing, the DC bias at  $V_{D1}$  may be centered between the upper and the lower limit. However, centering the DC bias is not always necessary, since it may conflict with other specifications. Nevertheless, the difference between  $V_{D1}$  and the upper or lower limit should be greater than the desired swing at that node.

As in the case of BJT emitter-follower, MOS source follower bias current can be determined from

$$I_{D5} \ge \frac{0\text{-to-peak output swing}}{R_L} \tag{4}$$

AC small-signal parameters can be obtained as:

$$A_{\nu} = \frac{v_{out}}{v_{in}} \approx -\frac{R_D}{\frac{1}{g_{m1}}} \frac{R_L}{R_L + \frac{1}{g_{m4}}} = -g_{m1}R_D \frac{R_L}{R_L + \frac{1}{g_{m4}}}$$

(5)

where

$$g_m = k'_n \frac{W}{L} V_{ov} = \sqrt{2k'_n \frac{W}{L} I_D}$$

(6)

CD4007 transistor array will be used for the implementation of the amplifier. Device parameters of CD4007 are approximately given as follows:

<sup>©</sup> Department of Electrical and Computer Engineering, Texas A&M University

| CD4007N                      | CD4007P                      |

|------------------------------|------------------------------|

| $k'_n = 70 \ \mu A/V^2$      | $k'_{p} = 15 \ \mu A/V^{2}$  |

| $V_{tn} = 1.4 V$             | $\dot{V}_{tp} = -1.65 V$     |

| $W = 170 \ \mu m$            | $W = 360 \ \mu m$            |

| $L = 10 \ \mu m$             | $L = 10 \ \mu m$             |

| $\lambda_n = 0.016 \ V^{-1}$ | $\lambda_{p}=$ 0.01 $V^{-1}$ |

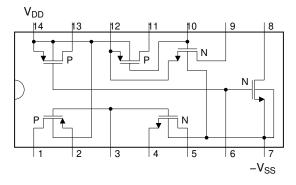

Connection diagram of the CD4007 chip (top view) is shown below.

Note that all P-channel substrates are connected to  $V_{DD}$  and all N-channel substrates are connected to  $-V_{SS}$ .

## **Calculations and Simulations**

Design a common-source MOSFET amplifier with a source follower using the following specifications:

$V_{DD} = V_{SS} = 5 V$   $R_L = 5 k\Omega$  Operating frequency: 5 kHz  $R_{in} \ge 100 k\Omega$   $|A_v| = 30$  Zero-to-peak un-clipped swing at  $V_{out} \ge 2.5 V$  $I_{supply} \le 1.5 mA$

- 1. Show all your calculations, design procedure, and final component values.

- **2.** Verify your results using a circuit simulator. Submit all necessary simulation plots showing that the specifications are satisfied. Also provide the circuit schematic with DC bias points annotated.

- **3.** Using a circuit simulator, perform Fourier analysis and determine the input and the output signal amplitudes resulting in 5% total harmonic distortion (THD) at the output. Provide the simulation results.

#### Measurements

- 1. Construct the amplifier you designed.

- 2. Measure *I*<sub>D1</sub>, *I*<sub>D4</sub>, *V*<sub>D1</sub>, *V*<sub>D2</sub> and *V*<sub>D5</sub>. If any DC bias value (especially *I*<sub>D</sub>) is significantly different than the one obtained from simulations, modify your circuit (i.e. change *R*<sub>B1</sub>, *R*<sub>B2</sub>, *R*<sub>G1</sub>, or *R*<sub>G2</sub>) to get the desired DC bias before you move onto the next step.

- **3.** Measure  $A_v$ ,  $R_{in}$ , and  $I_{supply}$  (for both  $V_{DD}$  and  $-V_{SS}$ ).

- 4. Measure the maximum un-clipped output signal amplitude.

- 5. Find the input signal amplitude resulting in 5% THD measurement at the output.

#### Report

- 1. Include calculations, schematics, simulation plots, and measurement plots.

- 2. Prepare a table showing calculated, simulated and measured results.

- 3. Compare the results and comment on the differences.

## Demonstration

- 1. Construct the amplifier you designed on your breadboard and bring it to your lab session.

- 2. Your name and UIN must be written on the side of your breadboard.

- 3. Submit your report to your TA at the beginning of your lab session.

- **4.** Measure  $A_v$ ,  $R_{in}$ , and  $I_{supply}$  (for both  $V_{DD}$  and  $-V_{SS}$ ).

- **5.** Apply the input signal resulting in 5% THD at the output from your earlier measurements. Show the input and output waveforms, and THD measurement at the output.