## DESIGN OF HIGH-SPEED OPTICAL INTERCONNECT TRANSCEIVERS

A DISSERTATION

### SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

### AND THE COMMITTEE ON GRADUATE STUDIES

### OF STANFORD UNIVERSITY

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

### FOR THE DEGREE OF

### DOCTOR OF PHILOSOPHY

Samuel Palermo

September 2007

© Copyright by Samuel Palermo 2007 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Mark A. Horowitz) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(David A. B. Miller)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Bruce A. Wooley)

Approved for the University Committee on Graduate Studies

iv

# Abstract

The increase in computing power enabled by CMOS scaling has created increased demand for chip-to-chip I/O bandwidth. Unfortunately, inter-chip electrical channel bandwidth has not scaled similarly to on-chip performance, causing current high-speed I/O link designs to be channel limited and require sophisticated equalization circuitry which increases power consumption. Interconnect architectures which employ optical channels have negligible frequency dependent loss and provide a potential path to increased I/O bandwidth without excessive circuit complexity or power consumption.

This dissertation focuses on a dense low-power CMOS optical link architecture which employs novel optical transmitter and receiver circuits and leverages an electrical link technique of time-division multiplexing in order to achieve high-speed operation. Transmitter designs are demonstrated for the two primary high-density optical sources, vertical-cavity surface-emitting lasers (VCSEL) and multiple-quantum-well modulators (MQWM). The implemented VCSEL driver employs simple transmitter equalization techniques in order to extend the effective device bandwidth for a given reliability level. For the MQWM devices, a pulsed-cascode driver supplies an output voltage swing of twice the nominal CMOS power supply without overstressing thin oxide core devices. A low-voltage integrating and double-sampling optical receiver provides adequate sensitivity in a power-efficient manner by avoiding linear high-gain elements. In order to address this receiver's inability to

handle uncoded data, a swing control filter which actively clamps the input signal within the receiver input range is investigated.

Transmitter clock generation uses an adaptive bandwidth phase-locked loop (PLL) for a wide frequency range, while receiver timing recovery is implemented with a dual-loop architecture which employs baud-rate phase detection and feedback interpolation to achieve reduced power consumption. High-precision phase spacing is ensured at both the transmitter and receiver through adjustable delay clock buffers applied independently on a per-phase basis.

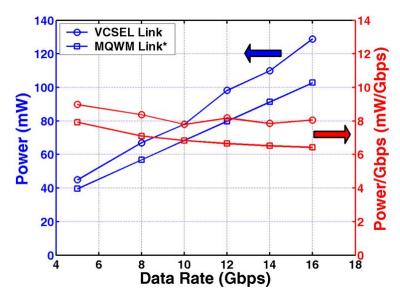

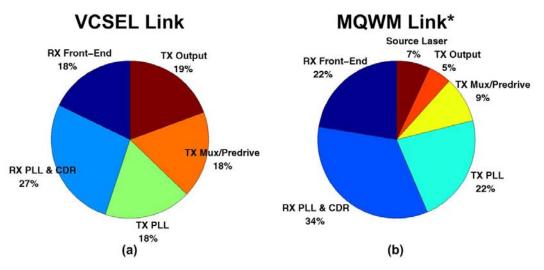

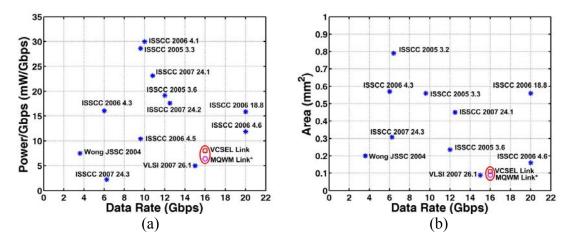

Implemented in a standard 1V 90nm CMOS process, the transceiver operates at data rates between 5 to 16Gb/s. At 16Gb/s, the measure power consumption is 129mW for the VCSEL-based link and projected at 103mW for the modulator-based link, with both links occupying an area close to 0.1mm<sup>2</sup>.

# Acknowledgments

In the time I spent at Stanford, I was able to experience an enormous amount of educational, professional, and personal growth due to the guidance and support of many people.

I am very lucky to have had the opportunity to work with an excellent research advisor, Prof. Mark Horowitz. His unequivocal technical expertise, teaching skills, and the unique ability to motivate through simultaneously challenging and encouraging ideas place him at the apex of the scientific research community. Mark's mentoring served as a key stabilizing force as I experienced the ebb and flow of doctoral research.

I would also like to especially thank some of the key faculty and researchers that I had the pleasure of working with at Stanford. I am grateful to my associate advisor, Prof. Miller, for introducing me to the exciting field of photonics and showing me many amazing technological applications. I would like to thank him for providing me the opportunity to collaborate with his students on several projects and for being a member of my oral defense and reading committees. I gratefully acknowledge Prof. Bruce Wooley for his teaching, support, and for taking the time to read this thesis. I also thank Dr. Tim Drabik for expanding my knowledge of VCSELs.

I have truly enjoyed and greatly benefited from the interaction with an amazing group of research colleagues at Stanford. I am extremely indebted to Azita Emami-

Neyestanak, with whom I collaborated on much of the optical high-speed link work. Special thanks are also in order for Bita Nezamfar, Dinesh Patil, and Patrick Chang for their assistance at various stages in the design of my final optical interconnect testchip. I am grateful for the opportunity to collaborate on research projects with Aparna Bhatnagar and Jon Roth from Prof. Miller's group. For their technical interaction and friendship, I would like to thank the following members of the Horowitz Group: Hae-Chang Lee, Vladimir Stojanović, Elad Alon, Dean Liu, Valentin Abramazon, Ken Mai, Jaeha Kim, Amir Amirkhany, Xiling Shen, Ron Ho, Jim Weaver, Bennett Wilburn, Francois Labonte, and Alex Solomatnikov. Also, from Prof. Miller's Group, Salman Latif, Noah Helman, and Henry Chin deserve special recognition.

I wish to thank the National Science Foundation, MARCO IFC, and Texas Instruments for their financial support. Also, donated resources from ST Microsystems, National Semiconductor, CMP, Emcore, Ulm Photonics, and Albis Optoelectronics enabled this research. Special thanks are in order for Bhusan Gupta and Greg Watson for assisting in establishing CAD infrastructure. I also sincerely thank Teresa Lynn, Penny Chumley, and Ann Guerra for their administrative support

The circuit design knowledge and experience I gained from my studies at Texas A&M University allowed me to hit the ground running at Stanford. For this, I thank Dr. José Pineda de Gyvez, Prof. Edgar Sánchez-Sinencio, and Dr. Sherif H. K. Embabi.

My parents have been a source of encouragement and support throughout my life. I especially thank my mother Georgia for her unconditional love and strength, which continued even after I moved her grandson halfway across the country. I also thank my other parents (in-laws), Tom Ed and Michelle, for their unwavering love and support. Finally, I am forever indebted to my wife Shawn and two sons, Nicholas and Kyle, whose immeasurable love has supported me throughout this journey. For that, I dedicate this thesis to them.

# **Table of Contents**

| Abstract                                                                                                          | •••••• <b>v</b> |

|-------------------------------------------------------------------------------------------------------------------|-----------------|

| Acknowledgments                                                                                                   | vii             |

| Table of Contents                                                                                                 | ix              |

| List of Tables                                                                                                    | xi              |

| List of Figures                                                                                                   | xii             |

| Chapter 1 Introduction                                                                                            | 1               |

| 1.1 Organization                                                                                                  |                 |

| Chapter 2 Background                                                                                              | 5               |

| <ul><li>2.1 High-Speed Electrical Links.</li><li>2.1.1 Electrical Link Circuits.</li></ul>                        | 6               |

| <ul><li>2.1.2 Electrical Channels</li><li>2.1.3 Channel Equalization and Advanced Modulation Techniques</li></ul> |                 |

| 2.2 High-Speed Optical Links<br>2.2.1 Optical Channels                                                            |                 |

| 2.2.2 Optical Transmitters<br>2.2.3 Optical Receivers                                                             | 24              |

| 2.3 Summary                                                                                                       |                 |

| Chapter 3 Optical Transmitter Design                                                                              |                 |

| 3.1 Multiplexing Transmitter                                                                                      |                 |

| 3.2 VCSEL Driver Output Stage                                                                                     |                 |

| 3.2.2 VCSEL Driver Output Stage Implementation                                                                    |                 |

| 3.2.3 Power and Area Overheads of the Equalizing Transmitter                                                      |                 |

| 3.2.4 Experimental Results                                |     |

|-----------------------------------------------------------|-----|

| 3.3 Modulator Driver Output Stage                         |     |

| 3.3.1 Previous High-Voltage Output Stage Implementations  |     |

| 3.3.2 Modulator Driver Output Stage Implementation        |     |

| 3.3.3 Experimental Results                                |     |

| 3.4 Summary                                               |     |

| Chapter 4 Optical Receiver Design                         | 71  |

| 4.1 Low-Voltage Integrating and Double-Sampling Front-End |     |

| 4.1.1 Receiver Operation                                  |     |

| 4.1.2 Receiver Segments                                   |     |

| 4.1.3 Average Current Generation                          |     |

| 4.1.4 Receiver Performance Analysis                       |     |

| 4.2 Input Swing Control Filter                            |     |

| 4.2.1 Swing Control Filter Overview                       |     |

| 4.2.2 Swing Control Filter Circuits                       |     |

| 4.2.3 Swing Control Filter Performance Issues             |     |

| 4.3 Experimental Results                                  |     |

| 4.4 Summary                                               |     |

| Chapter 5 Clock Generation and Recovery                   |     |

| 5.1 Clock Generation                                      |     |

| 5.1.1 PLL Circuits                                        | 117 |

| 5.2 Clock Recovery                                        | 122 |

| 5.2.1 Phase Detection                                     |     |

| 5.2.2 Dual-Loop CDR                                       |     |

| 5.3 Per-Phase Clock Adjustment                            |     |

| 5.4 Experimental Results                                  |     |

| 5.5 Summary                                               |     |

| Chapter 6 Conclusions                                     |     |

| 6.1 Optical Link Performance Summary                      |     |

| 6.2 Electrical I/O Comparison and Projections             | 141 |

| Bibliography                                              | 144 |

# **List of Tables**

| Table 3.1: | Interconnect and VCSEL simulation parameters                       | .42  |

|------------|--------------------------------------------------------------------|------|

| Table 3.2: | VCSEL transmitter performance summary                              | . 55 |

| Table 3.3: | MQW modulator transmitter performance summary                      | . 69 |

| Table 4.1: | Integrating receiver sensitivity parameters                        | .95  |

| Table 4.2: | Optical receiver performance summary                               | 113  |

| Table 5.1: | Data patterns with phase information for baud-rate phase detection | 126  |

| Table 5.2: | Clocking circuitry performance summary                             | 135  |

# **List of Figures**

| Figure 1.1: | I/O scaling necessity: (a) performance disparity between networking/on-   |

|-------------|---------------------------------------------------------------------------|

| chip p      | rocessing and off-chip bandwidth [2-4], (b) I/O scaling projections [5]2  |

| Figure 1.2: | Wavelength division multiplexing chip-to-chip optical interconnect [12].2 |

| Figure 2.1: | High-speed electrical link system                                         |

| Figure 2.2: | Transmitter output stages: (a) current-mode driver, (b) voltage-mode      |

| driver.     |                                                                           |

| Figure 2.3: | Receiver input stage with regenerative latch [26]8                        |

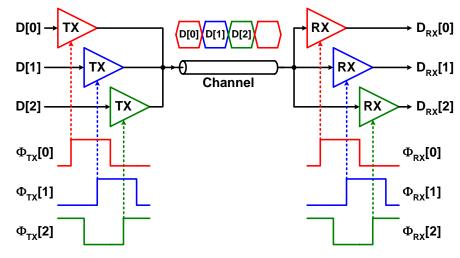

| Figure 2.4: | Time-division multiplexing link9                                          |

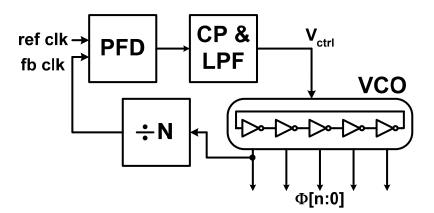

| Figure 2.5: | PLL frequency synthesizer9                                                |

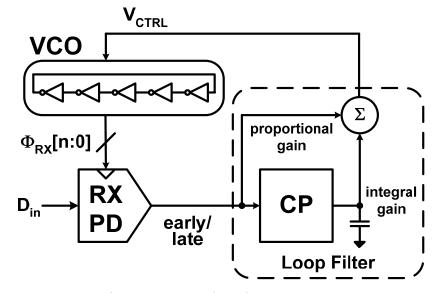

| Figure 2.6: | PLL-based CDR system11                                                    |

| Figure 2.7: | CDR phase detectors: (a) linear [35], (b) binary [36]11                   |

| Figure 2.8: | Backplane system cross-section                                            |

| Figure 2.9: | Frequency response of several backplane channels [41]14                   |

| Figure 2.10 | : Backplane channel performance at 5Gb/s: (a) pulse response, (b) eye     |

| diagra      | n14                                                                       |

| Figure 2.11 | : TX equalization with an FIR filter16                                    |

| Figure 2.12 | : RX equalization with an FIR filter17                                    |

| Figure 2.13 | : Continuous-time equalizing amplifier                                    |

| Figure 2.14 | : RX equalization with a DFE19                                            |

| Figure 2.15: Pulse amplitude modulation - simple binary PAM-2 (1bit/symbol) and           | 1    |

|-------------------------------------------------------------------------------------------|------|

| PAM-4 (2bits/symbol)                                                                      | .20  |

| Figure 2.16: Optical fiber cross-section                                                  | .23  |

| Figure 2.17: VCSEL: (a) device cross-section, (b) electrical model                        | .25  |

| Figure 2.18: VCSEL optical power versus current (L-I) curve                               | .26  |

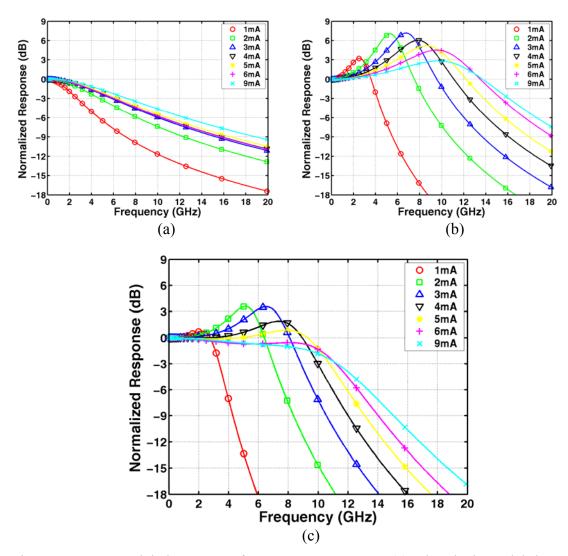

| Figure 2.19: Modeled VCSEL frequency response: (a) electrical model junction              |      |

| resistance current, (b) rate-equation model optical power, (c) cumulative optica          | ıl   |

| power                                                                                     | .27  |

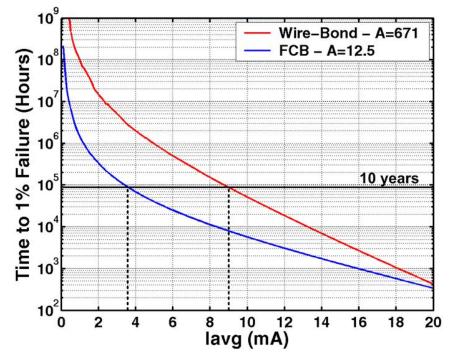

| Figure 2.20: VCSEL MTTF versus average current [75,76]                                    | . 30 |

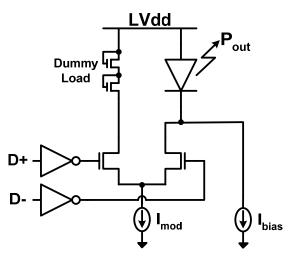

| Figure 2.21: VCSEL current-mode driver                                                    | . 31 |

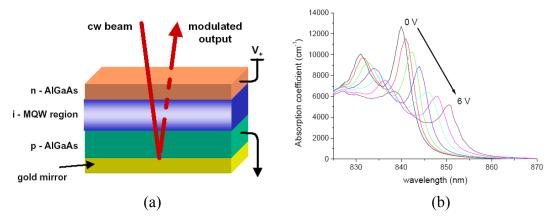

| Figure 2.22: MQWM: (a) device cross-section [84], (b) quantum-confined Stark              |      |

| effect of AlGaAs/GaAs quantum wells [86]                                                  | . 32 |

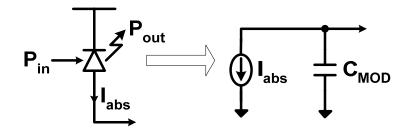

| Figure 2.23: MQWM electrical model                                                        | . 32 |

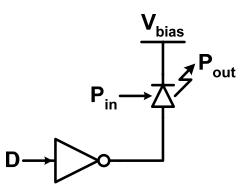

| Figure 2.24: MQWM voltage-mode driver                                                     | . 33 |

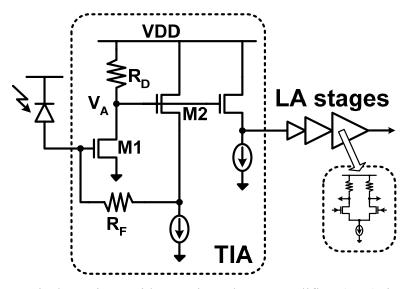

| Figure 2.25: Optical receiver with transimpedance amplifier (TIA) input stage and         |      |

| following limiting amplifier (LA) stages                                                  | .35  |

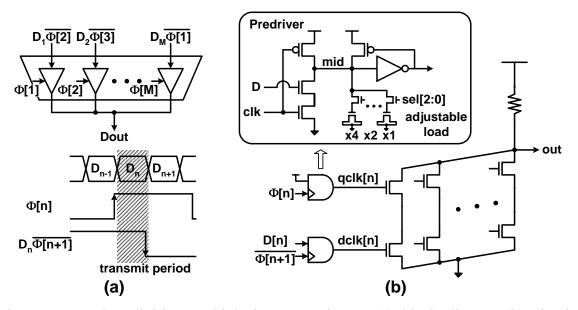

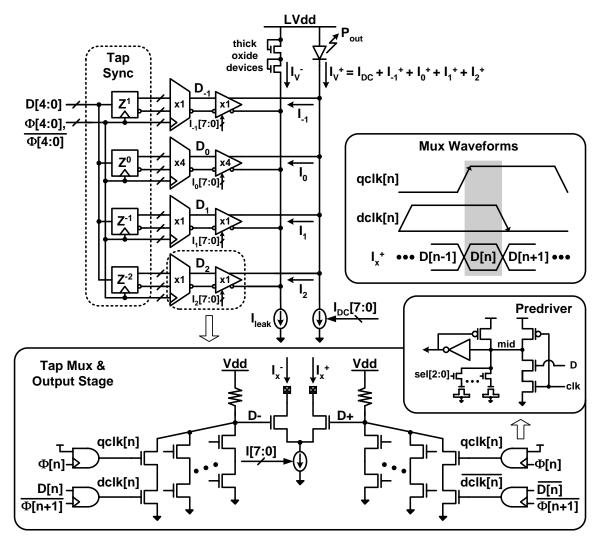

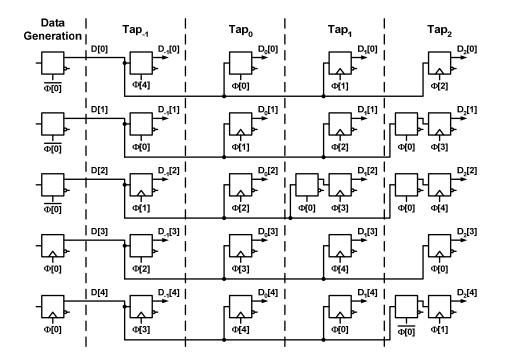

| Figure 3.1: Time-division multiplexing transmitter: (a) block digram, (b) circuit         |      |

| implementation [18]                                                                       | .40  |

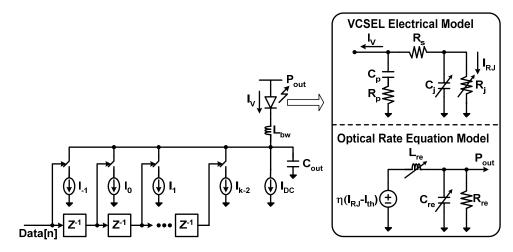

| Figure 3.2: Equalizing VCSEL transmitter simulation model                                 | .42  |

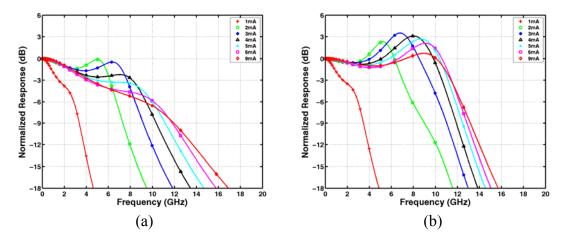

| Figure 3.3: Simulated VCSEL frequency response: (a) flip-chip bond case, (b) wire         | e    |

| bond case                                                                                 | .43  |

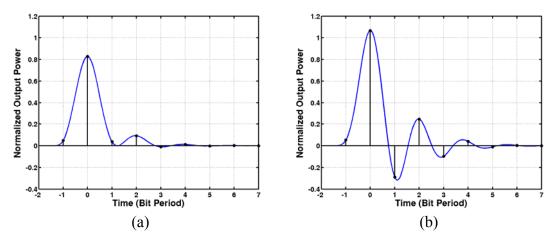

| Figure 3.4: Simulated 16Gbps pulse response of VCSEL with Iavg=5mA: (a) flip-             |      |

| chip bond case, (b) wire bond case                                                        | .44  |

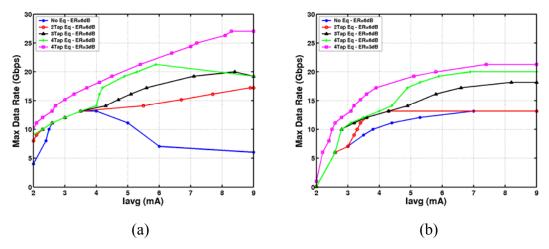

| Figure 3.5: Simulated maximum data rate versus $I_{avg}$ : (a) flip-chip bond case, (b) w | vire |

| bond case                                                                                 | .44  |

| Figure 3.6: VCSEL transmitter                                                             | .47  |

| Figure 3.7: VCSEL transmitter synchronization circuitry                                   | .48  |

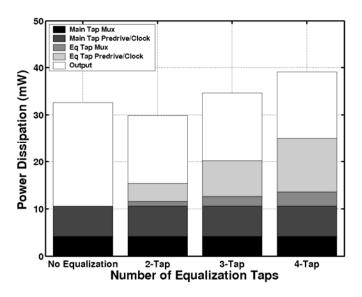

| Figure 3.8: Simulated transmitter power dissipation at 13Gbps with various equaliz        | er   |

| filter lengths – wire bond case                                                           | . 50 |

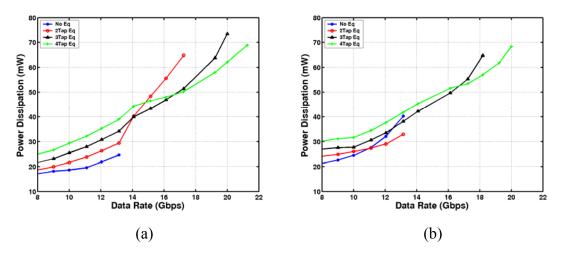

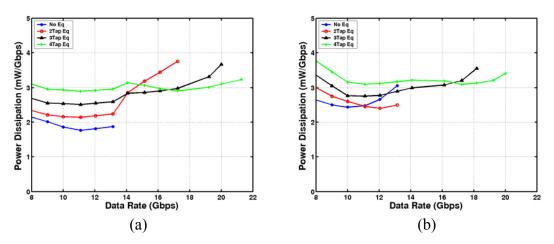

| Figure 3.9: Simulated power dissipation versus data rate for various equalizer length        | IS: |

|----------------------------------------------------------------------------------------------|-----|

| (a) flip-chip bond case, (b) wire bond case                                                  | 51  |

| Figure 3.10: Simulated power dissipation normalized by data rate for various                 |     |

| equalizer lengths: (a) flip-chip bond case, (b) wire bond case                               | 52  |

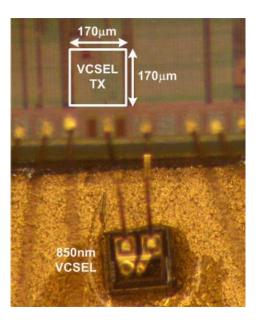

| Figure 3.11: Commercial 10Gbps VCSEL wirebonded to VCSEL transmitter                         | 53  |

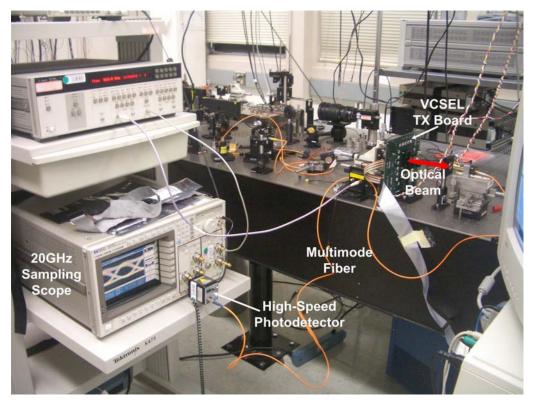

| Figure 3.12: VCSEL transmitter optical test setup                                            | 53  |

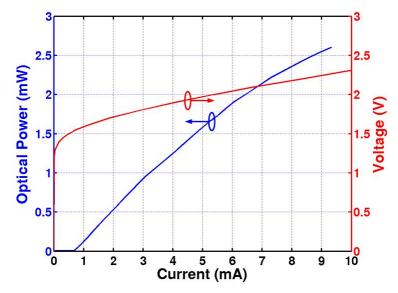

| Figure 3.13: VCSEL optical power and voltage versus DC current                               | 54  |

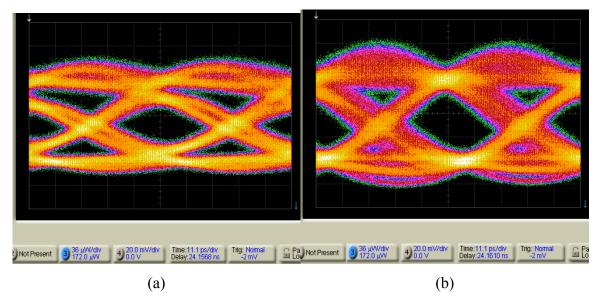

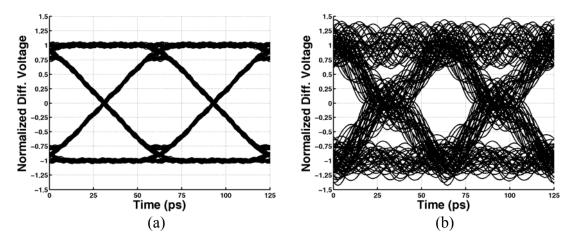

| Figure 3.14: 18Gbps VCSEL optical eye diagrams (ER=3dB): (a) without                         |     |

| equalization, (b) with equalization                                                          | 54  |

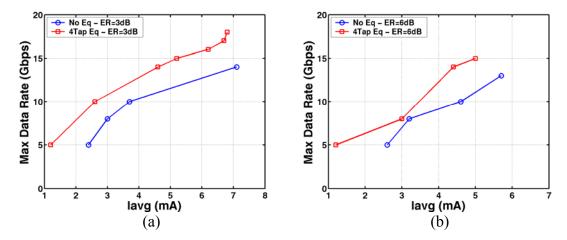

| Figure 3.15: VCSEL maximum data rate versus average current: (a) ER=3dB, (b)                 |     |

| ER=6dB                                                                                       | 55  |

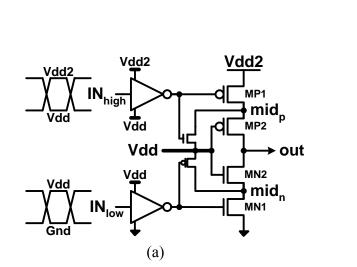

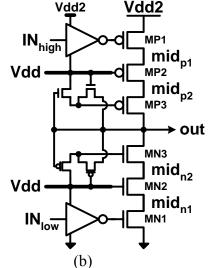

| Figure 3.16: High-voltage output stages: (a) static-biased cascode [100], (b) double-        | -   |

| cascode [102]                                                                                | 57  |

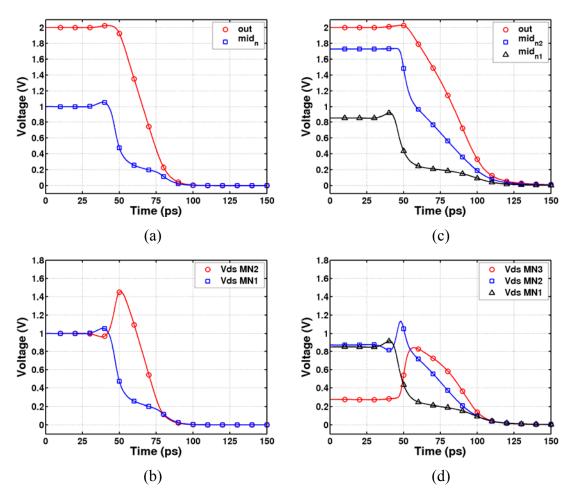

| Figure 3.17: Transient simulation of a falling transition: static-cascode output stage       |     |

| (a) nMOS drain voltages (b) nMOS drain-source voltages; double-cascode                       |     |

| output stage (c) nMOS drain voltages (d) nMOS drain-source voltages                          | 58  |

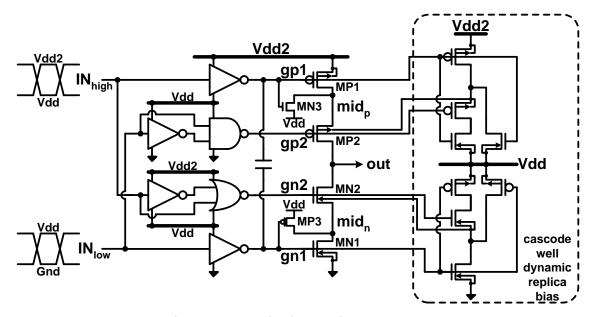

| Figure 3.18: Pulsed-cascode output stage                                                     | 59  |

| Figure 3.19: Transient simulation of pulsed-cascode output stage: falling transition         |     |

| (a) nMOS gate voltages (b) nMOS drain voltages (c) nMOS $V_{gs}$ and $V_{ds}$ , rising       | g   |

| transition (d) pMOS gate voltages (e) pMOS drain voltages (f) pMOS $\left V_{gs}\right $ and | ł   |

| V <sub>ds</sub>                                                                              | 50  |

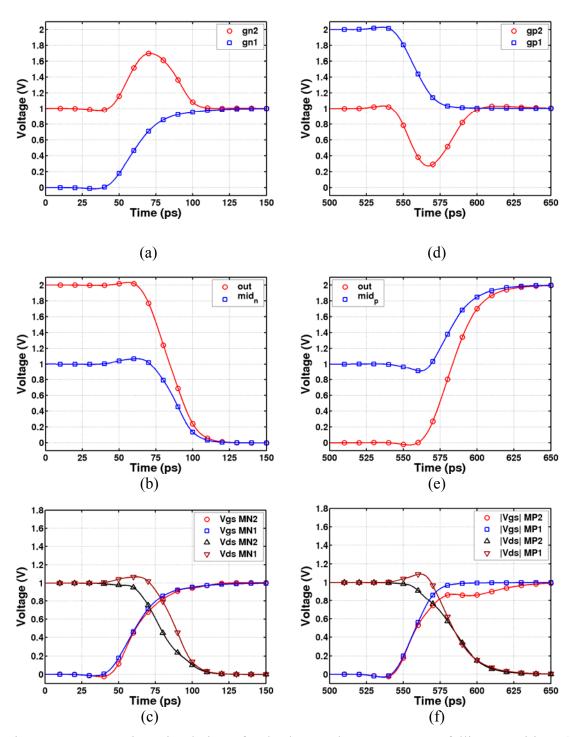

| Figure 3.20: Simulated average output 10-90% transition time versus load-to-input            |     |

| capacitance ratio for static-cascode, double-cascode, pulsed-cascode, and I/O                |     |

| inverter based drivers                                                                       | 51  |

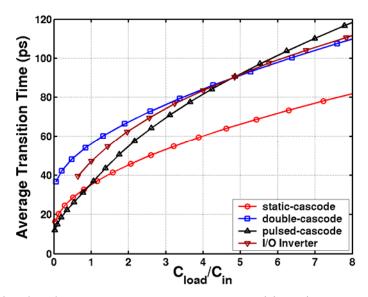

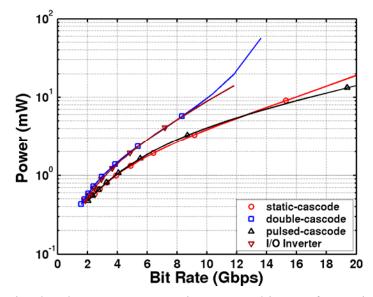

| Figure 3.21: Simulated power consumption versus bit rate for static-cascode, double          | -   |

| cascode, pulsed-cascode, and I/O inverter based drivers                                      | 53  |

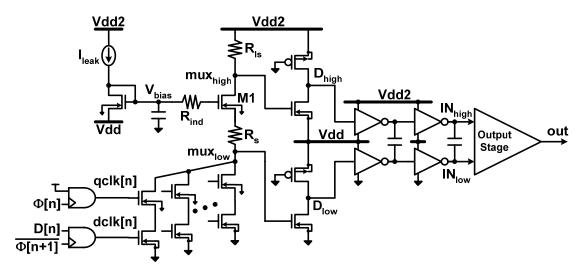

| Figure 3.22: Modulator transmitter with level shifting multiplexer                           | 54  |

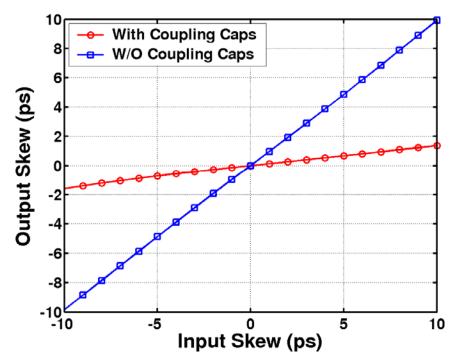

| Figure 3.23: Simulated coupling capacitor skew attenuation between "high" and                |     |

| "low" signal paths                                                                           | 55  |

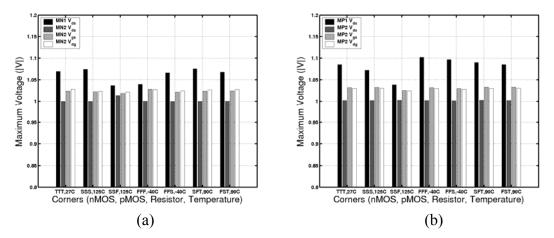

| Figure 3.24: Simulated output stage absolute maximum voltages for random data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inputs: (a) nMOS transistors, (b) pMOS transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

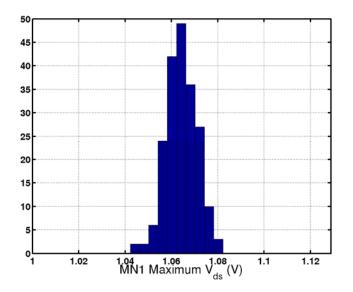

| Figure 3.25: Simulated distribution of MN1 maximum $V_{ds}$ – 200 Monte Carlo runs 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

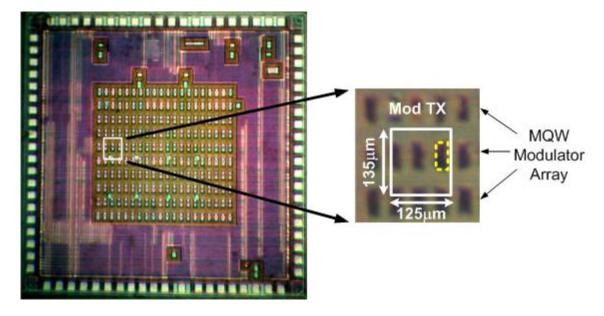

| Figure 3.26: Modulator transmitter on optical transceiver test chip. Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| pictured here are similar to the 850nm AlGaAs devices in [84]67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

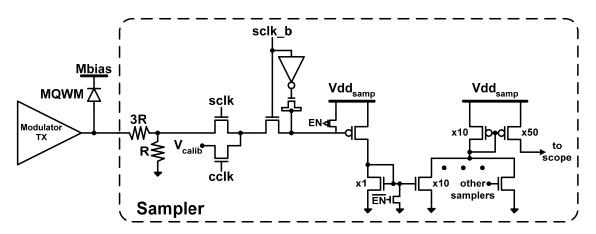

| Figure 3.27: Analog sampler for monitoring modulator transmitter output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

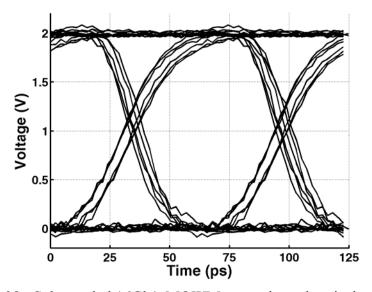

| Figure 3.28: Subsampled 16Gb/s MQWM transmitter electrical eye diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 3.29: Optical 1Gb/s pseudo-eye diagram69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

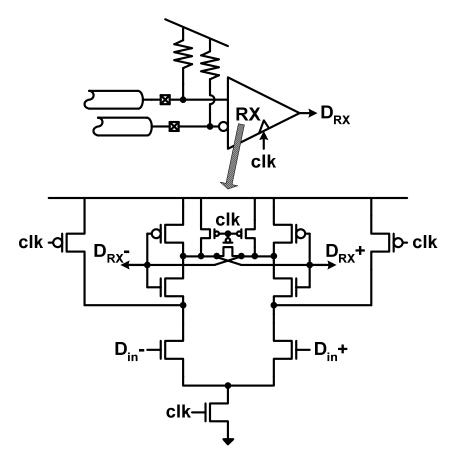

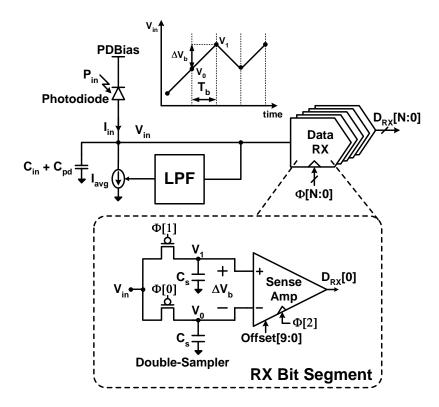

| Figure 4.1: Emami's integrating and double-sampling receiver [13]73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

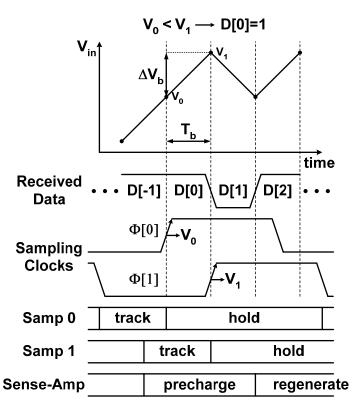

| Figure 4.2: Input voltage waveform and sampling clocks used to generate differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| voltage74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

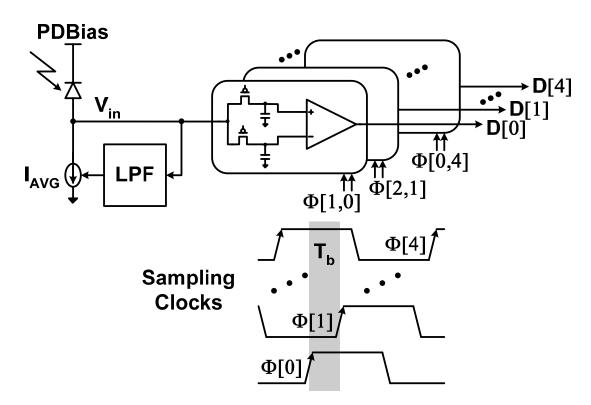

| Figure 4.3: Input demultiplexing receiver using multiple sampler clock phases75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

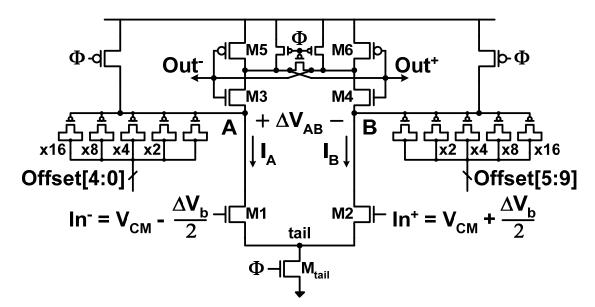

| Figure 4.4: Sense-amplifier with capacitive offset correction76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

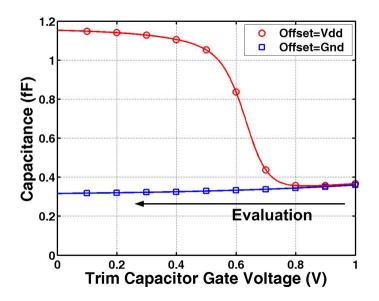

| Figure 4.5: Unit trim capacitance versus gate voltage for <i>Offset=Vdd</i> and <i>Gnd</i> 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

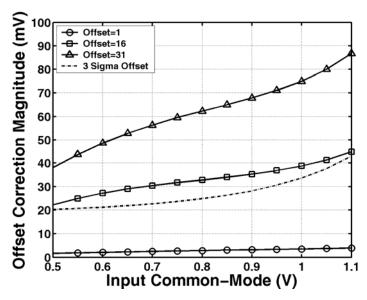

| Figure 4.6: Sense-amplifier input-referred offset correction and 3-sigma offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| i gare not sense amprirer mpar referred officer confection and s signa officer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| magnitude versus input common-mode voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| magnitude versus input common-mode voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

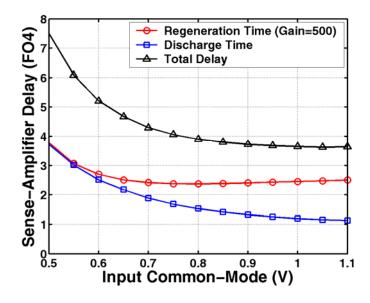

| <ul> <li>magnitude versus input common-mode voltage level</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

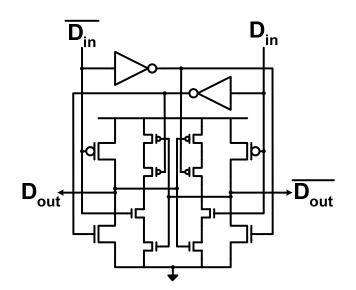

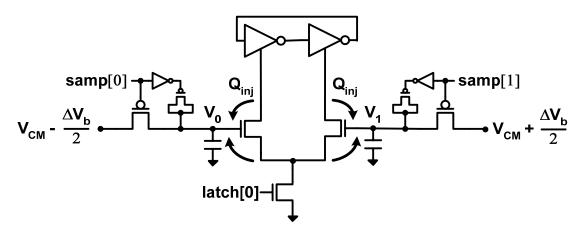

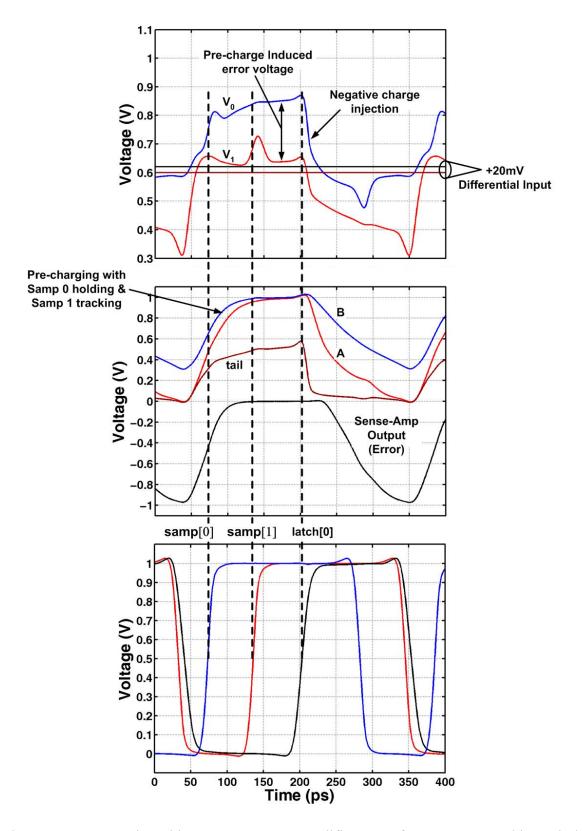

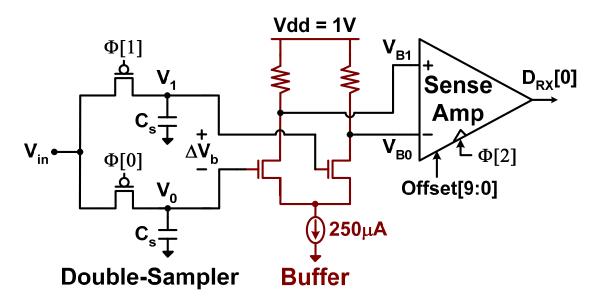

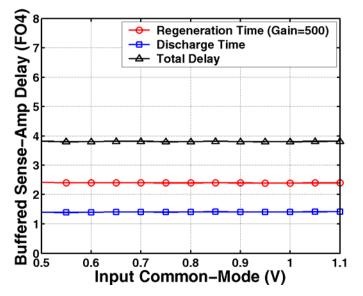

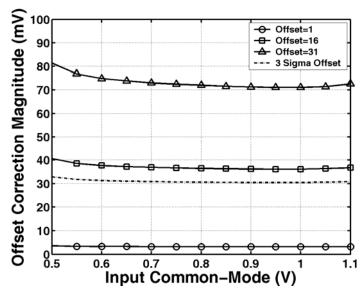

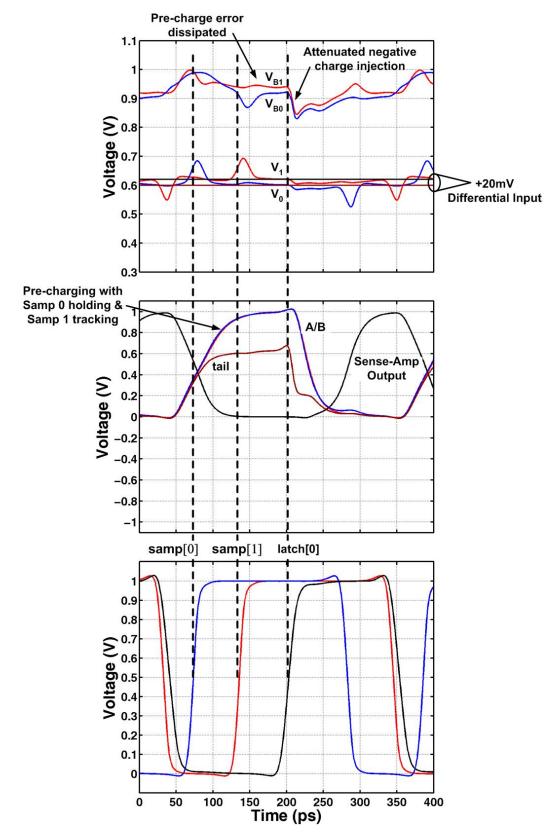

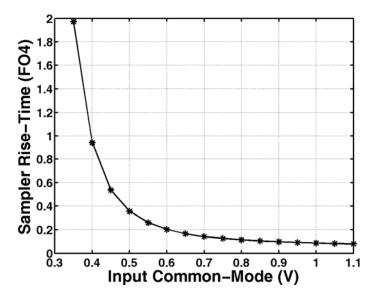

| magnitude versus input common-mode voltage level79Figure 4.7: Sense-amplifier delay versus input common-mode voltage level with the<br>maximum offset correction capacitance value80Figure 4.8: Modified SR-latch [108]82Figure 4.9: Sense-amplifier kickback charge82Figure 4.10: Receiver bit segment sense-amplifier waveforms at 2FO4 bit period<br>operation showing the negative effects of kickback charge83Figure 4.11: Modified receiver bit segment with differential buffer84Figure 4.12: Buffered sense-amplifier delay versus buffer input common-mode<br>voltage level with the maximum offset correction capacitance value84 |

| <ul> <li>magnitude versus input common-mode voltage level</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| magnitude versus input common-mode voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

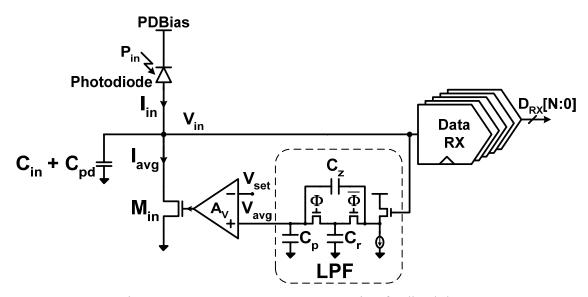

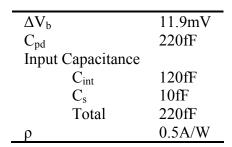

| Figure 4.16:      | Average current generation feedback loop                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------|

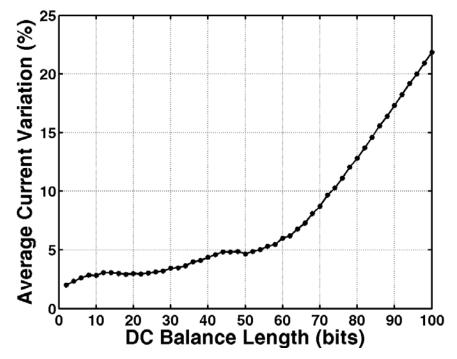

| Figure 4.17:      | Average current variation versus received data DC balance length90                                           |

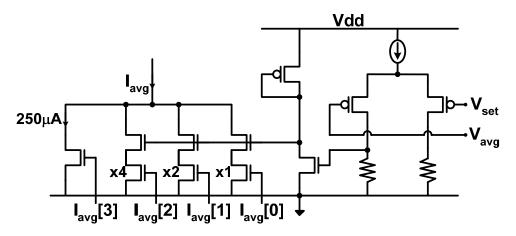

| Figure 4.18:      | Average current generation feedback amplifier and segmented output                                           |

| current           | source                                                                                                       |

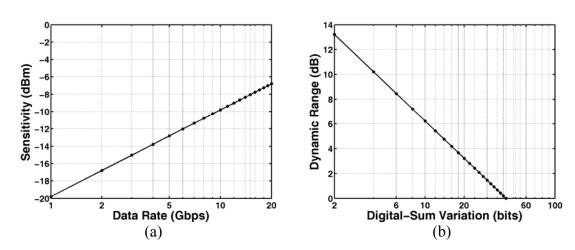

| Figure 4.19:      | Theoretical integrating receiver performance: (a) sensitivity versus data                                    |

| rate, (b)         | dynamic range versus DSV95                                                                                   |

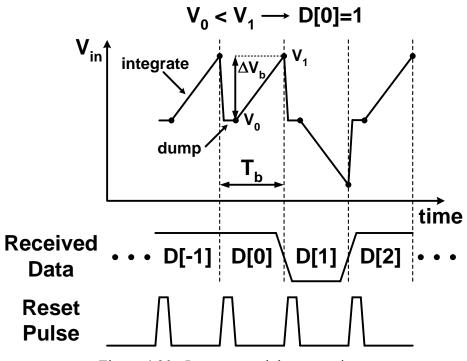

| Figure 4.20:      | Integrate and dump receiver                                                                                  |

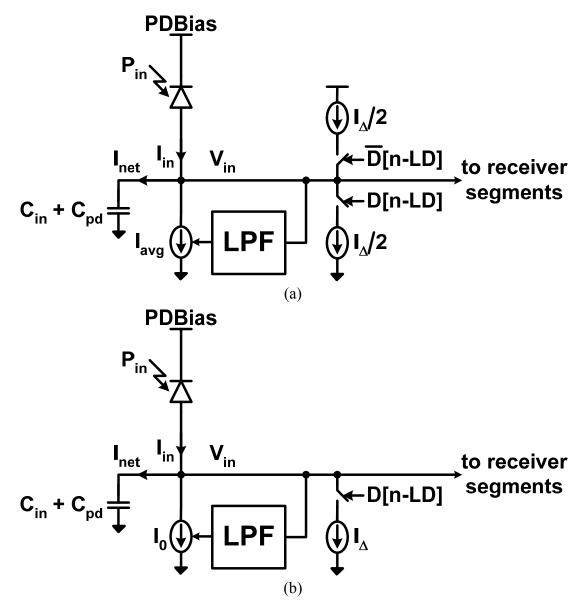

| Figure 4.21:      | Input node of modified integrating receiver with added switched current                                      |

| sources           | that form the swing control filter: (a) original proposition [110], (b)                                      |

| transfor          | med for practical implementation99                                                                           |

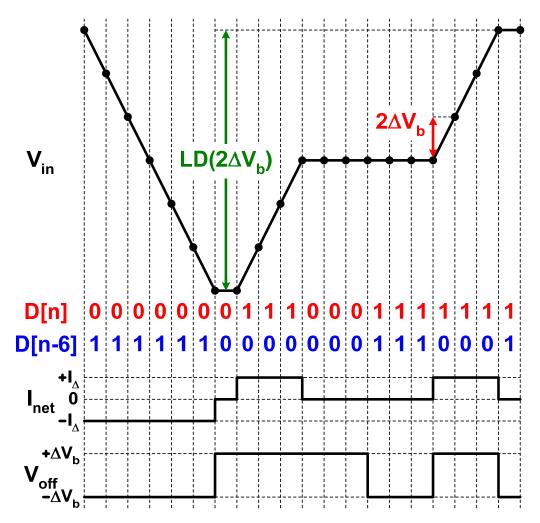

| Figure 4.22:      | Input voltage, net current, and dynamic offset values for the integrating                                    |

| receiver          | with swing control filter (LD=6bits)100                                                                      |

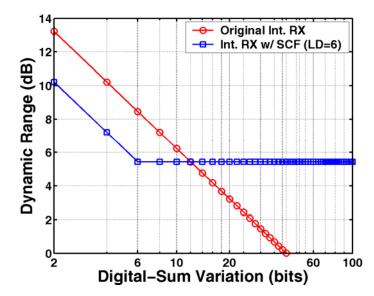

| Figure 4.23:      | Theoretical integrating receiver dynamic range versus DSV with and                                           |

| without           | swing control filter                                                                                         |

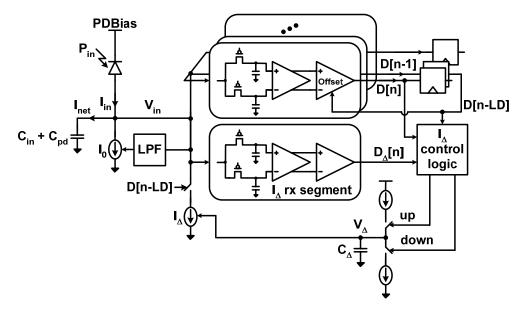

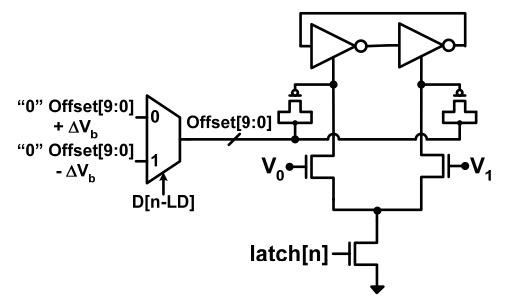

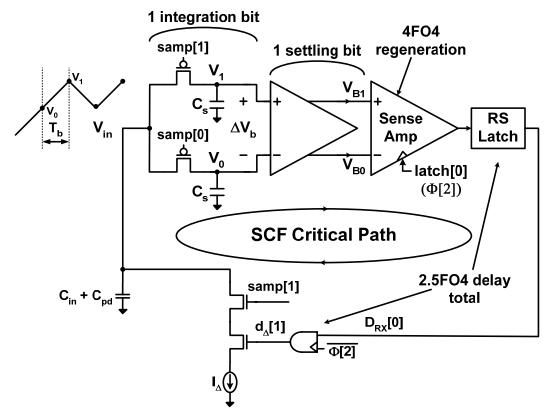

| Figure 4.24:      | Integrating receiver with swing control filter                                                               |

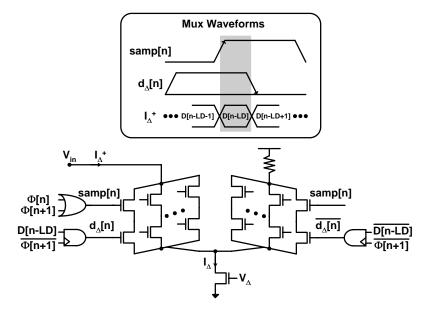

| Figure 4.25:      | Switched $I_{\Delta}$ current source                                                                         |

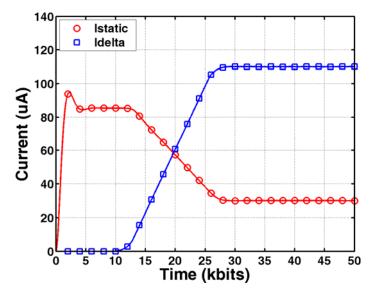

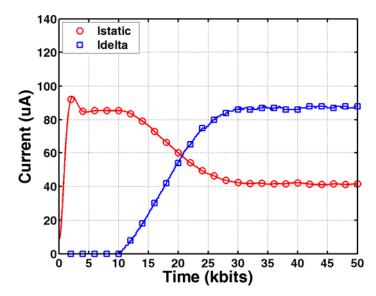

| Figure 4.26:      | $I_0$ and $I_{\Delta}$ control loop locking behavior; $I_0=30\mu A$ , $I_1=140\mu A$ , $I_{\Delta}=110\mu A$ |

|                   |                                                                                                              |

| Figure 4.27:      | Sense-amplifier dynamic offset generation                                                                    |

| Figure 4.28:      | Swing control filter critical path                                                                           |

| Figure 4.29:      | $I_0$ and $I_{\Delta}$ control loop locking behavior with 20% $\Delta V_b$ offset and $\sigma_n=13\%$        |

| $\Delta V_b; I_0$ | =30μA, $I_1$ =140μA, $I_{\Delta}$ =110μA                                                                     |

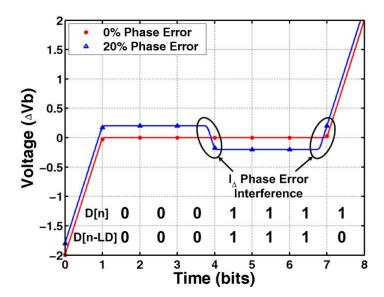

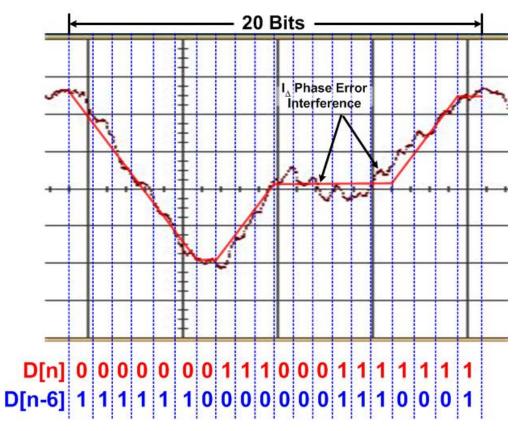

| Figure 4.30:      | $I_{\Delta}$ phase error effect on input voltage waveform                                                    |

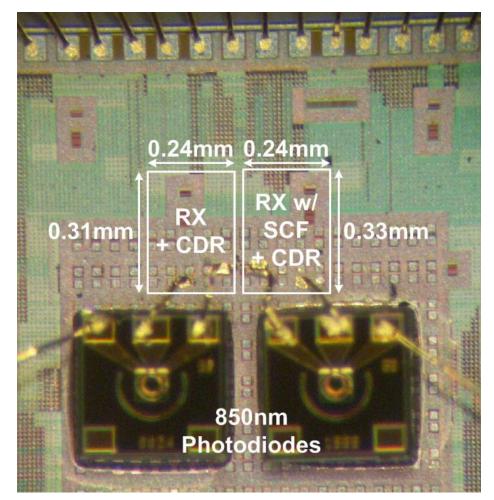

| Figure 4.31:      | 850nm photodiodes wirebonded to optical receivers                                                            |

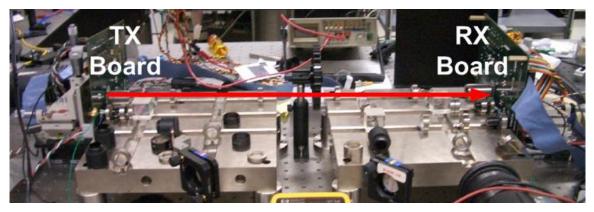

| Figure 4.32:      | Optical link test setup                                                                                      |

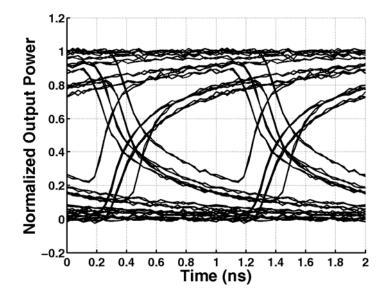

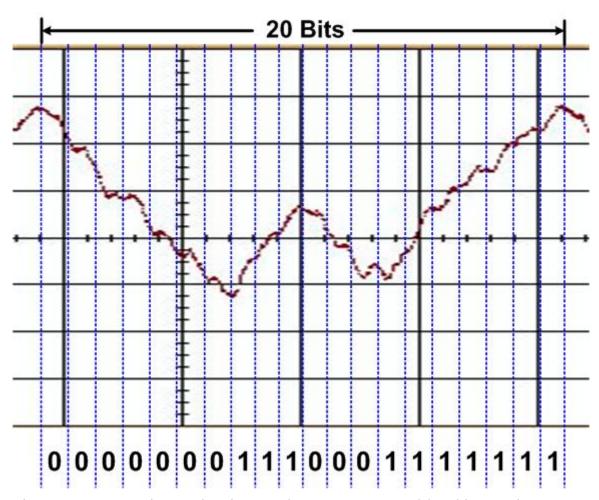

| Figure 4.33:      | Integrating receiver input node response to a 10Gb/s 20bit repeating                                         |

|                   | Note from the on-die measurement, bits 3 and 13 are somewhat distorted                                       |

| due to p          | periodic noise on the subsamplers supply that is believed to not be present                                  |

| -                 | nput waveform                                                                                                |

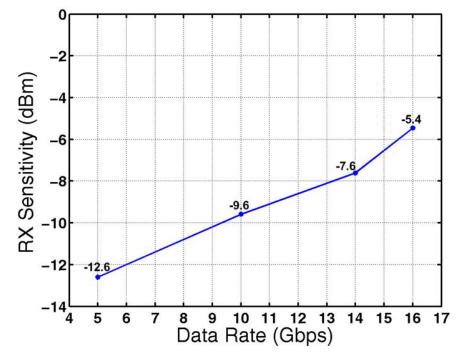

|                   | Measured integrating receiver sensitivity versus data rate                                                   |

| Figure 4.35: Simulated impact of photodiode wirebond connection on the receiver's          |

|--------------------------------------------------------------------------------------------|

| sampled differential input voltage at 16Gb/s: (a) no bondwire, (b) 0.3nH                   |

| bondwire111                                                                                |

| Figure 4.36: Integrating receiver with swing control filter input node response to a       |

| 10Gb/s 20bit repeating pattern. Note the voltage ripples in the ideally flat part of       |

| the input waveform due to a phase error in the $I_{\Delta}$ current source, similar to the |

| simulation results of Figure 4.30                                                          |

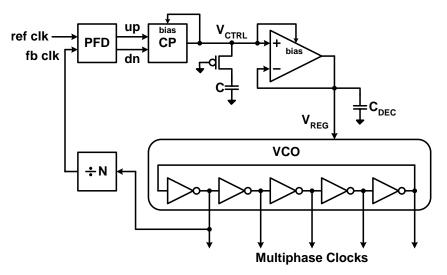

| Figure 5.1: Clock generation PLL                                                           |

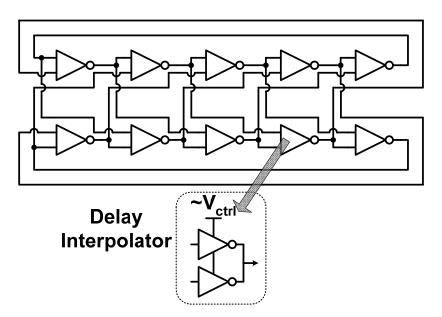

| Figure 5.2: Coupled ring oscillator [29]118                                                |

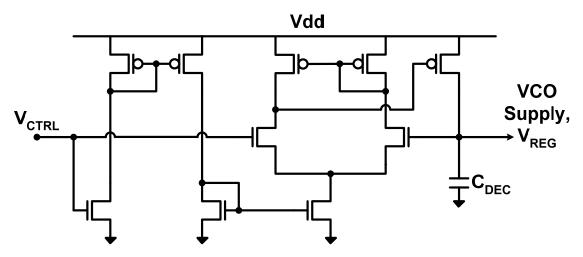

| Figure 5.3: Linear regulator for VCO supply filtering                                      |

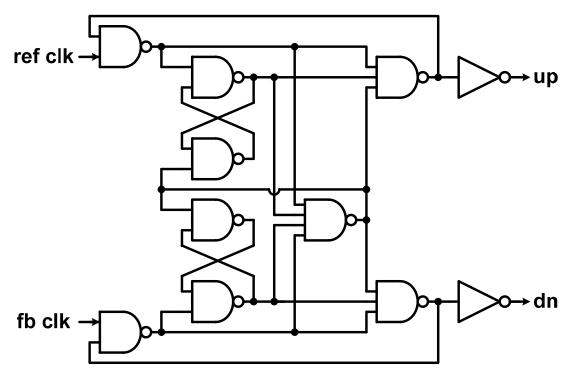

| Figure 5.4: Clock generation PLL phase-frequency detector120                               |

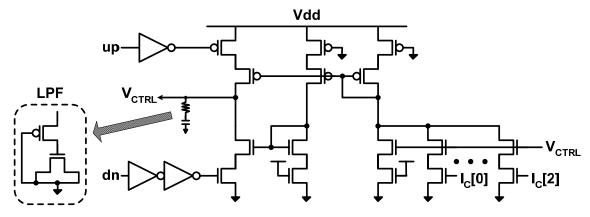

| Figure 5.5: Charge-pump and loop filter                                                    |

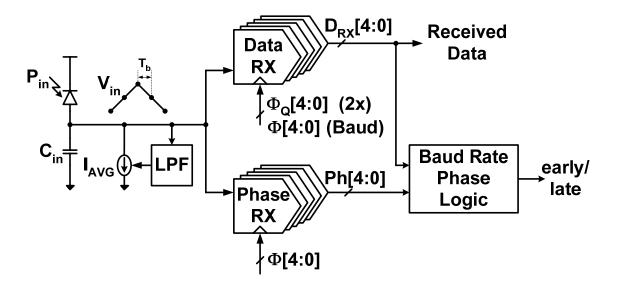

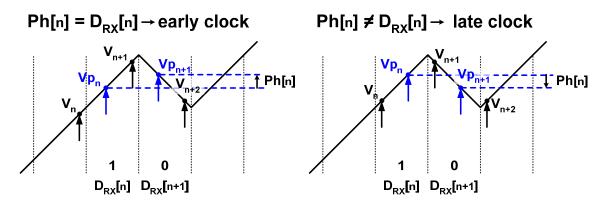

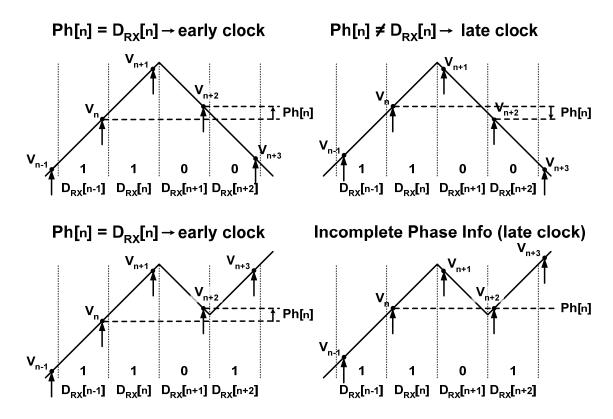

| Figure 5.6: CDR bangbang phase detector                                                    |

| Figure 5.7: Input voltage waveform with 2x-oversampling phase detection [98] 124           |

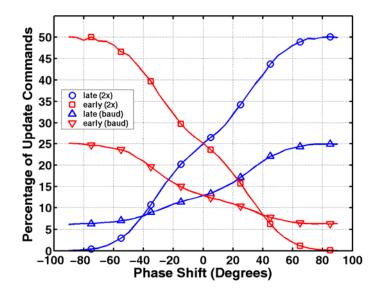

| Figure 5.8: Phase update probability for 2x-oversampling and baud-rate phase               |

| detection124                                                                               |

| Figure 5.9: Input voltage waveform with baud-rate phase detection [98]125                  |

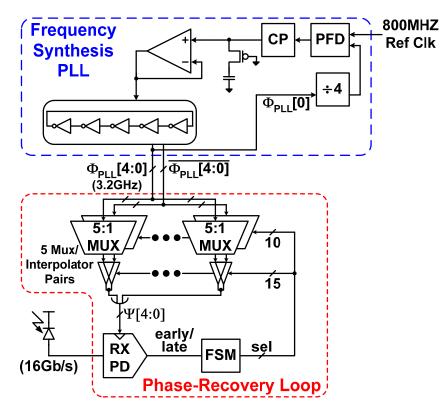

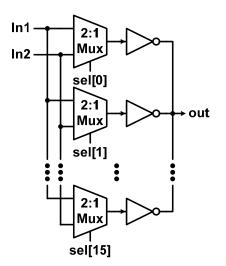

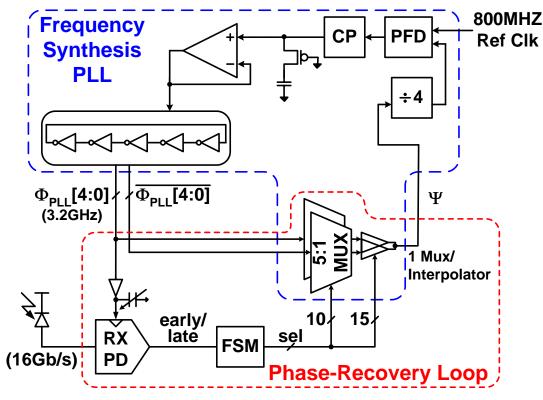

| Figure 5.10: Dual-loop CDR for a 5:1 input demultiplexing receiver                         |

| Figure 5.11: Digital phase interpolator                                                    |

| Figure 5.12: Dual-loop CDR with feedback interpolation [95]129                             |

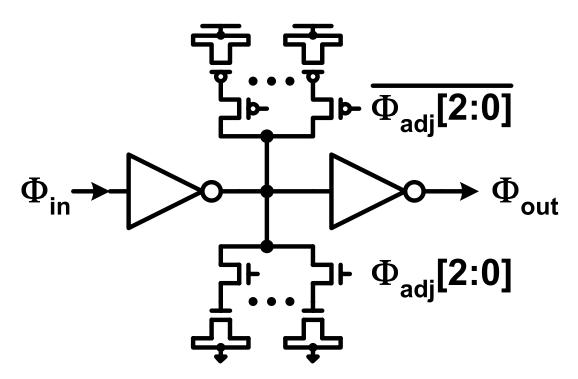

| Figure 5.13: Adjustable delay clock buffer                                                 |

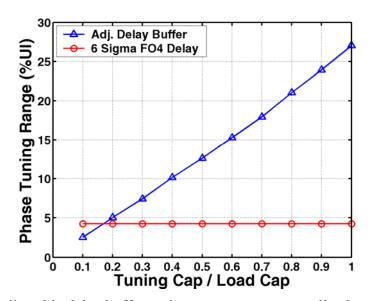

| Figure 5.14: Adjustable delay buffer tuning range versus normalized tuning                 |

| capacitance, 2FO4 UI                                                                       |

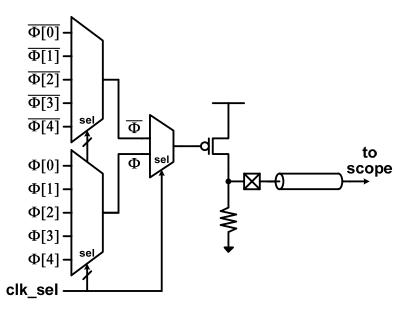

| Figure 5.15: Clock phase muxes for off-chip measurements                                   |

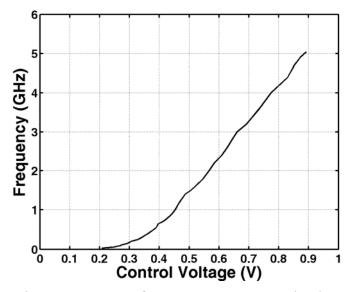

| Figure 5.16: VCO frequency versus control voltage                                          |

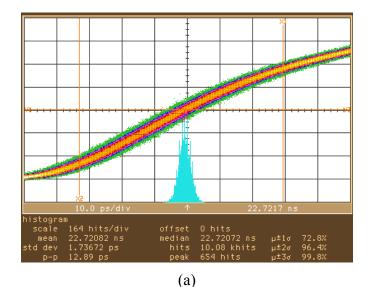

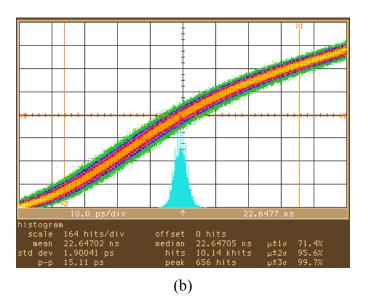

| Figure 5.17: Clock jitter performance: (a) frequency synthesis PLL, (b) CDR                |

| recovered clock                                                                            |

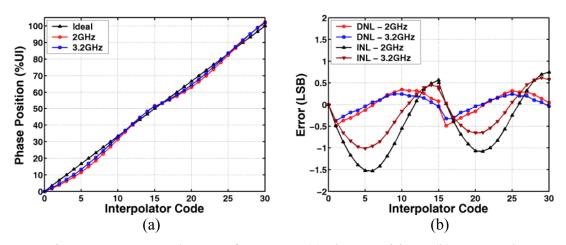

| Figure 5.18: Interpolator performance: (a) phase positions, (b) DNL and INL 134            |

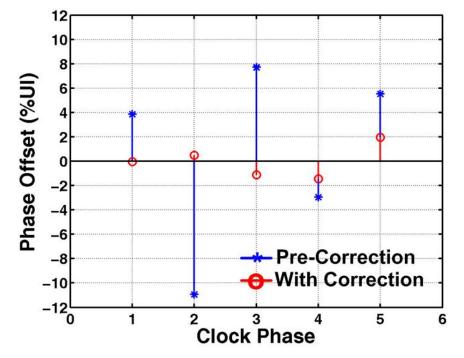

| Figure 5.19: Receiver clock phase tuning performance                                       |

| Figure 6.1: Optical link power consumption versus data rate. VCSEL link po   | ower is   |

|------------------------------------------------------------------------------|-----------|

| experimentally measured, while MQWM power is projected assuming 1            | 00fF      |

| modulators and a source laser with 6dB wall-plug efficiency                  | 140       |

| Figure 6.2: Optical link power breakdown at 16Gb/s: (a) VCSEL link, (b) M    | ÍQWM      |

| link (projected)                                                             | 140       |

| Figure 6.3: Optical versus electrical transceiver performance comparisons: ( | a) energy |

| efficiency, (b) circuit area                                                 | 141       |

# Chapter 1

# Introduction

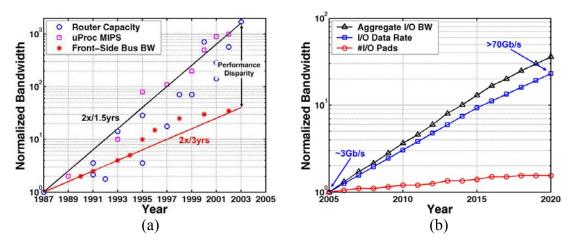

Integrated circuit scaling has enabled a huge growth in processing power which necessitates a corresponding increase in inter-chip communication bandwidth [1]. However, as shown in Figure 1.1(a), I/O bandwidth scaling has lagged behind the processor performance gains [2-4].

The two conventional methods for closing this performance gap include increasing both the per-pin data rate and the I/O number, as projected in [5] (Figure 1.1(b)). While high-performance I/O circuitry can leverage the technology improvements that enable increased core performance, unfortunately the bandwidth of the electrical channels used for inter-chip communication has not scaled in the same manner. Thus, rather than being technology limited, current high-speed I/O link designs are becoming channel limited. In order to continue scaling data rates, link designers implement sophisticated equalization circuitry to compensate for the frequency dependent loss of the bandlimited channels [6-8]. With this additional complexity comes both power and area costs, which will ultimately limit the I/O number.

Figure 1.1: I/O scaling necessity: (a) performance disparity between networking/on-chip processing and off-chip bandwidth [2-4], (b) I/O scaling projections [5]

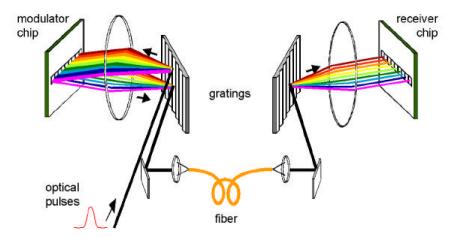

A promising solution to this I/O bandwidth problem is the use of optical inter-chip communication links. The negligible frequency dependent loss of optical channels provides the potential for optical link designs to fully leverage increased data rates provided through CMOS technology scaling without the necessity of additional equalization complexity. Optics also allows very high information density in both free-space systems [9-11], with the ability to focus short wavelength optical beams into small areas without the crosstalk issues of electrical links, and in fiber-based systems, with the added dimension of wavelength division multiplexing (WDM) (Figure 1.2) [12] where multiple parallel links are multiplexed on one fiber by using different wavelength (color) light for each link.

Figure 1.2: Wavelength division multiplexing chip-to-chip optical interconnect [12]

This dissertation focuses on a dense low-power CMOS link architecture which uses optical signaling in order to enable efficient scaling of inter-chip communication bandwidth. A power-efficient high-speed optical link is achieved by employing novel optical transmitter and receiver circuits and through leveraging an electrical link technique of time-division multiplexing. The optical transmitter circuits address current optical device issues of speed, reliability, and CMOS drive compatibility, while the optical receiver design focuses on achieving adequate sensitivity at high power efficiency. Robust operation of the time-division multiplexing architecture is enabled with advanced clocking techniques which generate high-precision clocks, perform receiver timing recovery, and compensate for phase errors induced by process mismatches.

### **1.1 Organization**

In order to comprehend why an I/O architecture modification as radical as optical signaling is under consideration, an understanding of current high-speed electrical link technology and the growing complexity required to signal over bandlimited electrical channels is necessary. Thus, Chapter 2 presents the basic principles of high-speed electrical and optical link design. While many of the high-speed circuit blocks are similar in electrical and optical links, the primary advantage optical links provide is a channel with negligible frequency dependent loss. Therefore, optical links trade-off the potential for reduced signaling complexity with the added cost of the optical channel and the electrical transduction circuitry.

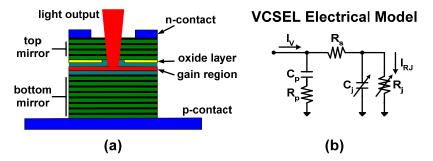

The remainder of the thesis focuses on the implementation of the low-power highspeed optical link architecture in a 90nm CMOS process, with experimental results presented that show operation up to 16Gb/s. Chapter 3 focuses on power-efficient transmitter circuits that address key issues with driving optical sources at high data rates in a CMOS technology. Transmitter designs are presented for two high-density optical sources, vertical-cavity surface-emitting lasers (VCSEL) and multiple-quantum-well modulators (MQWM). Chapter 4 discusses improvements made to an integrating and double-sampling optical receiver architecture [13] in order to enable low-voltage operation suitable for modern and future CMOS technologies. One of the issues with this receiver is its inability to handle uncoded data due to input voltage saturation. To address this, a swing control filter which actively clamps the input signal within the receiver input range is investigated.

Chapter 5 describes the circuitry which produces low-noise clocks with the highprecision phase spacing required by the time-division multiplexing architecture. An adaptive bandwidth frequency synthesis phase-locked loop (PLL) provides clock generation with optimal loop dynamics over a wide frequency range. Timing recovery is performed with a dual-loop architecture which employs baud-rate phase detection and feedback interpolation to achieve reduced power consumption. High-precision phase spacing is ensured at both the transmitter and receiver through adjustable delay clock buffers applied independently on a per-phase basis that compensates for circuit and interconnect mismatches.

Finally, Chapter 6 concludes the thesis with a performance summary of the VCSEL and MQWM links and comparisons against state-of-the-art electrical high-speed links.

# Chapter 2

# Background

This chapter describes the basic principles of high-speed electrical and optical link design. It begins with an overview of the electrical circuits required to achieve high-speed communication over band-limited electrical channels, and then discusses optical channel advantages and optical source and detector properties. It ends with a brief review of the electrical circuit techniques commonly applied to interface with these optical devices.

## 2.1 High-Speed Electrical Links

High-speed point-to-point electrical links are commonly used in short distance chip-to chip communication applications such as internet routers [6,7], multi-processor systems [14], and processor-memory interfaces [15-17]. In order to achieve high data rates, these systems employ specialized I/O circuitry that performs incident wave signaling over carefully designed controlled-impedance channels. As will be described later in this section, the electrical channel's frequency-dependent loss and impedance discontinuities become major limiters in data rate scaling. While traditionally simple binary non-return-to-zero (NRZ) pulse-amplitude-modulation (PAM-2) techniques have been used [18],

today's multi-Gb/s links require link designers to implement channel equalization [6-8] and consider more advanced modulation schemes [19,20].

This section begins by describing the three major link circuit components, the transmitter, receiver, and timing system. Next, it discusses the electrical channel properties that impact the transmitted signal. The section concludes by providing an overview of common equalization schemes and advanced modulation techniques that designers implement in order to extend data rates over the band-limited electrical channels.

#### **2.1.1 Electrical Link Circuits**

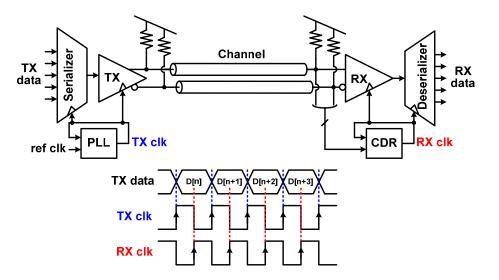

Figure 2.1 shows the major components of a typical high-speed electrical link system. Due to the limited number of high-speed I/O pins in chip packages and printed circuit board (PCB) wiring constraints, a high-bandwidth transmitter serializes parallel input data for transmission. Differential low-swing signaling is commonly used for common-mode noise rejection [21]. At the receiver, the incoming signal is sampled, regenerated to CMOS values, and deserialized. High-frequency clocks synchronize the data transfer and are generated by a frequency synthesis phase-locked loop (PLL) at the transmitter and recovered from the incoming data stream by a clock-and-data recovery (CDR) unit at the receiver.

Figure 2.1: High-speed electrical link system

#### Transmitter

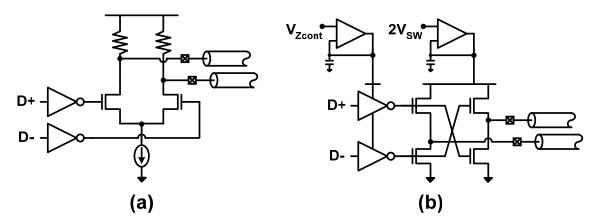

The transmitter must generate an accurate voltage swing on the channel while also maintaining proper output impedance in order to attenuate any channel-induced reflections. Either current or voltage-mode drivers, shown in Figure 2.2, are suitable output stages. Current-mode drivers typically steer current close to 20mA between the differential channel lines in order to launch a bipolar voltage swing on the order of  $\pm$ 500mV. Driver output impedance is maintained through termination which is in parallel with the high-impedance current switch. While current-mode drivers are most commonly implemented [22], the power associated with the required output voltage for proper transistor output impedance and the "wasted" current in the parallel termination led designers to consider voltage-mode drivers. These drivers use a regulated output stage to supply a fixed output swing on the channel through a series termination which is feedback controlled [23]. While the feedback impedance control is not as simple as parallel termination, the voltage-mode drivers have the potential to supply an equal receiver voltage swing at a quarter [24] of the common 20mA cost of current-mode drivers.

Figure 2.2: Transmitter output stages: (a) current-mode driver, (b) voltage-mode driver

#### Receiver

Figure 2.3 shows a high-speed receiver which compares the incoming data to a threshold and amplifies the signal to a CMOS value. This highlights a major advantage of binary differential signaling, where this threshold is inherent, whereas single-ended signaling requires careful threshold generation to account for variations in signal amplitude, loss, and noise [25]. The bulk of the signal amplification is often performed with a positive feedback latch [26,27]. These latches are more power-efficient versus cascaded linear amplification stages since they don't dissipate DC current. While regenerative latches are the most power-efficient input amplifiers, link designers have used a small number of linear pre-amplification stages to implement equalization filters that offset channel loss faced by high data rate signals [15,28].

Figure 2.3: Receiver input stage with regenerative latch [26]

One issue with these latches is that they require time to reset or "pre-charge", and thus to achieve high data rates, often multiple latches are placed in parallel at the input and activated with multiple clock phases spaced a bit period apart in a time-division-demultiplexing manner [18,29], shown in Figure 2.4. This technique is also applicable at the transmitter, where the maximum serialized data rate is set by the clocks switching the multiplexer. The use of multiple clock phases offset in time by a bit period can overcome the intrinsic gate-speed which limits the maximum clock rate that can be efficiently distributed to 6-8 FO4 delays [30].

Figure 2.4: Time-division multiplexing link

#### Timing Circuits

High-precision low-noise clocks are necessary at both the transmitter and receiver in order to ensure sufficient timing margins at high data rates. Figure 2.5 show a PLL, which is often used at the transmitter for clock synthesis in order to serialize reduced-rate parallel input data and also potentially at the receiver for clock recovery. The PLL is a negative feedback loop which works to lock the phase of the feedback clock to an input reference clock. A phase-frequency detector produces an error signal which is proportional to the phase difference between the feedback and reference clocks. This phase error is then filtered to provide a control signal to a voltage-controlled oscillator (VCO) which generates the output clock. The PLL performs frequency synthesis by placing a clock divider in the feedback path, which forces the loop to lock with the output clock frequency equal to the input reference frequency times the loop division factor.

Figure 2.5: PLL frequency synthesizer

It is important that the PLL produce clocks with low timing noise, quantified in the timing domain as jitter and in the frequency domain as phase noise. Considering this, the most critical PLL component is the VCO, as its phase noise performance can dominate at the output clock and have a large influence on the overall loop design. LC oscillators typically have the best phase noise performance, but their area is large and tuning range is limited [31]. While ring oscillators display inferior phase noise characteristics, they offer advantages in reduced area, wide frequency range, and ability to easily generate multiple phase clocks for time-division multiplexing applications [18,29].

Also important is the PLL's ability to maintain proper operation over process variances, operating voltage, temperature, and frequency range. To address this, selfbiasing techniques were developed by Maneatis [32] and expanded in [33,34] that set constant loop stability and noise filtering parameters over these variances in operating conditions.

At the receiver, clock recovery is required in order to position the data sampling clocks with maximum timing margin and also filter the incoming signal jitter. It is possible to modify a PLL to perform clock recovery with changes in the phase detection circuitry, as shown in Figure 2.6. Here the phase detector samples the incoming data stream to extract both data and phase information. As shown in Figure 2.7, the phase detector can either be linear [35], which provides both sign and magnitude information of the phase error, or binary [36], which provides only phase error sign information. While CDR systems with linear phase detectors are easier to analyze, generally they are harder to implement at high data rates due to the difficulty of generating narrow error pulse widths, resulting in effective dead-zones in the phase detector [37]. Binary, or "bangbang", phase detectors minimize this problem by providing equal delay for both data and phase information and only resolving the sign of the phase error [38]. In order to properly filter the input data jitter to prevent transfer onto the receiver clocks, the CDR bandwidth must be set sufficiently low, such that it has a hard time reducing the intrinsic phase noise of a ring VCO. Thus, while a PLL-based CDR is an efficient solution, generally one cannot optimally filter both VCO phase noise and input data jitter. This

motivates the use of dual-loop clock recovery [25], which provides two degrees of freedom to filter the two dominant clock noise sources.

Figure 2.6: PLL-based CDR system

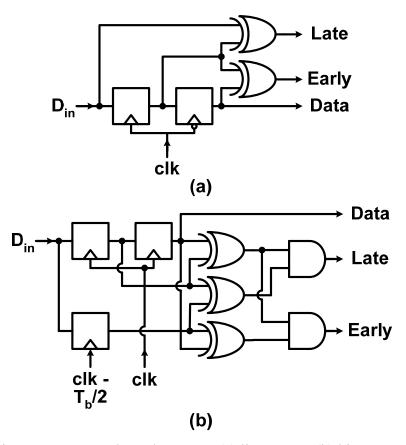

Figure 2.7: CDR phase detectors: (a) linear [35], (b) binary [36]

While proper design of these high-speed I/O components requires considerable attention, CMOS scaling allows the basic circuit blocks to achieve data rates that exceed 10Gb/s [15,16]. However, as data rates scale into the low Gb/s, the frequency dependent loss of the chip-to-chip electrical wires disperses the transmitted signal to the extent that it is undetectable at the receiver without proper signal processing or channel equalization techniques. Thus, in order to design systems that achieve increased data rates, link designers must comprehend the high-frequency characteristics of the electrical channel, which are outlined next.

#### **2.1.2 Electrical Channels**

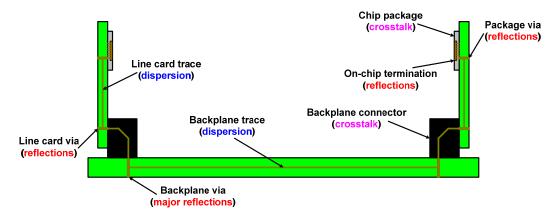

Electrical inter-chip communication bandwidth is predominantly limited by highfrequency loss of electrical traces, reflections caused from impedance discontinuities, and adjacent signal crosstalk, as shown in Figure 2.8. The relative magnitudes of these channel characteristics depend on the length and quality of the electrical channel which is a function of the application. Common applications range from processor-to-memory interconnection, which typically have short (<10") top-level microstrip traces with relatively uniform loss slopes [15], to server/router and multi-processor systems, which employ either long ( $\sim$ 30") multi-layer backplanes [6] or ( $\sim$ 10m) cables [39] which can both possess large impedance discontinuities and loss.

#### Dispersion

PCB traces suffer from high-frequency attenuation caused by wire skin effect and dielectric loss. As a signal propagates down a transmission line, the normalized amplitude at a distance x is equal to

$$\frac{V(x)}{V(0)} = e^{-(\alpha_R + \alpha_D)x}, \qquad (2.1)$$

where  $\alpha_R$  and  $\alpha_D$  represent resistive and dielectric loss factors [21]. The skin effect, which describes the process of high-frequency signal current crowding near the conductor surface, impacts the resistive loss term as frequency increases. This results in a resistive loss term which is proportional to the square-root of frequency

Figure 2.8: Backplane system cross-section

$$\alpha_{R} = \frac{R_{AC}}{2Z_{0}} = \frac{2.61 \times 10^{-7} \sqrt{\rho_{r}}}{\pi D 2Z_{0}} \sqrt{f} , \qquad (2.2)$$

where *D* is the trace's diameter (in),  $\rho_r$  is the relative resistivity compared to copper, and  $Z_0$  is the trace's characteristic impedance [40]. Dielectric loss describes the process where energy is absorbed from the signal trace and transferred into heat due to the rotation of the board's dielectric atoms in an alternating electric field [40]. This results in the dielectric loss term increasing proportional to the signal frequency

$$\alpha_D = \frac{\pi \sqrt{\varepsilon_r} \tan \delta_D}{c} f , \qquad (2.3)$$

where  $\varepsilon_r$  is the relative permittivity, *c* is the speed of light, and  $\tan \delta_D$  is the board material's loss tangent [21].

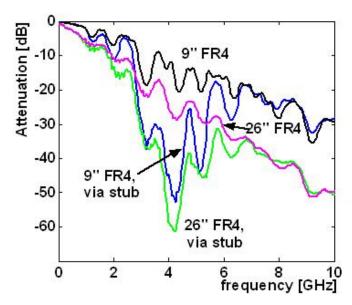

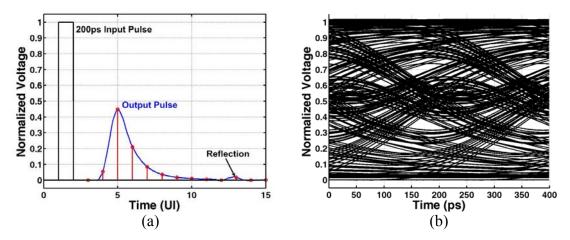

Figure 2.9 shows how these frequency dependent loss terms result in low-pass channels where the attenuation increases with distance [41]. The high-frequency content of a pulses sent across such channel is filtered, resulting in an attenuated received pulse whose energy has been spread or dispersed over several bit periods, as shown in Figure 2.10(a). When transmitting data across the channel, energy from individual bits will now interfere with adjacent bits and make them more difficult to detect. This intersymbol interference (ISI) increases with channel loss and can completely close the received data eye diagram, as shown in Figure 2.10(b).

Figure 2.9: Frequency response of several backplane channels [41]

Figure 2.10: Backplane channel performance at 5Gb/s: (a) pulse response, (b) eye diagram

### Reflections

Signal interference also results from reflections caused by impedance discontinuities. If a signal propagating across a transmission line experiences a change in impedance  $Z_r$  relative to the line's characteristic impedance  $Z_0$ , a percentage of that signal equal to

$$\frac{V_r}{V_i} = \frac{Z_r - Z_0}{Z_r + Z_0}$$

(2.4)

will reflect back to the transmitter. This results in an attenuated or, in the case of multiple reflections, a time delayed version of the signal arriving at the receiver. The most common sources of impedance discontinuities are from on-chip termination mismatches and via stubs that result with signaling over multiple PCB layers. Figure 2.9 shows that the capacitive discontinuity formed by the thick backplane via stubs can cause severe nulls in the channel frequency response.

#### Crosstalk

Another form of interference comes from crosstalk, which occurs due to both capacitive and inductive coupling between neighboring signal lines. As a signal propagates across the channel, it experiences the most crosstalk in the backplane connectors and chip packages where the signal spacing is smallest compared to the distance to a shield. Crosstalk is classified as near-end (NEXT), where energy from an aggressor (transmitter) couples and is reflected back to the victim (receiver) on the same chip, and far-end (FEXT), where the aggressor energy couples and propagates along the channel to a victim on another chip. NEXT is commonly the most detrimental crosstalk, as energy from a strong transmitter ( $\sim 1V_{pp}$ ) can couple onto a received signal at the same chip which has been attenuated ( $\sim 20mV_{pp}$ ) from propagating on the lossy channel. Crosstalk is potentially a major limiter to high-speed electrical link scaling, as in common backplane channels the crosstalk energy can actually exceed the through channel signal energy at frequencies near 4GHz [6].

#### 2.1.3 Channel Equalization and Advanced Modulation Techniques

The previous subsection discussed interference mechanisms that can severely limit the rate at which data is transmitted across electrical channels. As shown in Figure 2.9(b), frequency dependent channel loss can reach magnitudes sufficient to make simple NRZ binary signaling undetectable. Thus, in order to continue scaling electrical link data rates, designers have implemented systems which compensate for frequency dependent loss or equalize the channel response. This subsection discusses how the equalization circuitry is often implemented in high-speed links, and other approaches for dealing with these issues.

#### Equalization Systems

In order to extend a given channel's maximum data rate, many communication systems use equalization techniques to cancel intersymbol interference caused by channel distortion. Equalizers are implemented either as linear filters (both discrete and continuous-time) that attempt to flatten the channel frequency response, or as non-linear filters that directly cancel ISI based on the received data sequence. Depending on system data rate requirements relative to channel bandwidth and the severity of potential noise sources, different combinations of transmit and/or receive equalization are employed.

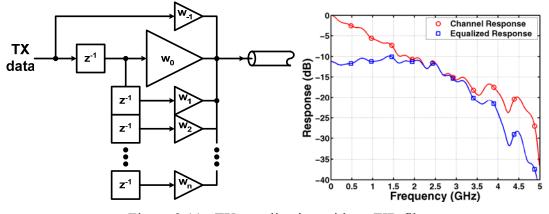

Transmit equalization, implemented with an FIR filter, is the most common technique used in high-speed links [42]. This TX "pre-emphasis" (or more accurately "de-emphasis") filter, shown in Figure 2.11, attempts to invert the channel distortion that a data bit experiences by pre-distorting or shaping the pulse over several bit times. While this filtering could also be implemented at the receiver, the main advantage of implementing the equalization at the transmitter is that it is generally easier to build high-speed digital-to-analog converters (DACs) versus receive-side analog-to-digital converters. However, because the transmitter is limited in the amount of peak-power that it can send across the channel due to driver voltage headroom constraints, the net result is that the low-frequency signal content has been attenuated down to the high-frequency level, as shown in Figure 2.11.

Figure 2.11: TX equalization with an FIR filter

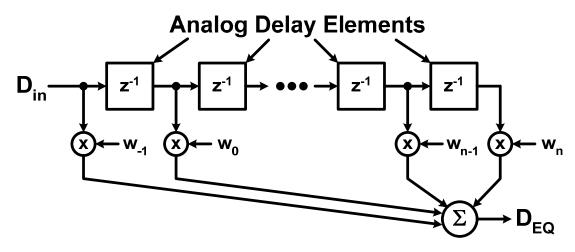

Figure 2.12 shows a block diagram of receiver-side FIR equalization. A common problem faced by linear receive side equalization is that high-frequency noise content and

crosstalk are amplified along with the incoming signal. Also challenging is the implementation of the analog delay elements, which are often implemented through timeinterleaved sample-and-hold stages [43] or through pure analog delay stages with large area passives [44,45]. Nonetheless, one of the major advantage of receive side equalization is that the filter tap coefficients can be adaptively tuned to the specific channel [43], which is not possible with transmit-side equalization unless a "back-channel" is implemented [46].

Figure 2.12: RX equalization with an FIR filter

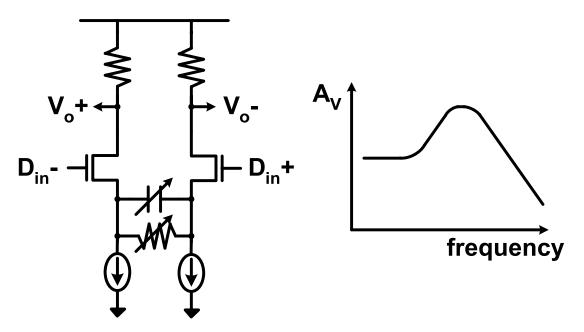

Linear receiver equalization can also be implemented with a continuous-time amplifier, as shown in Figure 2.13. Here, programmable RC-degeneration in the differential amplifier creates a high-pass filter transfer function which compensates the low-pass channel. While this implementation is a simple and low-area solution, one issue is that the amplifier has to supply gain at frequencies close to the full signal data rate. This gain-bandwidth requirement potentially limits the maximum data rate, particularly in time-division demultiplexing receivers.

Figure 2.13: Continuous-time equalizing amplifier

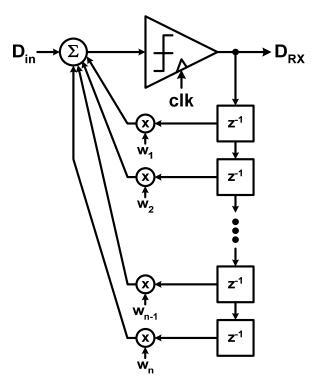

The final equalization topology commonly implemented in high-speed links is a receiver-side decision feedback equalizer (DFE). A DFE, shown in Figure 2.14, attempts to directly subtract ISI from the incoming signal by feeding back the resolved data to control the polarity of the equalization taps. Unlike linear receive equalization, a DFE doesn't directly amplify the input signal noise or cross-talk since it uses the quantized input values. However, there is the potential for error propagation in a DFE if the noise is large enough for a quantized output to be wrong. Also, due to the feedback equalization structure, the DFE cannot cancel pre-cursor ISI. The major challenge in DFE implementation is closing timing on the first tap feedback since this must be done in one bit period or unit interval (UI). Direct feedback implementations [6] require this critical timing path to be highly optimized. While a loop-unrolling architecture eliminates the need for first tap feedback [47], if a multiple tap implementation is required the critical path simply shifts to the second tap which has a timing constraint also near 1UI [8].

Figure 2.14: RX equalization with a DFE

### Advanced Modulation Techniques

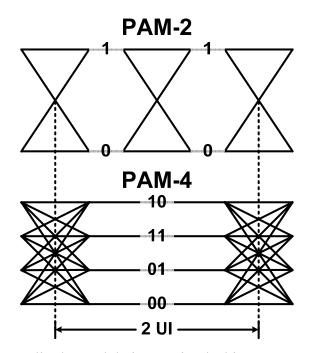

Modulation techniques which provide spectral efficiencies higher than simple binary signaling have also been implemented by link designers in order to increase data rates over band-limited channels. Multi-level PAM, most commonly PAM-4, is a popular modulation scheme which has been implemented both in academia [48] and industry [49,50]. Shown in Figure 2.15, PAM-4 modulation consists of two bits per symbol, which allows transmission of an equivalent amount of data in half the channel bandwidth. However, due to the transmitter's peak-power limit, the voltage margin between symbols is 3x (9.5dB) lower with PAM-4 versus simple binary PAM-2 signaling. Thus, a general rule of thumb exists that if the channel loss at the PAM-2 Nyquist frequency is greater than 10dB relative to the previous octave, then PAM-4 can potentially offer a higher signal-to-noise ratio (SNR) at the receiver. However, this rule can be somewhat optimistic due to the differing ISI and jitter distribution present with PAM-4 signaling [51]. Also, PAM-2 signaling with a non-linear DFE at the receiver further bridges the performance gap due to the DFE's ability to cancel the dominant first post-cursor ISI without the inherent signal attenuation associated with transmitter equalization [7].

Figure 2.15: Pulse amplitude modulation – simple binary PAM-2 (1bit/symbol) and PAM-4 (2bits/symbol)

Another more radical modulation format under consideration by link researchers is the use of multi-tone signaling. While this type of signaling is commonly used in systems such as DSL modems [52], it is relatively new for high-speed inter-chip communication applications. In contrast with conventional baseband signaling, multitone signaling breaks the channel bandwidth into multiple frequency bands over which data is transmitted. This technique has the potential to greatly reduce equalization complexity relative to baseband signaling due to the reduction in per-band loss and the ability to selectively avoid severe channel nulls. Typically, in systems such as modems where the data rate is significantly lower than the on-chip processing frequencies, the required frequency conversion in done in the digital domain and requires DAC transmit and ADC receive front-ends [53,54]. While it is possible to implement high-speed transmit DACs [55], the excessive digital processing and ADC speed and precision required for multi-Gb/s channel bands results in prohibitive receiver power and complexity. Thus, for power-efficient multi-tone receivers, researchers have proposed using analog mixing techniques combined with integration filters and multiple-inputmultiple-output (MIMO) DFEs to cancel out band-to-band interference [20].

Serious challenges exist in achieving increased inter-chip communication bandwidth over electrical channels while still satisfying I/O power and density constraints. As discussed, current equalization and advanced modulation techniques allow data rates near 10Gb/s over severely band-limited channels. However, this additional circuitry comes with a power and complexity cost, with typical commercial high-speed serial I/O links consuming close to 20mW/Gb/s [56,39] and research-grade links consuming near 10mW/Gb/s [15,17]. The demand for higher data rates will only result in increased equalization requirements and further degrade link energy efficiencies. While there has been recent work on reducing link power [23,28,57], these implementations have focused on moderate data rates over relatively tame channels. This approach will require extremely dense I/O architectures over optimized electrical channels that will ultimately be limited by the chip bump/pad pitch and crosstalk constraints. These issues motive investigation into the use of optical links for chip-to-chip applications, discussed in the next section.

# 2.2 High-Speed Optical Links

The primary motivation for an I/O architecture modification as radical as optical signaling is the magnitude of potential bandwidth offered with an optical channel. Conventional optical data transmission is analogous to wireless AM radio, where data is transmitted by modulating the optical intensity or amplitude of the high-frequency optical carrier signal. In order to achieve high fidelity over the most common optical channel – the glass fiber, high-speed optical communication systems typically use infrared light from source lasers with wavelengths ranging from 850-1550nm, or equivalently frequencies ranging from 200-350THz. Thus, the potential data bandwidth is quite large since this high optical carrier frequency exceeds current data rates by over three orders of magnitude. Moreover, because the loss of typical optical channels at short distances varies only fractions of dBs over wide wavelength ranges (tens of nanometers) [58], there is the potential for data transmission of several Tb/s without the requirement of channel equalization. This simplifies design of optical links in a manner similar to non-channel limited electrical links. However, optical links do require additional circuits that

interface to the optical sources and detectors. Thus, in order to achieve the potential link performance advantages, emphasis is placed on using efficient optical devices and low-power and area interface circuits.

This section gives an overview of the key optical link components, beginning with the optical channel attributes. A discussion of properties and modulation techniques of optical source devices suited for low-power high-density I/O applications follows. The section concludes with a presentation of high-speed optical detector characteristics and conventional receiver front-ends.

### **2.2.1 Optical Channels**

The two optical channels relevant for short distance chip-to-chip communication applications are free-space (air or glass) and optical fibers. These optical channels offer potential performance advantages over electrical channels in terms of loss, cross-talk, and both physical interconnect and information density [59].

Free-space optical links have been used in applications ranging from long distance line-of-sight communication between buildings in metro-area networks [60] to short distance inter-chip communication systems [9,61,62]. Typical free-space optical links use lenses to collimate light from a laser source. Once collimated, laser beams can propagate over relatively long distances due to narrow divergence angles and low atmospheric absorption of infrared radiation. The ability to focus short wavelength optical beams into small areas avoids many of the crosstalk issues faced in electrical links and provides the potential for very high information density in free-space optical interconnect systems with small 2D transmit and receive arrays [9-11]. However, free-space optical links are sensitive to alignment tolerances and environmental vibrations. To address this, researchers have proposed rigid systems with flip-chip bond chips onto plastic or glass substrates with 45° mirrors [61] or diffractive optical elements [62] that perform optical routing with very high precision.

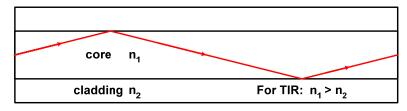

Optical fiber-based systems, while potentially less dense than free-space systems, provide alignment and routing flexibility for chip-to-chip interconnect applications. An

optical fiber, shown in Figure 2.16, confines light between a higher index core and a lower index cladding via total internal reflection. In order for light to propagate along the optical fiber, the interference pattern, or mode, generated from reflecting off the fiber's boundaries must satisfy resonance conditions. Thus, fibers are classified based on their ability to support multiple or single modes.

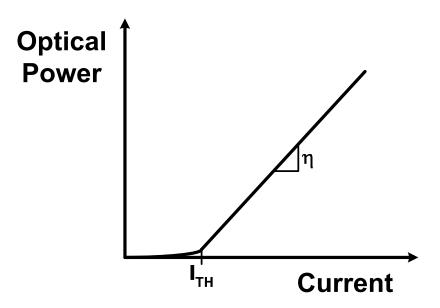

Figure 2.16: Optical fiber cross-section

Multi-mode fibers with large core diameters (typically 50 or 62.5µm) allow several propagating modes, and thus are relatively easy to couple light into. These fibers are used in short and medium distance applications such as parallel computing systems and campus-scale interconnection. Often relatively inexpensive vertical-cavity surface-emitting lasers (VCSEL) operating at wavelengths near 850nm are used as the optical sources for these systems. While fiber loss (~3dB/km for 850nm light) can be significant for some low-speed applications, the major performance limitation of multi-mode fibers is modal dispersion caused by the different light modes propagating at different velocities. Due to modal dispersion, multi-mode fiber is typically specified by a bandwidth-distance product, with legacy fiber supporting 200MHz-km and current optimized fiber supporting 2GHz-km [63].

Single-mode fibers with smaller core diameters (typically 8-10µm) only allow one propagating mode (with two orthogonal polarizations), and thus require careful alignment in order to avoid coupling loss. These fibers are optimized for long distance applications such as links between internet routers spaced up to and exceeding 100km. Fiber loss typically dominates the link budgets of these systems, and thus they often use source lasers with wavelengths near 1550nm which match the loss minima (~0.2dB/km) of conventional single-mode fiber. While modal dispersion is absent from single-mode fibers, chromatic (CD) and polarization-mode dispersion (PMD) exists. However, these

dispersion components are generally negligible for distances less than 10km, and are not issues for short distance inter-chip communication applications.