# Lecture 3: MC68000 instruction set

- Assembler directives (the most important ones)

- ORG, EQU, END, DC, DS, EXTERN/PUBLIC

- Instructions (the most important ones)

- Data movement

- Integer arithmetic

- Boolean

- Shift and rotate

- Bit manipulation

- Binary Coded Decimal

- Program flow

- System control

# Assembler directives

#### Assembler directives

- **are** instructions to the assembler program

- and they appear in the mnemonic (opcode) field of the source code

- are not instructions to the microprocessor

- and they have no direct effect on the contents of memory (except DC)

### They cover a number of functions, including

- defining symbols and assigning them values

- controlling the flow of execution of the assembler

- setting format and content of the object and listing files

# Assembler directives (the most important ones)

| DIRECTIVE | OPERATION                 |         | S      | ΥΝΤΑΧ                        |

|-----------|---------------------------|---------|--------|------------------------------|

| ORG       | set program origin        |         | ORG    | value                        |

| EQU       | equate value to symbol    | symbol  | EQU    | value                        |

| END       | end of source program     |         | END    | label                        |

| DC        | define data constant      | [label] | DC     | <pre>number[,number][]</pre> |

| DS        | define RAM storage        | [label] | DS     | count                        |

| RSEG      | begin relocatable segment |         | RSEG   | name                         |

| EXTERN    | define external symbol    |         | EXTERN | <pre>symbol[,symbol][]</pre> |

| PUBLIC    | define public symbol      |         | PUBLIC | <pre>symbol[,symbol][]</pre> |

# The ORG directive

#### FUNCTION (ORIGIN)

• Sets the starting address in memory for the instructions or data constants that follow

### EXAMPLE

| 00001000 |               | 1 | ORG    | \$1000   |

|----------|---------------|---|--------|----------|

| 00001000 | 203C 00000012 | 2 | MOVE.L | #\$12,d0 |

- Hex address \$1000 is set as the starting address for the following instruction

- The opcode for MOVE.L goes in address \$1000

- The second word for MOVE.L goes in address \$1002 ... and so on

# The EQU directive

#### FUNCTION (EQUATE)

- Assigns a value to a symbol. The symbol is used later in the program in place of the value

- EXAMPLE

| 00001000 |               | 1       | ORG    | \$1000       |

|----------|---------------|---------|--------|--------------|

| 00000100 |               | 2 count | EQU    | <b>\$100</b> |

| 00002000 |               | 3<br>4  | ORG    | \$2000       |

| 00002000 | 203C 00000100 | 5       | MOVE.L | #count,d0    |

| 00002006 |               | 6       | END    | \$2000       |

- The value of \$100 replaces the symbol in the binary code

- The use of EQU directives is encouraged because

- makes program more readable

- makes programs easier to maintain

# The END directive

### FUNCTION

- Used at the end of the source program

- Statements following the END directive are not processed by the assembler

### EXAMPLE

| 00001000 |               | 1 | ORG    | \$1000            |

|----------|---------------|---|--------|-------------------|

| 00001000 | 203C 00000012 | 2 | MOVE.L | #\$12 <b>,</b> d0 |

| 00001006 |               | 3 | END    | \$1000            |

- The label of the END directive (optional) represents the entry point for the program

- The address of the entry point is used by debuggers, loaders, conversion utilities, and so on, to identify the starting address of the program

# The DC directive

### FUNCTION (DEFINE CONSTANT)

• Places data constants WITHIN A PROGRAM

### EXAMPLE

| 000000D  |              | 1 cr   | EQU  | \$0D     |

|----------|--------------|--------|------|----------|

| 00001000 |              | 2      | ORG  | \$1000   |

| 00001000 | 0005FFFF     | 3 num  | DC   | 5,-1     |

| 00001004 | 05FF         | 4 more | DC.B | 5,-1     |

| 00001006 | 777269676874 | 5 name | DC.B | 'wright' |

| 0000100C | 0D00         | 6 var  | DC.B | cr,0     |

| 0000100E |              | 7      | END  | \$1000   |

- For words and longwords, the assembler adjusts the address of the constant to ensure proper alignment.

- ASCII characters defined as words are left-justified within the word

# The DS directive

### FUNCTION (DEFINE STORAGE)

- Reserves RAM storage for use during execution of the program.

- EXAMPLE

| 00000004 |    | 1 length | EQU  | 4      |

|----------|----|----------|------|--------|

| 00001000 |    | 2        | ORG  | \$1000 |

| 00001000 |    | 3 buffer | DS.B | length |

| 00001004 | FF | 4 temp   | DC.B | \$FF   |

| 00001005 |    | 5        | END  |        |

### NOTES

• The memory locations reserved for **buffer** are not initialized, they **will** contain garbage data

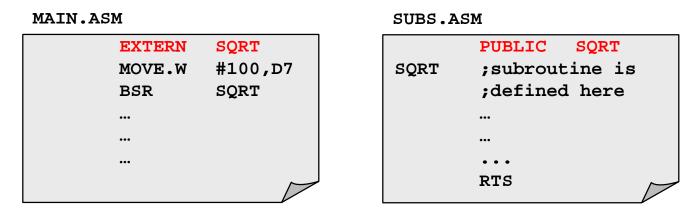

# The EXTERN/PUBLIC directives

### FUNCTION

• Used when a program is split over multiple files (modules)

### EXAMPLE

### NOTES

• MAIN.ASM contains the code of a main program, whereas SUBS.ASM contains the subroutines, which will typically be shared among several main programs.

# Instruction categories

#### Data movement

- Move operands (data) among memory locations or registers

- Integer arithmetic

- Addition, subtraction, multiply, divide, ...

- Boolean

- AND, OR, XOR, NOT, ...

- Shift and rotate

- Arithmetic-shift, logical-shift, rotate

- Bit manipulation

- Bit test, bit set, bit clear, ...

- Binary Coded Decimal

- Add, subtract and negate in BCD notation

- Program flow

- Branch, jump and return

- System control

- Miscellaneous: trap, reset, SR/CCR manipulation, ...

| INSTR. | DESCRIPTION                                                                                                                                                                                     | EXAMP                                                 | LE                                                  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| MOVE   | Copies an 8-, 16- or 32-bit value from<br>one memory location or register to<br>another memory location or register                                                                             | MOVE.B #\$8C,D0<br>MOVE.W #\$8C,D0<br>MOVE.L #\$8C,D0 | [D0]←\$XXXXX8C<br>[D0]←\$XXXX008C<br>[D0]←\$000008C |

| MOVEA  | Copies a source operand to an<br>address register. MOVEA operates<br>only on words or longwords.<br>MOVEA.W sign-extends the 16-bit<br>operand to 32 bits.                                      | MOVEA.W #\$8C00,A0<br>MOVEA.L #\$8C00,A0              | [A0]←\$FFFF8C00<br>[A0]←\$00008C00                  |

| MOVEQ  | Copies a 8-bit signed value in the<br>range –128 to +127 to one of the eight<br>data registers. The data to be moved<br>is sign-extended before it is copied to<br>its destination              | MOVEQ #-3,D0<br>MOVEQ #4,D0                           | [D0]←\$FFFFFFD<br>[D0]←\$0000004                    |

| MOVEM  | Transfers the contents of a <b>group</b> of<br>registers specified by a list. The list of<br>registers is defined as $A_i - A_j / D_p - D_q$ .<br>MOVEM operates only on words or<br>longwords. | MOVEM.L A0-A3/D0-D7,-(A7)                             | ;copies all working<br>;registers to stack          |

| INSTR. | DESCRIPTION                                                                                                                    | EXA             | MPLE             |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|--|

|        | ADD×/SUB× add/subtract the contents of a source to/from the contents of a destination and deposits the result in the           | ADD.W D0,D1     | ;[D1]←\$11118123 |  |

| ADD×   | destination location. Direct memory-to-memory operations are                                                                   | ADD.L D0,D1     | ;[D1]←\$22228123 |  |

| SUB×   | not permitted. Assume [D0]=\$11118000 and                                                                                      | ADDQ #N,D1      | ;N∈[1,8]         |  |

|        | [D1]=\$11110123.                                                                                                               | SUB.L D1,D0     | ;[D0]←\$00007EDD |  |

|        | MULU (multiply unsigned) forms the product of two 16-bit                                                                       |                 |                  |  |

| MULU   | integers. The 32-bit destination must be a data register. MULS                                                                 | MULU #\$0800,D0 | ;[D0]←\$00400000 |  |

| MULS   | is similar but treats data as signed. Assume                                                                                   |                 | ,[20]( ,00100000 |  |

|        | [D0]=\$ABCD8000.                                                                                                               |                 |                  |  |

|        | DIVU (divide unsigned) works with a 32-bit dividend and a 16-<br>bit divisor. The dividend must be a data register. The 16-bit |                 |                  |  |

| DIVU   | result is stored in the low word of the destination, and the 16-                                                               | DIVS #-3,D0     | ;[D0]←\$0002FFFC |  |

| DIVS   | bit remainder in the high word. DIVS is similar but treats data                                                                |                 |                  |  |

|        | as signed. Assume [D0]=\$0000000E, 14 <sub>10</sub> .                                                                          |                 |                  |  |

| _      | CRL (clear) writes zeros into the destination operand. NEG                                                                     | CLR.B D0        | ;[D0]←\$1234B000 |  |

| CLR    | (negate) performs a 2s complement operation on the                                                                             | CLR.L D0        | ;[D0]←\$00000000 |  |

| NEG    | destination datasubtracts it from zero. Assume<br>[D0]=\$1234B021.                                                             | NEG.W D0        | ;[D0]←\$12344FDF |  |

|        | Sign-extend increases the bit-size of a signed integer. <b>EXT.W</b>                                                           |                 |                  |  |

| EXT    | converts an 8-bit into a 16-bit, and <b>EXT.L</b> converts a 16-bit                                                            | EXT.W DO        | ;[D0]←\$12340021 |  |

|        | into a 32-bit. Assume [D0]=\$1234B021.                                                                                         | EXT.L DO        | ;[D0]←\$FFFFB021 |  |

| INSTR.      | DESCRIPTION                                                                                                                   |                     | EXAMPLE                                                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------|

| AND<br>ANDI | Bit-wise logical AND operation.<br>Normally used to <b>clear</b> , or <b>mask</b> ,<br>certain bits in a destination operand. | ANDI.B #%0111111,D0 | ;clear the 8 <sup>th</sup> least<br>;significant bit of D0 |

| OR<br>ORI   | Bit-wise logical OR operation.<br>Normally used to <b>set</b> certain bits in a<br>destination operand.                       | ORI.B #%10101010,D0 | ;set even bits of D0<br>;lowest byte                       |

| EOR<br>EORI | Bit-wise logical XOR operation.                                                                                               | EOR.B #%11111111,D0 | ;XOR of the lowest byte of D0                              |

| NOT         | Bit-wise NOT operation. Assume [D0]=\$1234F0F0.                                                                               | NOT.W D0            | ;[D0]←\$12340F0F                                           |

| TST         | Similar to CMP #0, operand                                                                                                    | TST DO              | ;update N,Z and clear V,C                                  |

# Shift and rotate

| INSTR. | OPERATION                 | BIT MOVEMENT           |

|--------|---------------------------|------------------------|

| ASL    | Arithmetic<br>shift left  | C ← Operand ← 0<br>X ← |

| ASR    | Arithmetic<br>shift right | Operand → C<br>▲ ↓ X   |

| LSL    | Logic shift<br>left       | C ← Operand ← 0<br>X ← |

| LSR    | Logic shift<br>right      | 0 → Operand → C<br>→ X |

| ROL    | Rotate left               | C Operand              |

| ROR    | Rotate right              | → Operand → C          |

| SWAP   | Swap words of a longword  | 16 bits 16 bits        |

| INSTR. | DESCRIPTION                                                                                                                                               | EXAMPLE (Assume [D0]=\$0000009)                                   |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| BSET   | Bit test and set Causes the Z-bit to<br>be set if the specified bit is zero and<br>then forces the specified bit of the<br>operand to be set to one       | BSET #2, D0 ; [D0] $\leftarrow$ \$000000D and [Z] $\leftarrow$ 1  |  |

| BCLR   | Bit test and clear works like BSET<br>except that the specified bit is<br>cleared (forced to zero) after it has<br>been tested                            | BCLR #0, D0 ; [D0] $\leftarrow$ \$0000008 and [Z] $\leftarrow$ 0  |  |

| BCHG   | Bit test and change causes the<br>value of the specified bit to be<br>reflected in the Z-bit and then toggles<br>(inverts) the state of the specified bit | BCHG #4, D0 ; [D0] $\leftarrow$ \$00000019 and [Z] $\leftarrow$ 1 |  |

| BTST   | Bit test reflects the value of the specified bit in the Z-bit                                                                                             | BTST #2, D0 ;[Z]←1                                                |  |

| INSTR. | DESCRIPTION                                                                                                                                                                                            | EXAMPLE (Assu | ume[X]=0, [D0]=48, [D1]=21)            |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------|

| ABCD   | Adds the source operand and the X-bit to the destination operand using BCD arithmetic. This is a BYTE operation only; the X-bit is used to provide a mechanism for multi-byte BCD operations.          | ABCD D0,D1    | ;[D1]←0000069                          |

| SBCD   | Subtract the source operand and the X-bit from the destination operand using BCD arithmetic. This is a BYTE operation only, so the X-bit is used to provide a mechanism for multi-byte BCD operations. | SBCD D1,D0    | ;[D0]←0000027                          |

| NBCD   | Subtract the destination operand and the X-bit from zero.                                                                                                                                              | NBCD D1       | ;[D1]←00000052<br>;[X]←1, [V]←1, [C]←1 |

| INSTR.     | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BRA        | BRA (branch always) implements an<br>unconditional branch, relative to the PC. The<br>offset is expressed as an 8- or 16-bit signed<br>integer. If the destination is outside of a 16-bit<br>signed integer, BRA <b>cannot</b> be used.                                                                                      |  |

| Bcc        | Bcc (branch conditional) is used whenever<br>program execution must follow one of two<br>paths depending on a condition. The condition<br>is specified by the mnemonic cc. The offset is<br>expressed as an 8- or 16-bit signed integer. If<br>the destination is outside of a 16-bit signed<br>integer, Bcc cannot be used. |  |

| BSR<br>RTS | BSR branches to a subroutine. The PC is<br>saved on the stack before loading the PC with<br>the new value. RTS is use to return from the<br>subroutine by restoring the PC from the stack.                                                                                                                                   |  |

| JMP        | JMP (jump) is similar to BRA. The only<br>difference is that BRA uses only relative<br>addressing, whereas JMP has more<br>addressing modes, including absolute address<br>(see reference manual).                                                                                                                           |  |

| сс | CONDITION                | BRANCH<br>TAKEN IF                                          |

|----|--------------------------|-------------------------------------------------------------|

| CC | Carry clear              | C=0                                                         |

| CS | Carry set                | C=1                                                         |

| NE | Not equal                | Z=0                                                         |

| EQ | Equal                    | Z=1                                                         |

| PL | Plus                     | N=0                                                         |

| MI | Minus                    | N=1                                                         |

| HI | Higher than              | $\overline{C}\overline{Z} = 1$                              |

| LS | Lower than or same as    | C+Z=1                                                       |

| GT | Greater than             | $NV\overline{Z} + \overline{N}\overline{V}\overline{Z} = 1$ |

| LT | Less than                | $N\overline{V} + \overline{N}V = 1$                         |

| GE | Greater than or equal to | $N\overline{V} + \overline{N}V = 0$                         |

| LE | Less than or equal to    | $Z + (N\overline{V} + \overline{N}V) = 1$                   |

| VC | Overflow clear           | V=0                                                         |

| VS | Overflow set             | V=1                                                         |

| Т  | Always true              | Always                                                      |

| F  | Always false             | Never                                                       |

| INSTR.                      | DESCRIPTION                                                                                                                                                                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVE<br>ANDI<br>ORI<br>EORI | Unique variations of MOVE, AND, OR and EOR that allow altering the bits in the status and condition code registers.                                                                                         |

| TRAP                        | TRAP performs three operations: (1) pushes the PC and SR to the stack, (2) sets the execution mode to supervisor and (3) loads the PC with a new value read from a vector table                             |

| STOP<br>RESET               | STOP loads the SR with an immediate operand and stops<br>the CPU. RESET asserts the CPU's RESET line for 124<br>cycles. If STOP or RESET are executed in user mode, a<br><i>privilege violation</i> occurs. |