# Lecture 2: MC68000 architecture

- General information

- Programmer's model

- Memory organization

- Instruction format

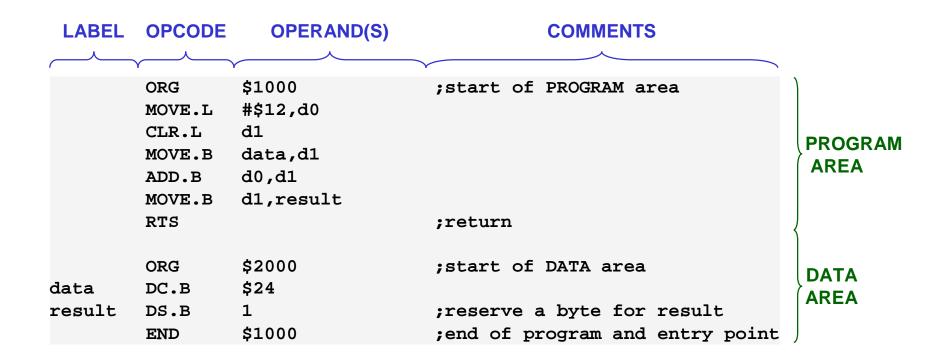

- Our first assembly program

- The sim68k simulator

- Machine translation

# MC68000 general information

|                                                       | $D_4$              | 1        | 0     | 64       | D5                                 |

|-------------------------------------------------------|--------------------|----------|-------|----------|------------------------------------|

| Specifications                                        | D <sub>3</sub>     | 2        |       | 63       | D <sub>6</sub>                     |

| • 22 bit Data and Address Pagistors                   |                    | 4        |       | 62<br>61 | D <sub>7</sub><br>D <sub>8</sub>   |

| <ul> <li>32-bit Data and Address Registers</li> </ul> | $\mathbf{D}_{0}$   | 5        |       | 60       | D <sub>9</sub>                     |

| <ul> <li>16-bit Data Bus</li> </ul>                   | AS                 | 6        |       | 59       | D <sub>10</sub>                    |

|                                                       | UDS<br>LDS         | 7        |       | 58<br>57 | D <sub>11</sub>                    |

| <ul> <li>24-bit Address Bus (16MB)</li> </ul>         | R/W                | 8<br>9   |       | 57<br>56 | D <sub>12</sub><br>D <sub>13</sub> |

| <ul> <li>14 Addressing Modes</li> </ul>               | DTACK              | 10       |       | 55       | <b>D</b> <sub>14</sub>             |

|                                                       | BG                 | 11       |       | 54       | D <sub>15</sub>                    |

| <ul> <li>Memory-Mapped Input/Output</li> </ul>        | BGACK<br>BR        | 12<br>13 |       | 53<br>52 | GND                                |

| - Dragram Countar                                     | V <sub>cc</sub>    | 14       | 68000 | 51       | A <sub>23</sub><br>A <sub>22</sub> |

| <ul> <li>Program Counter</li> </ul>                   | CLK                | 15       | CPU   | 50       | A <sub>21</sub>                    |

| <ul> <li>56 Instructions</li> </ul>                   | GND<br>HALT        | 16       |       | 49       | V <sub>cc</sub>                    |

|                                                       | RESET              | 17<br>18 |       | 48<br>47 | A <sub>20</sub><br>A <sub>19</sub> |

| <ul> <li>5 Main Data Types</li> </ul>                 | VMA                | 19       |       | 46       | A <sub>18</sub>                    |

| <ul> <li>7 interrupt levels</li> </ul>                | E                  | 20       |       | 45       | A <sub>17</sub>                    |

|                                                       | VPA<br>BERR        | 21<br>22 |       | 44<br>43 | A <sub>16</sub><br>A <sub>15</sub> |

| <ul> <li>Clock speeds: 4MHz to 12.5MHz</li> </ul>     | IPL <sub>2</sub>   | 23       |       | 42       | A <sub>15</sub>                    |

| - Synchronous and covinchronous data                  | $\overline{IPL}_1$ | 24       |       | 41       | <b>A</b> <sub>13</sub>             |

| <ul> <li>Synchronous and asynchronous data</li> </ul> |                    | 25       |       | 40       | A <sub>12</sub>                    |

| transfers                                             | $FC_2$<br>$FC_1$   | 26<br>27 |       | 39<br>38 | A <sub>11</sub><br>A <sub>10</sub> |

|                                                       | FC <sub>0</sub>    | 28       |       | 37       | A <sub>9</sub>                     |

|                                                       | A <sub>1</sub>     | 29       |       | 36       | A <sub>8</sub>                     |

|                                                       | $A_2$<br>$A_3$     | 30<br>31 |       | 35<br>34 | $A_7$<br>$A_6$                     |

|                                                       | A3<br>A4           | 32       |       | 33       | A <sub>6</sub>                     |

R

# What is a "microprocessor architecture"?

- For our purposes the architecture is the <u>software or</u> <u>programmer's model</u> of the microprocessor

- The CPU registers available to the programmer

- The basic instructions the CPU can perform

- The ways these instructions can **specify a memory location**

- The way data is organized in memory

- How the CPU accesses & controls **peripheral** devices

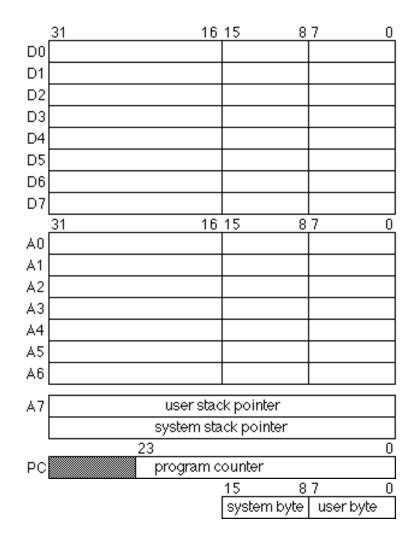

# MC68000 register set

- 8 data registers (D0-D7)

- 8 address registers (A0-A7)

- There are TWO A7 registers

- User Stack Pointer (USP)

- Supervisor Stack Pointer (SSP)

- Program Counter (PC)

- Status Register / Condition Code Register (SR/CCR)

# Status/Condition Code Register

### More significant byte: SR

- Only modifiable in supervisor mode

- Details in later sections

### Least significant byte: CCR

- For user-level programs

- Behavior depends on instruction

| 15 | 13 | 10    | 8  | 4   | 0     |

|----|----|-------|----|-----|-------|

| т  | S  | 12 11 | 10 | X N | z v c |

- T Trace Mode

- S Supervisor State

- I Interrupt Mask

- X Extend

- N Negative

- Z Zero

- Y Overflow

- C Carry

| Bit      | Meaning                            |

|----------|------------------------------------|

| т        | Tracing for run-time               |

| •        | debugging                          |

| S        | Supervisor or                      |

| 3        | User Mode                          |

|          | System responds to interrupts      |

| •        | with a level higher than I         |

| С        | Set if a carry or borrow is        |

|          | generated. Cleared otherwise       |

| v        | Set if a signed overflow           |

| v        | occurs. Cleared otherwise          |

| z        | Set if the result is zero.         |

| 2        | Cleared otherwise                  |

| Ν        | Set if the result is negative.     |

| IN       | Cleared otherwise                  |

| Х        | Retains information from the carry |

| <b>^</b> | bit for multi-precision arithmetic |

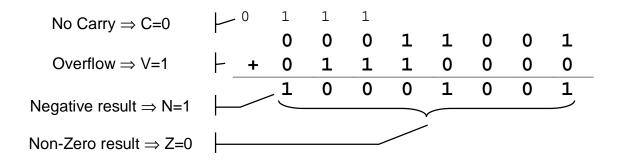

# Condition Code Register example

- Add the numbers \$19 and \$70 and show the effect on the CCR bits

- The following piece of code performs the operation

- MOVE.B #\$70,D0

- ADD.B #\$19,DO

- To illustrate the behavior of the CCR we will perform an addition in base 2

# Data representation (review)

### Three bases will be used thoroughly

- Decimal

- **321**<sub>10</sub> =  $3 \times 10^2$  +  $2 \times 10^1$  +  $1 \times 10^0$

- Hexadecimal

- **•**  $AB6_{16} = 10 \times 16^2 + 11 \times 16^1 + 6 \times 16^0$

- Binary

- **101**  $_2$  = 1×2<sup>2</sup> + 0×2<sup>1</sup> + 1×2<sup>0</sup>

### Express the following numbers in base 10

- 0111<sub>10</sub>

- FF05<sub>16</sub>

- 1000<sub>2</sub>

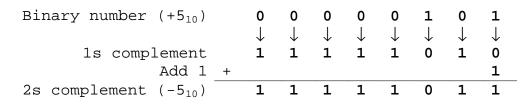

# 2's complement (review)

### How to express negative numbers in binary?

- Sign-Magnitude:

- Use the Most Significant Bit to encode the sign

- 0111<sub>2</sub>=+7<sub>10</sub>

- 1111<sub>2</sub>=-7<sub>10</sub>

- 2s Complement:

- The most commonly used form

- Subtraction is made *very* easy (perform the operation 5-7)

- The range of numbers that can be represented is from -2<sup>n-1</sup> to +2<sup>n-1</sup>-1

# Memory organization

#### 24-bit addresses

- 16MB can be addressed

- 3 data widths

- BYTE: 8-bit, can be at even or odd address

- WORD: 16-bit, must be at x2 address

- LONGWORD:32-bit, must be at x4 address

#### Big-endian order

- Words are stored with the lower 8-bits in the higher of the two storage locations

- As opposed to little-endian processors, like the Intel 80x86 family

|                    | Memory<br>address |           |           | <ul> <li>Since the data bus is 16-bit wide,<br/>it makes sense to visualize<br/>memory in blocks of 16 bits</li> </ul> |

|--------------------|-------------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------|

|                    | \$000000          | Byte0     | Byte1     |                                                                                                                        |

|                    | \$000002          | Byte2     | Byte3     |                                                                                                                        |

|                    | \$000004          | Byte4     | Byte5     |                                                                                                                        |

|                    | \$000000          | Word0 MSB | Word0 LSB |                                                                                                                        |

|                    | \$000002          | Word1 MSB |           |                                                                                                                        |

|                    | \$000004          | Word2 MSB |           |                                                                                                                        |

|                    | \$000006          | Word3 MSB | Word3 LSB |                                                                                                                        |

| MOVE \$3210, 0     | \$000000          | 32        | 10        |                                                                                                                        |

|                    | \$000000          | Longword  | d 0 (MSW) |                                                                                                                        |

|                    | \$000002          |           | d 0 (LSW) |                                                                                                                        |

|                    | \$000004          | Longwore  | 1 1 (MSW) |                                                                                                                        |

|                    | \$000006          | Longwor   | d 1 (LSW) |                                                                                                                        |

|                    | \$000000          | 76        | 54        |                                                                                                                        |

| MOVE \$76543210, 0 | \$000002          | 32        | 10        |                                                                                                                        |

# Register Transfer Language (RTL)

- A notation that describes the micro-processors actions clearly and unambiguously

- We'll use a simplified version

- 100 means "#100"

- [M(4)] means "contents stored in memory location 4"

- [MAR] means "contents stored in MAR"

- [M(4)]=100 means "memory location 4 contains #100"

- [MAR]=100 means "MAR contains #100"

- [PC]←4 means "load number 4 onto PC"

- [M(4)]←100+[M(4)] means "add #100 to contents of memory location 4 and save"

# MC68000 instructions

#### Instruction format is

#### <label> opcode<.field> <operands> <;comments>

- clabel> pointer to the instruction's memory location

- opcode

opcode

opcode

opcode

opcode

- defines width of operands (B,W,L)

- <operands> data used in the operation

- <;comments> for program documentation

#### Examples

|      | Instruction |         | RTL            |

|------|-------------|---------|----------------|

|      | MOVE.W      | #100,D0 | [D0]←100       |

|      | MOVE.W      | 100,D0  | [D0]←[M(100)]  |

|      | ADD.W       | D0,D1   | [D1]←[D1]+[D0] |

|      | MOVE.W      | D1,100  | [M(100)]←[D1]  |

| data | DC.B        | 20      | [data] ←20     |

|      | BRA         | label   | [PC] ←label    |

# Instruction operands

#### Operands can be

- registers

- constants

- memory addresses

### Basic addressing modes (to be expanded)

| <ul> <li>D<sub>n</sub>: data register direct</li> </ul> | MOVE.L D0,       | D1 |

|---------------------------------------------------------|------------------|----|

| <ul> <li>A<sub>n</sub>: register indirect</li> </ul>    | MOVE.L (A0),     | D1 |

| <ul> <li>#n: immediate</li> </ul>                       | MOVE.L #10,      | D1 |

| <ul> <li>n: absolute</li> </ul>                         | MOVE.L \$08FF00, | D1 |

#### Immediate operands can be specified in several formats

- Hexadecimal: prefixed by \$

- Octal: prefixed by @

- Decimal: prefixed by & (or nothing)

- Binary: prefixed by %

- ASCII: within single quotes 'abc'

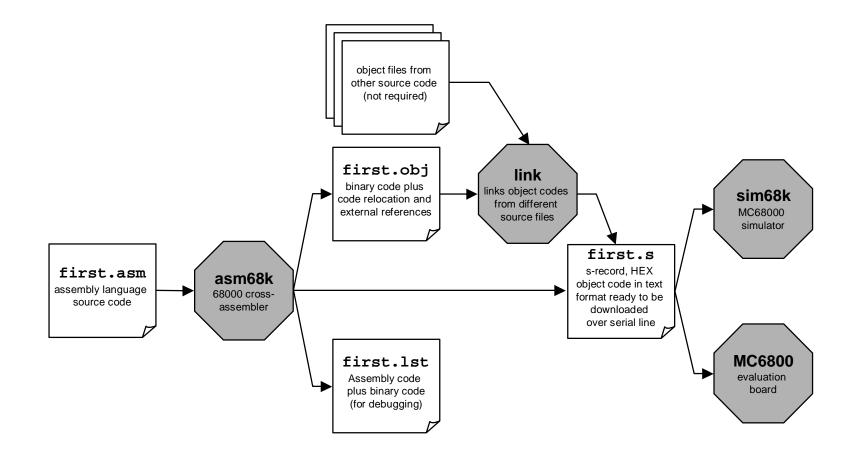

# Compilation and execution steps

### Compilation steps

- Write source in text editor and save (first.asm)

- Create binary with assembler (asm68k first.asm -1)

- I flag creates list file (first.lst) with assembly and binary code

- Link with linker --only if multiple source files

### Execution steps (on simulator)

- Start simulator (sim68k)

- Load program (LO first.s)

- Execute

- Directly (GO 1000) or

- Step by step (T)

# The sim68k simulator

- Available on thor.cs.wright.edu and 339 Russ PCs

- Type sim68k on command line

### Basic simulator commands

| Command                  | Syntax                                                    | Example         |  |

|--------------------------|-----------------------------------------------------------|-----------------|--|

| <b>Display Formatted</b> | DF                                                        | DF              |  |

| Memory Dump              | MD <address> <count> [;DI]</count></address>              | MD 1000 20 ;DI  |  |

| Memory Modify            | MM <address> [;{ ,W,L}]</address>                         | MM 1000         |  |

| Register Modify          | <pre>.<register> [<contents>]</contents></register></pre> | .PC 1000        |  |

| Block Fill               | BF <addr1> <addr2> <data></data></addr2></addr1>          | BF 1000 2000 FF |  |

| Go                       | GO [ <address>]</address>                                 | GO              |  |

| Trace                    | T [ <address>]</address>                                  | Т               |  |

| Set Breakpoint           | BR [ <address>]</address>                                 | BR 1000         |  |

| Clear Breakpoint         | NOBR [ <address>]</address>                               | NOBR            |  |

| Load                     | LO <fname></fname>                                        | LO FIRST.S      |  |

| Store                    | ST <fname> <address> <count></count></address></fname>    | ST FIRST 100 10 |  |

| Exit                     | EX                                                        | EX              |  |

### Run the simulator

| MS                                                                                                                                                                                                                                                                                            | _ 🗆 ×         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| MC68000/ECB Simulator.<br>Copyright (C) Livadas and Ward, 1992. Author Wayne Wolf<br>Version 2.3<br>SIM68000 2.3 > LO FIRST.S<br>SIM68000 2.3 > .PC 1000<br>SIM68000 2.3 ><br>.PC=00001000                                                                                                    |               |

| SIM68000 2.3 > T                                                                                                                                                                                                                                                                              |               |

| PC=00001006 SR=8000=T.0 US=00007000 SS=00007E00<br>D0=00000012 D1=912AAC38 D2=CABABC34 D3=212B3F97<br>D4=A1CC9EEE D5=D946AF5F D6=4C9A63AA D7=52205D24<br>A0=8FC0A05F A1=B688A0B3 A2=57BA89D0 A3=085A3A58<br>A4=C443A903 A5=372B65A7 A6=659D7A2B A7=00007000<br>000001006 4281 CLR.L           | D1            |

| SIM68000 2.3 > T                                                                                                                                                                                                                                                                              |               |

| PC=00001008 SR=8004=T.02 US=00007000 SS=00007E00<br>D0=00000012 D1=00000000 D2=CABABC34 D3=212B3F97<br>D4=A1CC9EEE D5=D946AF5F D6=4C9A63AA D7=52205D24<br>A0=8FC0A05F A1=B688A063 A2=57BA89D0 A3=085A3A58<br>A4=C443A903 A5=372B65A7 A6=659D7A2B A7=00007000<br>00001008 1239 00002000 MOVE.B | \$00002000,D1 |

| SIM68000 2.3 > T                                                                                                                                                                                                                                                                              |               |

| PC=0000100E SR=8000=T.0 US=00007000 SS=00007E00<br>D0=00000012 D1=00000024 D2=CABABC34 D3=212B3F97<br>D4=A1CC9EEE D5=D946AF5F D6=4C9A63AA D7=52205D24<br>A0=8FC0A05F A1=B688A083 A2=57BA89D0 A3=085A3A58<br>A4=C443A903 A5=372B65A7 A6=659D7A2B A7=00007000<br>0000100E D200 ADD.B            |               |

| ФООО́100Е D200 АDD.В                                                                                                                                                                                                                                                                          | D0,D1         |

| SIM68000 2.3 > T                                                                                                                                                                                                                                                                              |               |

| PC=00001010 SR=8000=T.0 US=00007000 SS=00007E00<br>D0=00000012 D1=00000036 D2=CABABC34 D3=212B3F97<br>D4=A1CC9EEE D5=D946AF5F D6=4C9A63AA D7=52205D24<br>A0=8FC0A05F A1=B688A0B3 A2=57BA89D0 A3=085A3A58<br>A4=C443A903 A5=372B65A7 A6=659D7A2B A7=00007000<br>00001010 13C1 00002001 MOVE.B  | D1,\$00002001 |

| SIM68000 2.3 >                                                                                                                                                                                                                                                                                |               |

# How is the program's machine code stored in physical memory?

| MEMORY   | MACHINE       | SOURCE |        | ASSEM  | BLY       |

|----------|---------------|--------|--------|--------|-----------|

| LOCATION | CODE          | LINE   |        | CODE   | =         |

|          |               |        |        |        |           |

| / Y      |               | Ŷ      | Y      |        |           |

| 00001000 |               | 1      |        | ORG    | \$1000    |

| 00001000 | 203C 0000012  | 2      |        | MOVE.L | #\$12,d0  |

| 00001006 | 4281          | 3      |        | CLR.L  | d1        |

| 00001008 | 1239 00002000 | 4      |        | MOVE.B | data,d1   |

| 0000100E | D200          | 5      |        | ADD.B  | d0,d1     |

| 00001010 | 13C1 00002001 | 6      |        | MOVE.B | d1,result |

| 00001016 | 4E75          | 7      |        | RTS    |           |

|          |               | 8      |        |        |           |

| 00002000 |               | 9      |        | ORG    | \$2000    |

| 00002000 | 24            | 10     | data   | DC.B   | \$24      |

| 00002001 |               | 11     | result | DS.B   | 1         |

| 00002002 |               | 12     |        | END    | \$1000    |

|          |               |        |        |        |           |

| \$001000 | 20   | 3C     |

|----------|------|--------|

| \$001002 | 00   | 00     |

| \$001004 | 00   | 12     |

| \$001006 | 42   | 81     |

| \$001008 | 12   | 39     |

| \$00100A | 00   | 00     |

| \$00100C | 20   | 00     |

| \$00100E | D2   | 00     |

| \$001010 | 13   | C1     |

| \$001012 | 00   | 00     |

| \$001014 | 20   | 01     |

| \$001016 | 4E   | 75     |

|          |      |        |

|          | data | result |

| \$002000 | 20   | 00     |

### Machine code translation

| ASSEMBLY CODE   | INSTRUCTION FORMAT    | MACHINE CODE  |

|-----------------|-----------------------|---------------|

| MOVE.L #\$12,d0 | 00 10 000 000 111 100 | 203C 0000012  |

| MOVE.B data,d1  | 00 01 001 000 111 001 | 1239 00002000 |

| MOVE<br>Operation:  | Move Data From Source to Destination MOVE<br>(Source)→Destination                                                       | Des                   |           |                             | — Specifies the desti<br>re allowed as shown: | nation lo | cation. Only data           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|-----------------------------|-----------------------------------------------|-----------|-----------------------------|

| Assembler           |                                                                                                                         | Addressing Mode       | Mode      | Register                    | Addressing Mode                               | Mode      | Register                    |

| Assembler<br>Syntax | MOYE (ea),(ea)                                                                                                          | Dn                    | 000       | register number             | d(An,Xi)                                      | 110       | register number             |

| <b>Upina</b>        | mone tear, tear                                                                                                         | An                    | —         | _                           | Abs.W                                         | 111       | 000                         |

| Attributes:         | Size=(Byte,Word,Long)                                                                                                   | (An)                  | 010       | register number             | Absl                                          | 111       | 001                         |

|                     |                                                                                                                         | (An)+                 | 011       | register number             | d(PC)                                         | -         | —                           |

| Description:        | Move the content of the source to the destination location. The data is examined as it is                               | -(An)                 | 100       | register number             | d(PC,Xi)                                      | -         | —                           |

|                     | moved, and the condition codes set accordingly. The size of the operation may be<br>specified to be byte, word or long. | d(An)                 | 101       | register number             | lmm                                           | -         | —                           |

| Condition Cod       |                                                                                                                         |                       |           | as shown:                   |                                               |           | De sistera                  |

|                     |                                                                                                                         | Lidden a de a Marida  | Mode      | De sistere                  | Lidden and a shift of a                       | Mode      | De sisters                  |

|                     | N Set if the result is negative. Cleared otherwise.                                                                     | Addressing Mode<br>Dn | 000       | Register<br>register number | Addressing Mode<br>d(An,Xi)                   | 110       | Register<br>register number |

|                     | Z Set if the result is zero. Cleared otherwise.                                                                         | Án*                   | 000       | register number             | Abs.W                                         | 111       | 000                         |

|                     | Y Always cleared.                                                                                                       | (An)                  | 010       | register number             | AbsL                                          | 111       | 001                         |

|                     | C Always cleared.                                                                                                       | (An)+                 | 010       | register number             | d(PC)                                         | 111       | 010                         |

|                     | X Notalfected.                                                                                                          | - (An)                | 100       | register number             | d(PC,Xi)                                      | 111       | 011                         |

| Instruction Fo      | - at                                                                                                                    | d(An)                 | 101       | register number             |                                               | 111       | 100                         |

|                     | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                                                   | * For byte size opera | ion, addr | ess register direct is r    | not allowed.                                  |           |                             |

- 11 10 word operation. long operation. Ξ

| Addressing Mode | Mode | Register        |  | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|--|-----------------|------|-----------------|

| Dn              | 000  | register number |  | d(An,Xi)        | 110  | register number |

| An              |      | —               |  | Abs.W           | 111  | 000             |

| (An)            | 010  | register number |  | AbsL            | 111  | 001             |

| (An)+           | 011  | register number |  | d(PC)           | -    | Ι               |

| -(An)           | 100  | register number |  | d(PC,Xi)        | _    | -               |

| d(An)           | 101  | register number |  | Imm             | —    | -               |

|                 |      |                 |  |                 |      |                 |

sing modes are

| Addressing Mode | Mode | Register        |  | Addressing Mode | Mode | Register        |

|-----------------|------|-----------------|--|-----------------|------|-----------------|

| Dn              | 000  | register number |  | d(An,Xi)        | 110  | register number |

| An*             | 001  | register number |  | Abs.W           | 111  | 000             |

| (An)            | 010  | register number |  | AbsL            | 111  | 001             |

| (An)+           | 011  | register number |  | d(PC)           | 111  | 010             |

| -(An)           | 100  | register number |  | d(PC,Xi)        | 111  | 011             |

| d(An)           | 101  | register number |  | Imm             | 111  | 100             |

Microprocessor-based System Design Ricardo Gutierrez-Osuna Wright State University

# Memory organization example

|                    | Memory<br>address |              |           | <ul> <li>Since the data bus is 16-bit wide,</li> <li>it makes sense to visualize</li> <li>memory in blocks of 16 bits</li> </ul> |

|--------------------|-------------------|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------|

|                    | \$000000          | Byte0        | Byte1     |                                                                                                                                  |

|                    | \$000002          | Byte2        | Byte3     |                                                                                                                                  |

|                    | \$000004          | Byte4        | Byte5     |                                                                                                                                  |

|                    | \$000000          | Word0 MSB    | Word0 LSB |                                                                                                                                  |

|                    | \$000002          | Word1 MSB    | Word1 LSB |                                                                                                                                  |

|                    | \$000004          | Word2 MSB    | Word2 LSB |                                                                                                                                  |

|                    | \$000006          | Word3 MSB    | Word3 LSB |                                                                                                                                  |

| MOVE \$3210, 0     | \$000000          | 32           | 10        |                                                                                                                                  |

|                    | \$000000          | Longword     | 10 (MSW)  |                                                                                                                                  |

|                    | \$000002          | Longwore     |           |                                                                                                                                  |

|                    | \$000004          |              | 1 1 (MSW) |                                                                                                                                  |

|                    | \$000006          | ······₩····· | d 1 (LSW) |                                                                                                                                  |

| MOVE \$76543210, 0 | \$000000          | 76           | 54        |                                                                                                                                  |

| толе 21024277° О   | \$000002          | 32           | 10        |                                                                                                                                  |