# ECEN474: (Analog) VLSI Circuit Design Fall 2011

Lecture 5: MOS Transistor Modeling

Sebastian Hoyos Analog & Mixed-Signal Center Texas A&M University

#### Announcements

- Lab 1 this week

- Reading for next time

- Razavi's CMOS book chapter 16

## Agenda

- Threshold voltage dependencies on W,L

- Temperature dependencies

- Process corners

- Technology characterization for design

- Adapted from Prof. B. Murmann (Stanford) notes

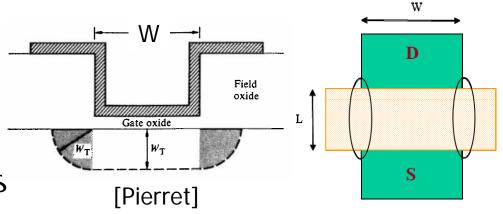

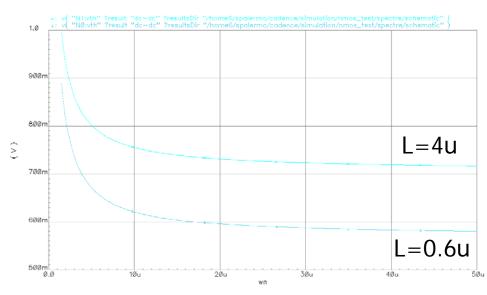

# V<sub>T</sub> Dependency on W

Gate-controlled depletion region extends in part outside the gate width

V<sub>T</sub> monotonically increases with decreasing channel width

$$\begin{aligned} V_T &= V_{Twide} + \Delta V_T \\ \Delta V_T &= \frac{q N_A W_T}{C_{or}} \frac{\pi W_T}{2W} \end{aligned}$$

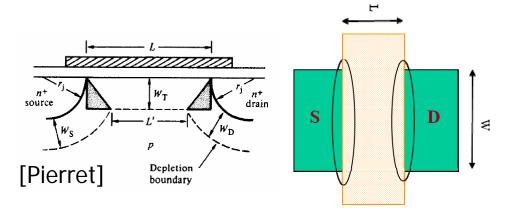

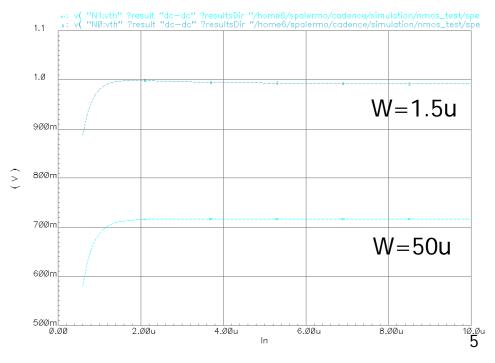

# V<sub>T</sub> Dependency on L

- Source and drain assist in forming the depletion region under the gate

- With simple model, V<sub>T</sub> monotonically decreases with decreasing channel length

$$V_T = V_{Tlong} + \Delta V_T$$

$$\Delta V_T = -\frac{qN_AW_T}{C_{ox}}\frac{r_j}{L}\left(\sqrt{1 + \frac{2W_T}{r_j}} - 1\right)$$

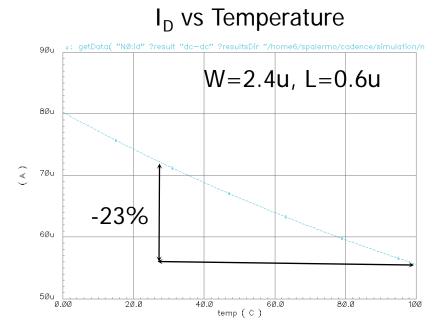

## Temperature Dependence

- Transistor mobility and threshold voltage are dependent on temperature

- Mobility ∞T<sup>-3/2</sup> due to increased scattering

- Threshold voltage decreases with temperature due to reduced bandgap energy  $E_g = 1.16 \frac{7.02 \times 10^{-4} T^2}{T + 1108}$

$\mu = \mu_0 \left(\frac{300}{T}\right)^{3/2}$

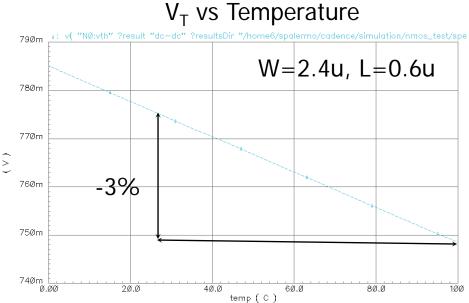

#### **Process Corners**

- Substantial process variations can exist from wafer to wafer and lot to lot

- Device characteristics are guaranteed to lie in a performance envelope

- To guarantee circuit yield, designers simulate over the "corners" of this envelope

- Example: Slow Corner

- Thicker oxide (high  $V_T$ , low  $C_{ox}$ ), low  $\mu$ , high  $R_{\Box}$

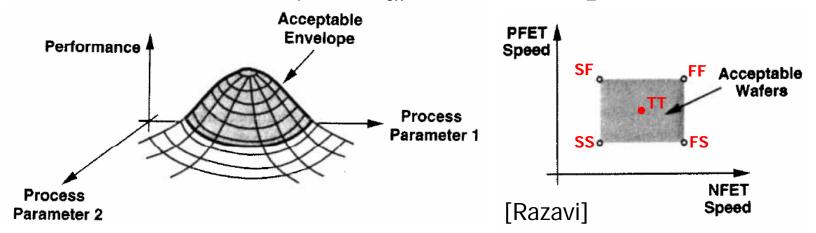

# Inverter Delay Variation with Process & Temperature

CMOS inverter delay varies close to ±40% over process and temperature

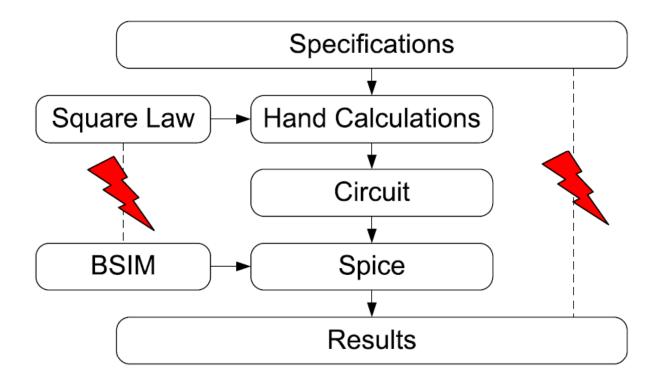

# How to Design with Modern Sub-Micron (Nanometer) Transistors?

- Hand calculations with square-law model can deviate significantly from actual device performance

- However, advanced model equations are too tedious for design

- Tempts designers to dive straight to simulation with little understanding on circuit performance trade-offs

- "Spice Monkey" approach

- How can we accurately design when hand analysis models are way off?

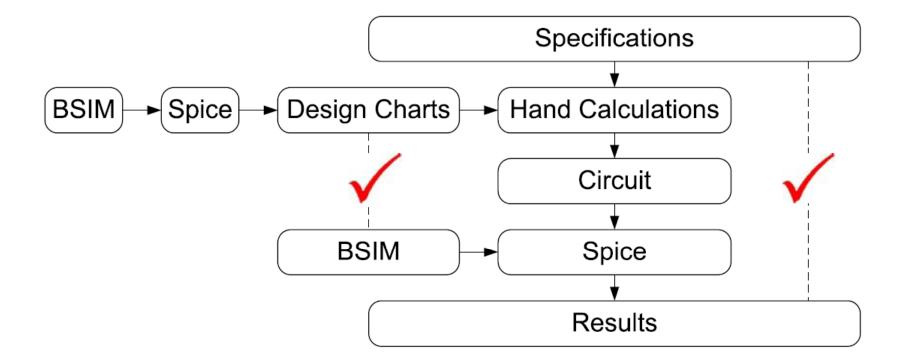

- Employ a design methodology which leverages characterization data from BSIM simulations

## The Problem

[Murmann]

#### The Solution

[Murmann]

# Device Figures of Merit

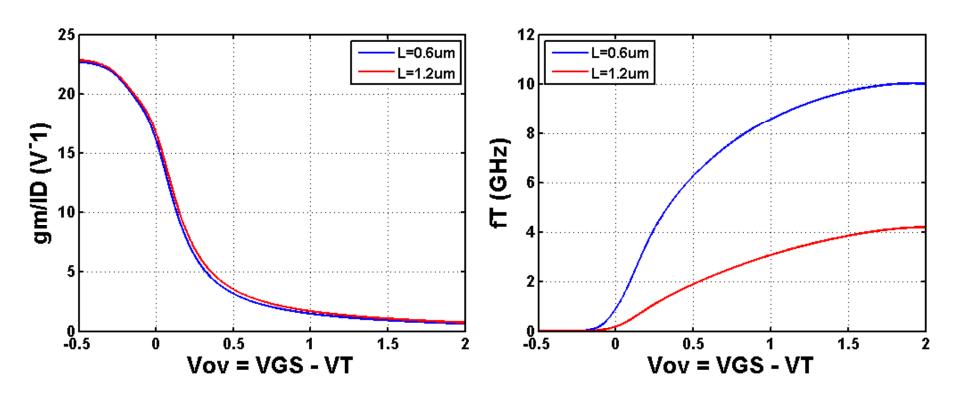

#### Transconductance efficiency

• Want maximum g<sub>m</sub> for minimum current

#### Square-Law

$$\frac{g_m}{I_D} = \frac{2}{V_{OV}}$$

$$V_{OV} = V_{GS} - V_T$$

- Transit frequency, f<sub>T</sub>

- Want maximum g<sub>m</sub> for minimum C<sub>qq</sub>

- $C_{gg} = total \ gate \ cap = C_{gs} + C_{gd} + C_{gb}$

$$\omega_{T} = \frac{g_{m}}{C_{gg}} \cong \frac{3}{2} \frac{\mu V_{OV}}{L^{2}}$$

assuming  $C_{gg} = C_{gs}$  only

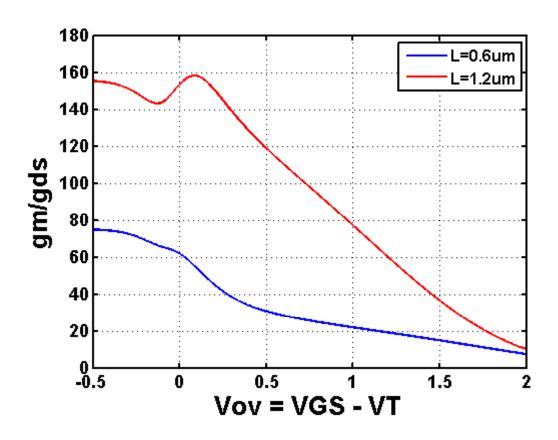

- Intrinsic gain

- Want maximum  $g_m/g_{ds}=g_m r_o$

$$\frac{g_m}{g_{ds}} \cong \frac{2}{\lambda V_{OV}}$$

## Technology Characterization for Design

- Generate data for the following over a reasonable range of g<sub>m</sub>/I<sub>D</sub> and channel lengths

- Transit frequency (f<sub>T</sub>)

- Intrinsic gain (g<sub>m</sub>/g<sub>ds</sub>)

- Current density (I<sub>D</sub>/W)

- Also useful is extrinsic capacitor ratios

- C<sub>gd</sub>/C<sub>gg</sub> and C<sub>dd</sub>/C<sub>gg</sub>

- Parameters are (to first order) independent of transistor width, which enables "normalized design"

- Do design hand calculations using the generated technology data

- Still need to understand how the circuit operates for an efficient design!!!

## Our 0.6um Technology Simulation Data

#### NMOS W=2.4um

## Our 0.6um Technology Simulation Data

#### NMOS W=2.4um

## Next Time

Layout Techniques