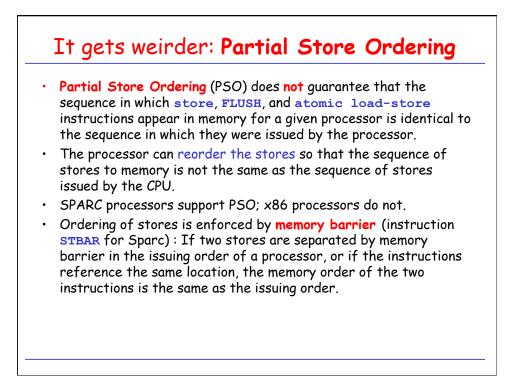

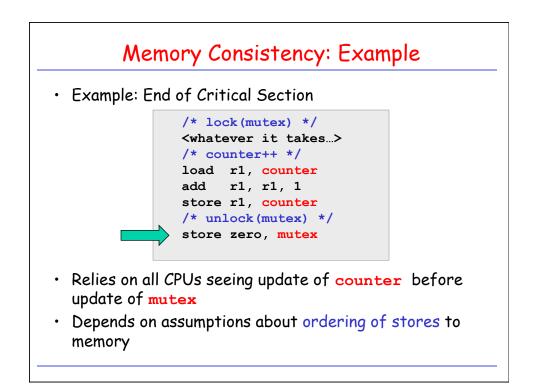

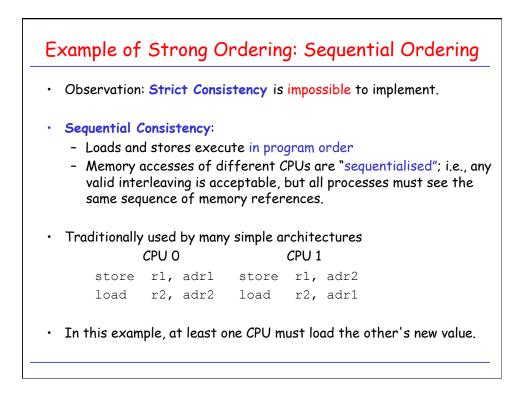

| Example:                      |                                                |           |         |           |       |         |

|-------------------------------|------------------------------------------------|-----------|---------|-----------|-------|---------|

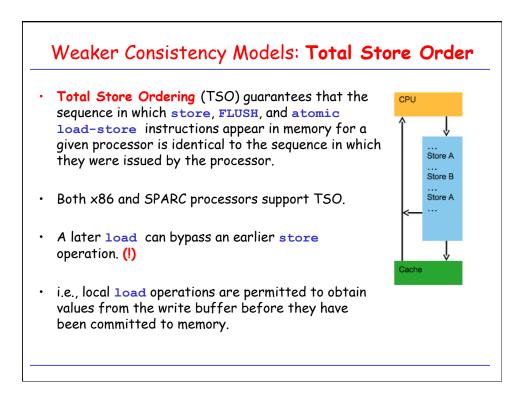

| CPU 0                         |                                                | CPU 1     |         |           | CPU   |         |

| store                         | rl, adrl                                       | store     | r1, a   | adr2      | Î     | Ŷ       |

| load                          | r2, adr2                                       | load      | r2, a   | adr1      |       | Store A |

| Both CPUs may read old value! |                                                |           |         |           |       | Store B |

|                               | a <mark>re support</mark> to<br>structions, su |           | bal ord | lering of | <     | Store A |

| - atomic sv                   | vap                                            |           |         |           |       | - 1     |

| - test & se                   | it i                                           |           |         |           | Cache | Ŷ       |

| - load-linke                  | ed + store-cor                                 | nditional |         |           |       |         |

|                               |                                                |           |         |           |       |         |